входы которого подключены к другим выходам второго коммутатора, седьмой выход блока управления соединен с управляющим входом второго блока сравнения, выходы с восьмого по десятый подключены к управляющим входам третьего регистра, а одиннадцатый выход .Соединен с первым входом первого регистра, второй вход которого, третий вход второго регистра и прямой вход триггера подключены к второму выходу формирователя управляющих сигналов, двенадцатый выход блока управления соединен с первым управляющим входом первого коммутатора, второй управляющий вход которого подключен к выходу третьего элемента И, первый вход которого соединен с тринадцатым выходом блока управления, а второй вход объединен с вторыми входами второго элемента И, элемента ИЛИ-НЕ, второй вход второго элемента И и вход формирователя управляющих сигналов являются другими управляющими входами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1244726A1 |

| Запоминающее устройство | 1979 |

|

SU849301A1 |

| Логическое запоминающее устройство | 1977 |

|

SU661609A1 |

| Устройство для коррекции ошибок в блоках памяти | 1985 |

|

SU1257708A1 |

| Запоминающее устройство | 1983 |

|

SU1116458A1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| Устройство для контроля записи информации в блоках памяти | 1982 |

|

SU1076954A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1401447A1 |

| Устройство управления доступом к памяти для обмена массивами данных в многопроцессорной системе | 1989 |

|

SU1633418A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С АВТОНОМНЫМ КОНТРОЛЕМ, содержащее накопитель данных, формирователь адресных сигналов, входы которого являются адресными входами устройства, а выходы соединены с адресными входами накопителя данных, формирователь, чис.повых сигналов, одни из входов и выходов которого являются информационными входа.ми и выходами устройства, дешифратор, входы которого являются одними из управляющих входов устройства, триггер, первый элемент И, блок управления, отличающееся тем, что, с целью повышения надежности устройства, в него введены второй и третий элементы И, элемент ИЛИ, элемент ИЛИ-НЕ, блоки сравнения, коммутаторы, регистры, формирователь контрольных кодов, блок индикации. формирователь синхроимпульсов и формирователь управляющих сигналов, вход которого соединен с первым входом формирователя синхроимпульсов, а первый выход соединен с инверсным входом триггера, прямой которого подключен к второму входу формирователя синхроимпульсов, выходы которого соединены с входами с первого по четверть й блока упг)ав.. пятый и шестой входы которого подключены соответственно к выходу псрр.ого б,

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может бьггь применено в микропроцессорных системах управления.

запоминающее устройство с самокоитролем, в котором для контроля работы устройства применяют метод подсчета KOHjpcxHbHbix сумм, при котором содержимое каждой из ячеек памяти поочередно дважды складывают поразрядно с полностью единичным словом i.

Недостатком этого устройства является низкая надежность.

Наиболее б.шзким к предлагаемому является заио.мииающее устройство с самоконтролем, содержащее блок .местного управления, процессор, регистр микрокоманд, первый и второй паянные формирователи, соединенные с соответствующими входами оперативного накопителя, постоянный накоГ1ите.ль .микрокоманд, дешифратор сигналов унравления, генератор тактовых импульсов, триггер управления генератором и элемент И, причем адресные шины и шины данных оперативного накопителя соединены с шинными формирователя.ми, а первый и второй управляющие входы накопителя соединены с пыходоу, регист|5а микрокоманд, другие выводы Н1ИННЫХ формирователей соединены с соответствующими входами и выходами npoiieccopa 2.

Недостатком прототипа является низкая надежность, поскольку не предусмотрен контроль во время функционирования устройства и требуется периодически отключать накопитель для проведения профилактическо о функционального контроля.

Цель изобретения - повышение надежности устройства.

Поставленна цель достигается те.м, что в запоминающее устройство с автономным контролем, содержащее накопитель данных, формирователь адресных сигналов, входы которого являются адресными входами устройства, а выходы соеди)1ены с адресными

входами накопителя данных, формирователь числовых сигналов, одни из входов и выходов которого являются информационными входами и выходами устройства, дешифратор, входы которого являются одними из управляющих входов устройства, триггер, первый элемент И и блок управления, введены второй и третий элементы И, элемент ИЛИ, элемент ИЛИ - НЕ, блоки сравнения, коммутаторы, регистры, формирователь контрольных кодов, блок индикации, формирователь синхроимпульсов и формирователь управляющих сигналов, вход которого соединен с первым входом формирователя синхроимпульсов, а первый выход соединен с инверсным входом триггера, прямой выход ко5торого подключен к второму входу фор.мирователя синхроимпульсов, выходы которого соединены с входами с первого по четвертый блока управления, пятый и шестой входы которого подключены соответственно к выходу

0 первого блока сравнения и первому входу э.пемента ИЛИ-НЕ и к выходу второго блока сравнения, одни из входов которого и одни из входов первого коммутатора соединены с выходами формирователя контрольных ко5дов, входы которого подключены к выходам первого регистра и группе входов блока управления, первый и второй выходы которого соединены соответственно с первыми входами первого и второго элементов И, а третий и четвертый выходы подключены соот0ветственно к первому входу второго регистра и к второму входу второго регистра и управляющему входу первого блока сравнения, одни из входов которого подключены к одним из выходов второго регистра и входам блока индикации, управляющий вход кото5рого соединен с пятым выходом блока управления, шестой выход которого подключен к первым управляющим входам второго коммутатора, второй управляющий вход которого соединен с выходом первого блока

0 сравнения, другие входы которого подключены к другим выходам второго регистра и

адресным входам накопителя данных, первый управляющий вход которого соединен с выходом нервого элемента И, второй вход которого подключен к выходу элемента ИЛИ, первый и второй входы которого соединены соответственно с выходом элемента ИЛИ-НЕ и с выходом дешифратора и седьмым входом блока управления, восьмой вход которого подключен к выходу второго элемента И и второму управляющему входу накопителя данных, информационные входы и выходы которого соединены соответственно с выходами первого коммутатора, с одними из входов второго коммутатора, другими входами второго блока сравнения и входами третьего регистра, выходы которого подключены к другим входам второго коммутатора, причем другие входы первого ком:. -;;тора соединены соответственно с одними из выходов второго коммутатора и с дру|иу.и выходами формирователя числовых ciii па/юв, другие входы которого подключены к другим выходам второго коммутатора, седьмой выход блока управления соединен с управляющим входом второго блока сравнения, выходы с восьмого по десятый подключены к управляющим входам третьего регистра, а одиннадцатый выход соединен с первым входом первого регистра, второй вход которого, третий вход второго регистра и прямой вход триггера подключены к второму выходу формирователя управляющих сигналов, двенадцатый выход блока управления соединен с первым управляющим входом первого коммутатора, второй управляющий вход которого подключен к выходу третьего элемента И, первый вход которого соединен с тринадцатым выходом блока управления, а второй вход объединен с вторыми входами второго элемента И, элемента ИЛИ-НЕ, второй вход второго элемента И и вход формирователя управляющих сигналов являются другими управляющимт входами устройства.

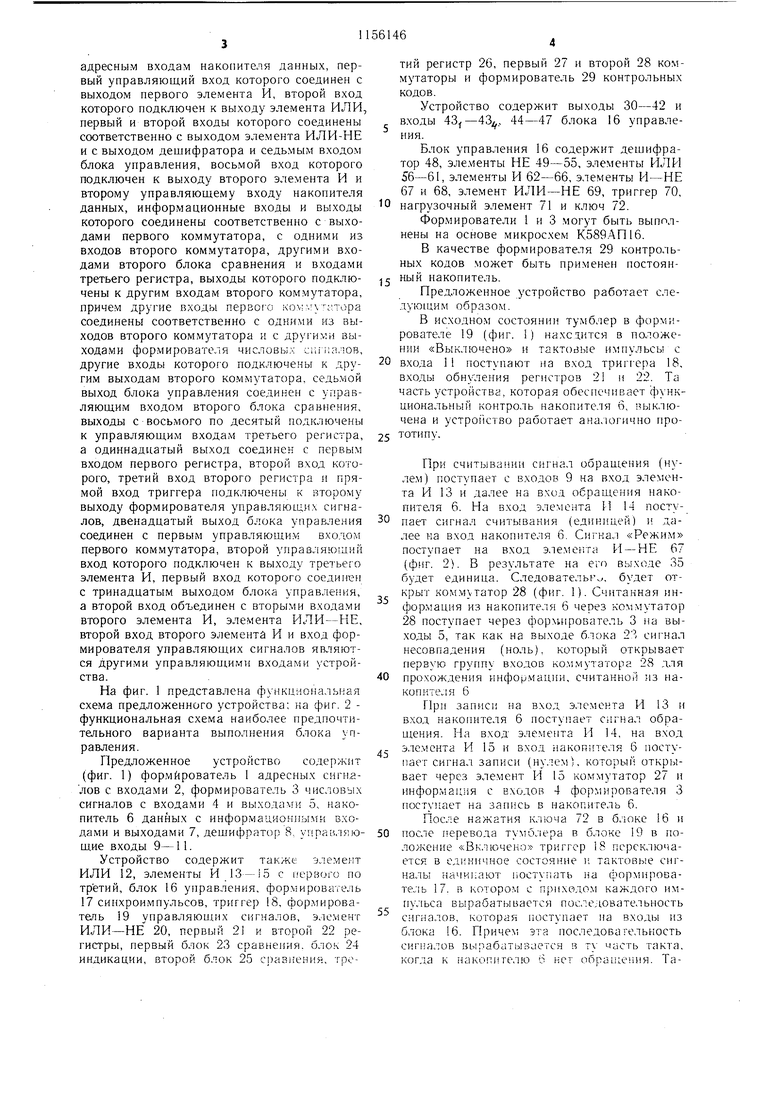

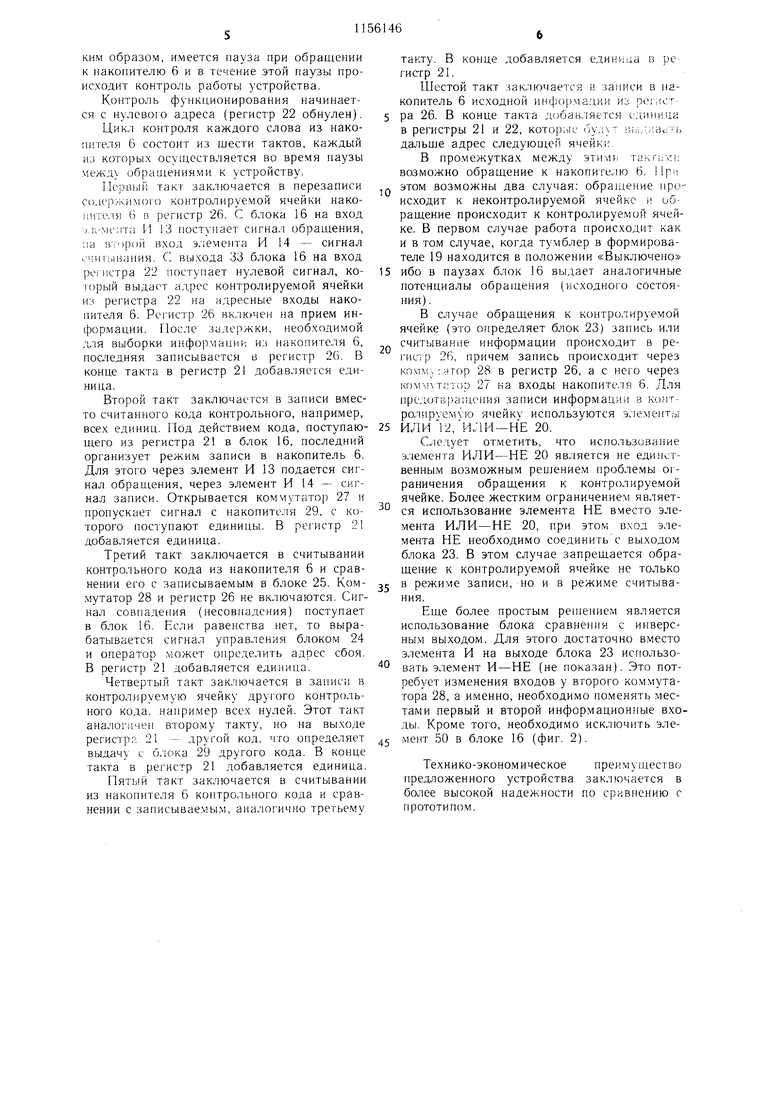

На фиг. 1 представлена функциональная схема предложенного устройства: на фиг. 2 функциональная схема наиболее предпочтительного варианта выполнения блока управления.

Предложенное устройство содержит (фиг. Г) формирователь 1 адресных сигналов с входами 2, формирователь 3 числовых сигналов с входа.ми 4 и выхода гк 5, накопитель 6 данных с информацион 1ым.ч входами и выходами 7, дешифратор 8, управляющие входы 9-11.

Устройство содержит также элемент ИЛИ 12, элементы И 13-15 с первого по третий, блок 16 управления, формирователь 17 синхроимпульсов, триггер 18, форл1ирователь 19 управляюпдих сигналов, элемент ИЛИ-НЕ 20, первый 21 и второй 22 регистры, первый блок 23 сравнения, бло.к 24 индикации, второй блок 25 сг), третий регистр 26, первый 27 и второй 28 коммутаторы и формирователь 29 контрольных кодов.

Устройство содержит выходы 30-42 и входы 43j-43/, 44-47 блока 16 управления.

Блок управления 16 содержит дешифратор 48, элементы НЕ 49-55, элементы ИЛИ 56-61, элементы И 62-66, элементы И-НЕ 67 и 68, элемент ИЛИ-НЕ 69, триггер 70, нагрузочный элемент 71 и ключ 72.

Формирователи 1 и 3 могут быть выполнены на основе микросхем К589АП16.

В качестве формирователя 29 контрольных кодов может быть применен постоянныи накопитель.

Предложенное устройство работает следующим образом.

В исходном состоянии тумблер в формирователе 19 (фиг. 1) нахса,нтся в положении «Выключено и тактовые импульсы с

0 входа 11 поступают на вход триггера 18, входы обнуления регистров 21 и 22. Та часть устройства, которая обеспечивает функциональный контроль накопителя 6, выключена и ycTpoiicTBO работает аналогично прототипу.

При считывании сигнал обращения (нулем) поступает с входов 9 на вход элемента И 13 и далее на вход обращения накопитетя 6. На вход элеме11та И 14 поступает сигнал считывания (ед1 ницей) и далее на вход накопителя 6. Сигнал «Режим поступает на вход эле.мепта И - НЕ 67 (ф.иг. 2). В результате на его выходе 35 будет единица. Следовательго. будет открыт комм татор 28 (фиг. 1). Считанная информация из накопителя 6 через коммутатор 28 поступает через формирователь 3 на выходы 5, так как на выходе блока 2, сигнал несовпадения (ноль), который открывает первую группу входов ко.ммутаторг 28 для

прохождения информации, считанной яз накопителя 6

При записи на вход элемента И 13 и ВХО.Л, накопителя 6 поступает сигнал обращения. На вход элемента И 14, на вход элемента И 15 и вход накопителя 6 поступает сигнал записи (нулем), который открывает через элемент И 15 коммутатор 27 и информация с входов 4 фор.мирователя 3 поступает на запись в накопитель 6.

После нажатия ключа 72 в блоке 16 и

0 после перевода тумблера в блоке 19 в положение «Включено триггер 18 переключается в ед11ничное состояние и тактовые сигналы начинают гюступать ь:а формирователь 17, в котором с приходо.м каждого импульса вырабатывается последовательность

сигналов, которая iiocTyriaeT на входы из блока 16. Причем эта последовгггельность сигналов вырабатывается в ту часть такта, когда к накоп11те,тю 6 кет обпащения. ТаКИМ образом, имеется пауза при обращении к накопителю бив течение этой паузы происходит контроль работы устройства.

Контроль функционирования начинается с нулевого адреса (регистр 22 обнулен).

Цикл контроля каждого слова из накопителя 6 состоит из шести тактов, каждый из которы.х осуществляется во время паузы между обраихениями к устройству.

Первый такт заключается в перезаписи солержимого контролируемой ячейки накоliHTe.ii- 6 в регистр 26. С блока 16 на вход ,м-;-мг;гга 1-1 13 поступает сигнал обращения, на вход з.:;емента И 14 - сигнал . чиг;,1вапия. с вы.хода 33 блока 16 на вход poi истра 22 поступает нулевой сигнал, который выдает адрес контролируемой ячейки из регистра 22 на адресные входы накопителя 6. Регистр 26 включен на прием информации. После задержки, необходи.мой для выборки информации из накопителя 6, носледняя записывается в регистр 26. В конце такта в регистр 21 добавляется единица.

Второй такт заключается в записи вместо считанного кода контрольного, например, всех единиц. Под действием кода, поступающего из регистра 2 в блок 16, последний организует режим записи в накопитель 6. Для этого через элемент И 13 подается сигнал обращения, через элемент И 14 - сигнал записи. Открывается коммутатор 27 и пропускает сигнал с накопителя 29, с которого поступают единицы. В регистр 21 добавляется единица.

Третий такт заключается в считывании контрольного кода из накопителя 6 и сравнении его с записываемым в блоке 25. Коммутатор 28 и регистр 26 не включаются. Сигнал совпадения (несовпадения) поступает в блок 16. Если равенства нет, то вырабатывается сигнал управления блоком 24 и оператор может определить адрес сбоя. В регистр 21 добавляется единица.

Четвертый такт заключается в записи в контролируемую ячейку другого контрольного кода, например всех нулей. Этот такт аналогичен второму такту, но на выходе регистр;- 21 - другой код, что определяет выдачу с блока 29 другого кода. В конце такта в регистр 21 добавляется единица.

Пятый такт заключается в считывании из накопителя 6 контрольного кода и сравнении е записываемым, аналогично третьему

такту. В конце добавляется едини:1а в ре гистр 21.

Шестой такт заключается к записи в накопитель 6 исходной информации из periicT5 pa 26. В конце такта добавляется единица в регистры 21 и 22, KOTO)iiFe ,-ивоп дальше адрес следующей ячейки:,

В про.межутках между этими та.кгами возможно обращение к накопителю 6. Пр;-:

Q этом возможны два случая: обращение происходит к неконтролируемой ячейке и обращение происходит к контролируемой ячейке. В первом случае работа происходит как и в том случае, когда тумблер в формирователе 19 находится в положении «Выключено

5 ибо в паузах блок 16 выдает аналогичные потенциалы обращения (исходного состояния) .

В случае обращения к контролируемой ячейке (это определяет блок 23) запись или считывание информации происходит в ре истр 26, причем запись происходит через ко.мму; гор 28 в регистр 26, а с него через комч т;::т()р 27 на входы накопителя 6. .Для предотБращ( записи информации в коятролир ем ю ячейку используются эле.мептп

5 ИЛИ l 2,илИ-НЕ 20.

Следует отметить, что использование элемента ИЛИ-НЕ 20 является не единственным возможным решением пробле.мы ограничения обращения к контролируемой ячейке. Более жестким ограничением является использование элемента НЕ вместо элемента ИЛИ-НЕ 20, при этом в.ход элемента НЕ необходимо соединить с выходом блока 23. В этом случае запрещается обращение к контролируемой ячейке не только

5 в режиме записи, но и в режиме считывания.

Еще более простым ре1пением является использование блока сравнения с инверсным выходом. Для этого достаточно вместо элемента И на выходе блока 23 использо0 вать элемент И-НЕ (не показан). Это потребует изменения входов у второго коммутатора 28, а именно, необходимо поменять местами первый и второй информацион.чые входы. Кроме того, необходимо исключить эле5 мент 50 в блоке 16 (фиг. 2).

Технико-экономическоепреи.мущество

предложенного устройствазаключается в

более высокой надежностипо сравнению с прототипом.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| «Электроника, 1979, „V2 24, с | |||

| Фальцовая черепица | 0 |

|

SU75A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Микропроцессорные комплекты интегральных схем (состав и структура) | |||

| Справочник гюд ред | |||

| А | |||

| А | |||

| Васенкова и В | |||

| .А | |||

| Шахнова | |||

| М., «Сов | |||

| радио, 1982, с | |||

| Деревянное стыковое скрепление | 1920 |

|

SU162A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Насос | 1917 |

|

SU13A1 |

Авторы

Даты

1985-05-15—Публикация

1984-01-30—Подача