прямому выходу формирователя импульсов, а вход сброса - к входу сброса четйертого триггера, установочный вход пятого триггера и первый вход первого элемента ИЛИ объединены и являются установочным входом устройства, второй вход первого элемента ИЛИ является другим управляющим входом устройства, выходы второго элемента ИЛИ и третьего элемента ИЛИ-НЕ и прямой выход пятого триггера являются другими управляющими выходами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля записи информации в блоках памяти | 1981 |

|

SU949720A1 |

| Система для обмена информацией | 1990 |

|

SU1815646A1 |

| Запоминающее устройство | 1983 |

|

SU1116458A1 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1156146A1 |

| Устройство для анализа вызванных потенциалов головного мозга | 1990 |

|

SU1804787A1 |

| Устройство для управления считыванием и вводом информации | 1990 |

|

SU1751786A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Устройство для сопряжения процессора с памятью | 1983 |

|

SU1149272A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УПРАВЛЯЮЩЕЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1995 |

|

RU2094842C1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЗАПИСИ ИНФОРМАЦИИ В БЛОКАХ НАМЯТИ, содержащее регистры адреса, накопитель, блок сравнения, первый и вто- . рой входы которого являются -соответственно информационным и контрольным входами устройства, триггеры и коммутатор, первый вход которого и вход первого регистра адреса объединены и являются адресным входом устройства, адресным выходом которого является выход первого регистра адреса, формирователь импульсов, первь)й элемент ИЛИ-НЕ, первый элемент НЕ и элемент. ИЛИ-И, причем выход первого регистра адреса соединен с вторым входом коммутатора, выход которого подключен к входу второго регистра адреса, выход которого соедимен с адресным входом накопителя, информационный вход которого подключен к вь1ходу первого триггера, информационный вход которого соединен с выходом блока сравнения, первый и второй управляющие входы коммутатора подключены соответственно к инверсному выходу второго триггера и к прямому выходу второготриггера, первому входу первого элемента ИЛИ-НЕ, установочному и информационному входам третьего триггера, вход синхронизации которого соединен с выходом первого элемента НЕ, а инверсный выход -г с управляющим входом формирователя импульсов, прямой выход которого подключен к первому управляющему входу накопителя и входу синхронизации четвертого триггера, прямой выход которого соединен с первым входом элемента ИЛИ-И, а инверсный выход -- с установочным входом первого триггера, вторым входом мервого элемента ИЛИ-НЕг и вторым входом элемента ИЛИ-И, выход которого подключен к входу первого эле.мента НЕ и BXO;KIM синхронизации регистров адреса, первого и второго триггеров н формирователя импульсов, третий и четвертый входы элемента ИЛИ-И и входы сброса второго и четвертого триггеров являются одними из управляющих входов устройства, прямой выход формирователя импульсов, инверсН1 1Й выход четвертого триггера и выходы второго триггера являются одними из управляющих выходов устройства, отличающееся тем, что, с целью повышения досто в верности контроля, в него введены пятый (Л триггер, элементы ИЛИ, второй и третий элементы ИЛИ-НЕ и второй элемент НЕ, причем первый вход и выход второго элемента ИЛИ-НЕ подключены соответстве)но к выходу первого триггера и к второму управляющему входу накопителя, выход первого элемента ИЛИ соединен с информационным входом второго триггера и установочным входом четвертого триггера, второй вход второго элемента ИЛИ-НЕ CD СО подключен к входу сброса первого триггера, первому входу второго элемента ИЛИ сд и прямому выходу пятого триггера, инверсный выход которого соединен с первым третьего элемента ИЛИ-НЕ, второй вход которого подк-пючен к выходу второго элемента НЕ, вход которого соединен с выходом накопителя, третий и четвертый входы третьего элемента ИЛИ-НЕ соединены соответственно с выходом элемента ИЛИИ и с инверсным выходом формирователя импульсов, второй вход второго элемента ИЛИ подключен к выходу первого элемента ИЛИ-НЕ, информационные входы четвертого и пятого триггеров соединены с прямым выходом третьего регистра, вход синхронизации пятого триггера подключен к

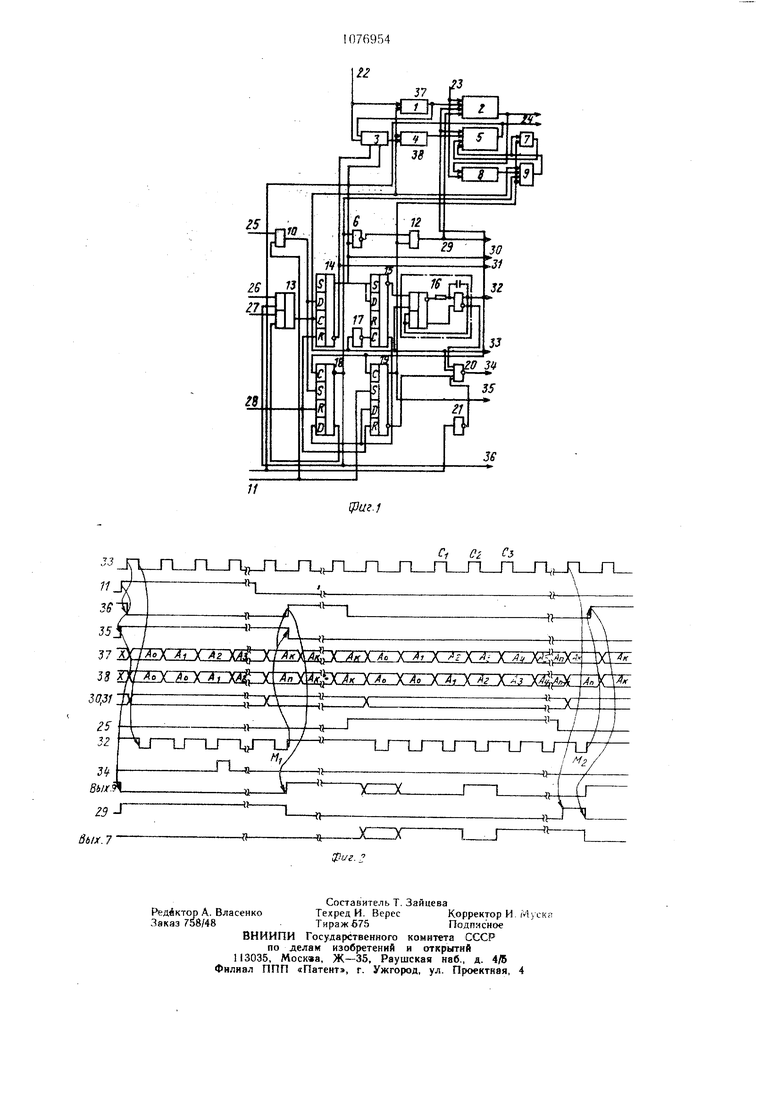

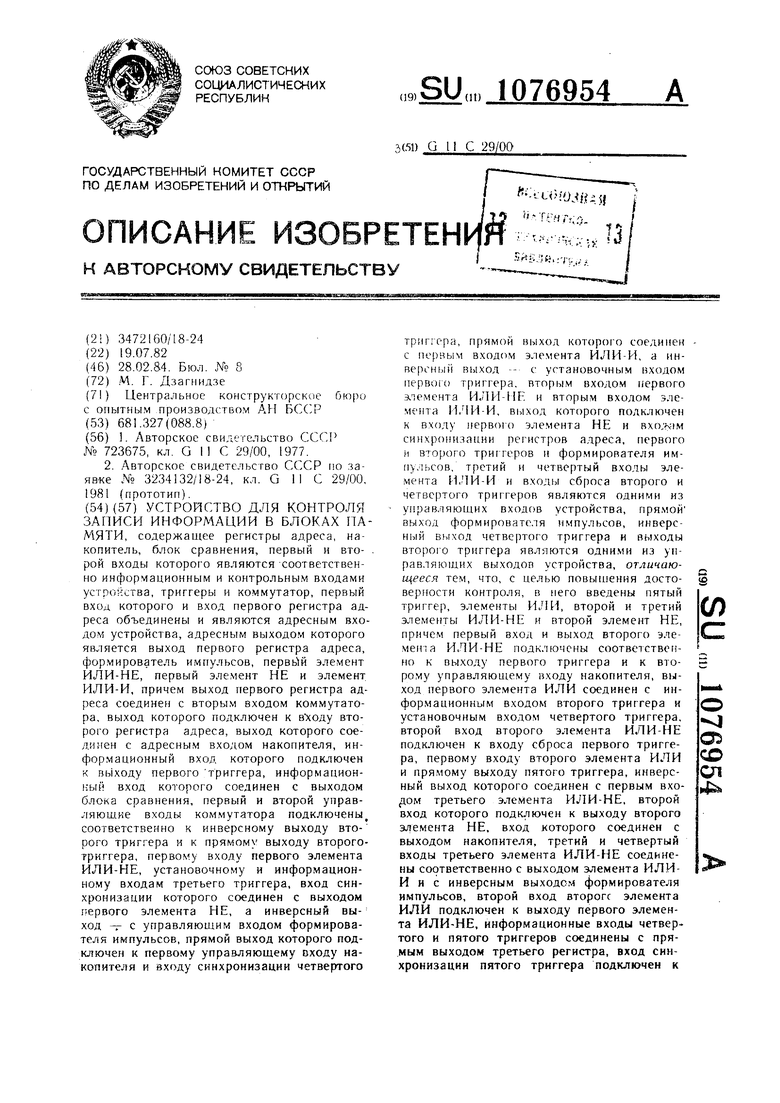

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам и может быть использовано для контроля оперативных запоминающих устройств в информационно-измерительных системах, когда запись информации в память производится синхронно с измерениями. Одно из известных устройств содержит формирователи интервала записи и конца считывания, элементы И и элементы ИЛИ, входы которых подключены соответственно к выходу формирователя записи и первого элемента И, а выход соединен с шиной «Запись и через последовательно включенные формирователи считывания и конца считывания с входом второго элемента И, другой вход которого соединен с выходом схемы сравнения, а выход - с первыми входами первого и третьего элементов И, вторые входы которых подключены соответственно к прямому и инверсному выходам формирователя интервала записи, вход которого соединен с выходом формирователя записи, причем третьего элемента И подключен к шине «Отказ 1. Недрстатками указанного устройства являются низкие быстродействие и достоверность контроля. Наиболее близким к предлагаемому является устройство для контроля 3anHqH инфЙрмации в блоках памяти, содержащее схему сравнения, входы которой являются информационным и контрольным входами устройства, основной регистр адреса и блок местного управления, входы которого являются управляющими входами устройства, дополнительный регистр адреса, коммутатор, накопитель и первый триггер, информационный вход которого подключен к выходу схемы сравнения, вход синхронизации соединен с входами синхронизации регистров адреса и выходом синхроимпульсов блока местного управления, выход первого триггера подключен к информационному вхо ду накопителя, адресный вход которого соединен с выходом дополнительного регистра адреса, информационный вход которого подключен к выходу коммутг гора, первый, второй, третий и четвертый входь; которого соединены соответственно с выходом и с адресным входом основного регистра адреса и с управляющими выходами блока местного управления, выход управления записью которого соединен с управляющим входом накопителя, выход которого является информационным выходом устройства 2. Недостатком известного устройства является низкая достоверность контроля определяемая вероятностью сбоя при записи результатов контроля в накопитель, так как в случае сбоя при записи информации в ОЗУ, Б накопитель записывается «1, а в случае отсутствия сбоя - «О. Цель изобретения - повыщение достоверности контроля. Поставленная цель достигается тем, что в устройство для контроля записи информации в блоках памяти, содержащее регистры адреса, накопитель, блок сравнения, первый и второй входы которого являются соответственно информационным и контрольным входами устройства, триггеры и коммутатор, первый вход которого и вход первого регистра адреса объединеHbi и являются адресным входом устройства, адресным выходом которого является выход первого регистра адреса, формирователь импульсов, первый элемент ИЛИ-НЕ, первый элемент НЕ и элемент ИЛИ-И, причем выход первого регистра адреса соединен с вторым входом коммутатора, выход которого подключен к входу второго регистра адреса, выход которого соединен с адресным входом накопителя, информационный вход которого подключен к выходу первого триггера, информационный вход которого соединен с выходом блока сравнения, первый и второй управляющие входы коммутатора подключены соответственно к инверсному выходу второго триггера и к прямому выходу второго триггера, первому входу первого элемента ИЛИ-НЕ, установочному и информационно му входам третьего триггера, вход синхронизации которого соединен с выходом первого элемента НЕ, а инверсный выход - с управляющим входом формирователя импульсов, прямой выход которого подключен к первому упрарзляющему входу накопителя и входу синхронизации четвертою триггера, ирямой выход которого соединен с первым входом элемента ИЛИ-НЕ, а инверсный выход - с установочным входом первого триггера, вторым входом первого элемента ИЛИ-НЕ и вторым входом элемента ИЛИ-И, выход которого подключен к входу первого элемента НЕ и входам синхронизации регистров адреса, первого и второго триггеров, и формирователя импульсов, третий и четвертый входы элемента ИЛИ-И и входы сброса второго и четвертого триггеров являются одними из управляющих входой устройства, прямой выход формирователя импульсов, инверсный выход четвертого триггера и выходы второго триггера являются одними из управляющих выходов устройства, введены пятый триггер, элементы ИЛИ, второй и третий элементы ИЛИ-НЕ и второй элемент НЕ, причем первый вход и выход второго э..;емента ИЛИ-НЕ подключены соогветственно . к выходу первого триггера и к второму управляющему рлоду накопителя, выход первого элемента ИЛИ соединен с итгформационным входом второго триггера и установочным входом четвертого триггера, второй вход второго элемента ИЛИ-НЕ подключен к входу сброса первого триггера, первому входу второго элемента ИЛИ и прямому выходу пятого триггера, инверсный выход которого соединен с первым входом третьего элемента ИЛИ-НЕ, второй вход которого подключен к выходу второго элемента НЕ, вход которого соединен с выходом накопителя, третий и четвертый входы третьего элемента ИЛИ-НЕ соединены соответственно с выходом элемента ИЛИИ и с инверсным выходом формирователя импульсов, второй вход второго элемента ИЛИ подключен к выходу первого элемента ИЛИ-НЕ, информационные входы четвертого и пятого триггеров соединены с прймым выходом третьего триггера, вход синхронизации пятого триггера подключен к прямому выходу формирователя импульсов, а вход сброса- к входу сброса четвертого триггера, установочный вход пятого триггера и первый вход первого элемента ИЛИ объединены и являются установочным входом устройства, второй вход первого элемента ИЛИ является другим управляющим входом устройства, выходы второго элемента ИЛИ и третьего элемента ИЛИ-НЕ и прямой выход пятого триггера являются другими управляющими выходами устройства. На фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2временная диаграмма, поясняющая его работу. Устройство содержит (фиг. U) первый регистр I .адреса, контролируемый блок 2 памяти (ОЗУ), коммутатор 3, второй регпстр 4 а.цюса, накопитс.пь 5, первый 6 и второй 7 элементы И.ЧИ-НЕ, блок 8 сравнения, первый триггер 9, первый элемент ИЛИ 10 с первым входом, II,.второй элемент ИЛИ 12, элемент ЙЛИ-И 13, .второй 14 и третий 15 триггеры, формирователь 16 импульсов, первый элемент НЕ 17. четвертый 18 и пятый 19 триггеры, третий элемент ИЛИ-НЕ 20 и второй элемент HF: 21. На фиг. 1 обозначены адресный 22 и информационный 23 входы устройства, выход 24 накопителя 5, управляющий вход 25 устройства, предназначенный для ввода сигналов режима записи, управляющие входы 26 и 27 устройства, предназначенные для ввода синхронмпульсов записи и считывания соответственно, управляющий вход 28, предназначенный для установки устройства при включении питания, управляющие выходы 29-31 устройства, предназначенные для вывода имnyjibcoB «Выбор кристалла ОЗУ и сигналов управления коммутатором 3 соответственно, управляющие выходы 32-34 устройотва, предназначенные для вывода импульсов «Запись, синхроимпульсов и иМпульсов «Отказ соответственно, управляюЬ5не выходы 35 и 36 устройства, предназначенные для вывода сигнала установки накопителя 5 и сигнала считывания соответственно и адресный выход 37 устройства и вход 38 накопителя 5. На фиг. 2 изображены синхроимпульсы на выходе 33 устройства, сигналы установки на входе II, импульсы считывания на выходе 36, сигналы установки накопителя 5 на выходе 35, АО-АП адреса на выходе 37 устройства (где п - целое число), адреса на входе 38 накопите-тя 5, «мпульсы управления коммутатором 3 на выходах 30 и 31 устройства, сигналы режима записи на входе 25 устройства, импульсы записи на выходе 32, импульсы «Отказ на выходе 34 устройства, сигналы на выходе триггера 9, сигнал «Выбор кристалла ОЗУ на выходе 29 устройства и сигнал на выходе элемента ИЛИНЕ 7. На фиг. 2 обозначены произвольные адреса А (где к - целое число), синхроимпульсы Cj, С, Сэ и импульсы М,, М записи. Накопитель 5 (фиг. 1) предназначен для запоминания результата сравнения кода, записанного в блок 2 памяти (ОЗУ) с кодом на входе блока 2 (в случае, если запись в блок 2 произведена с ощибкой, в накопитель 5 записывается «1). В качестве накопителя 5 используется микросхема К500РУ415. Коммутатор 3 предназначен для выбора источника адресов, поступивших в регистр 4, и позволяет записи осуществить формирование адреса для накопителя 5 на один синхроимпульс позже, чем для контролируемого ОЗУ. Предлагаемое устройство работает следующим образом. В режиме установки накопителя 5 на в.хол 11 (фиг. I) подается «1. При этом 19 устанав.жвается в единичное состояние, выключая через элемент И/1И 12 блок памяти сигналом на выходе 29 и «О со своего инверсного выхода, разрешая формирование импульса «Отказ на выходе 34 элементом И/1И-НЕ 20. Выключение блока 2 необходимо для предотвращения записи в него случайной информации. Далее, поступая с входа 11 на вход элемента ИЛИ 0, сигнал «Гежим установки .накопителя попадает на инфор.мационный вход триггера 14 и вход установки триггера 18, устанавливая триггер 18 в единимное состояние, причем сигналы с его выходов, поступая на входы элемента ИЛИ-И 13, открывают вход 26 (синхроимпульсы записи) и закрывают вход 27 (синхроимпульсы считывания). На выходе 35 появляется «1 с прямого выхода триггера 19. которая поступает на вход элемента ИЛИНГ: 7 и на вход сброса триггера 9. В результате накопитель 5 включается «О с выхода элемента ИЛИ-НЕ 7, а на информационном входе накопителя 5 появляется «О с выхода триггера 9. Затем на вход 26 подаются синхроимпульсы записи, а на вход 22 адреса, по которы.м производится запись в режиме записи. При этом к выбранную часть ячеек накопителя 5 заГ|ись ваются «О. Состояние коммутатора 3 акое же, как и в режиме записи, описанием ниже, поэтому адреса накопителя 5 смещены относительно адресов, подаваемых на вход 22 устройства. В связи с этим в конце режима установки накопителя 5 необходимо подать на вход 26 дополнительный синхроимпульс после того, как импульс ка входе 11 будет снят. При этом на входе 22 может присутствовать произвольный адрес АК (фиг. 2). По фронту дополнительного синхронмпул ;са триггер и, на информационном входе которого после снятия импульса на входе 11 по;1внтся «о, переключится в нулевое состояние. По спаду .цополнительного синхроимпульса триггер 15 переключается в нуле:joe состояние, запретив сигналом со своего .jHsepcHoro выхода работу формирователя б, однако на его выходе импульс лаписи /спеет сф ормироваться еще один раз ;MI на фиг. 2) из-за задержки запрещаю;uero сигнала с инверсного выхода триггера 15 относительно спада синхроимпульса на входе синхронизации формирователя 16, По концу последнего импульса записи в режиме установки накопителя 5 триггеры 8 и 19 устанавливаются в нулевое состояние и на .этом режим установки накопителя 5 оканчивается, о чем сообихается снятием : -;гкалз «Установка накопителя на выходе 35 и установкой сигнала «Считывание на ны.ходе 36. Блок 2 пя.мякч н.клн)ч; е-ц-н «О с выхода 29 элемента ИЛИ 12. :1,:и во время уст;ию ки нако11иге;1я 5 произойдет сбой, то есть вместо «{) и накопитель 5 запишется «1, и на выходе 34 появится короткий положительный и.мпульс, о которому можно, например, прои.чвести повторную saiiHCb по данному адресу. В результате установки накопителя 5 в те его ячейп. которые имеют такие же адреса, какие будут иметь ячейки блока 2 в режие записи, записываются «П. Таким образо.м, ещеДО режима записи нак(Л1:и 1ель 5 содержит информацию, соответствующую отсутствию сбоев в блоке 2 па.мяги. В режиме записи на вход 25 подастся «1. При этом устройство работает так же, как и в режиме «Установка накопителя, но триггер 19 не устанавливается в единичное состояние и., следовательно, блок 2 не выключается импульсом iia выход 29, а на яыходе 35 не появляется «1. поэтому три1тер 9 получает возможность переключения в единичное состояние, а накопитель 5 не включается «О с выхода элемента ИЛИ-НЕ 7, на обоих входах которого присутствуют «О. Ком.мутатор 3, управляемый выходами триггера 14, подключает niubopмациор ный вход регистра 4 к выходу регистра 1, поэтому адреса для накопителя 5 формируются с задержкой на один синхроимпульс относительно адресов блока 2 (фиг. 2), однако из-за задержки переключения триггера 4 первый адрес (А па фиг. 2) успеет записаться в оба регистра 1 и 4, что предотвратит запись информации в накопитель 5 по первому синхроимпульсу записи по случайному адресу. Как видно из фиг. 2, адреса накопителя 5 и блока памяти формируются по фронту синхроимпульсов записи. По спаду формируются импульсы записи. Так как эти импульсы оканчиваются до прихода следующего синхроимпульса не позже, чем за су.ммарное время задержки фронта на входе синхронизации триггера 9 бтНосительно .момента появления информации на его информационном входе, вре.мени восстановления блока 2 после записи и времени задержки в блоке 8, блок 2 успевает перейти в состояние «Считывание, а блок 8 сравнить появившийся на выходе блока 2 за/исан5 ый код с ксдом на его входе 23 (информация на входе 23 изменяется по фронту синхроимпульса записи), рая.ыме, че.м за время, равное задеряске фр01па импу- ьса на входе ci: ;лпонм:-ацип триггера 9 относительно импульса :,j С: с :иф ::;: Г.ИОППСМ входе до приходр U-f; си г рпимпульса записи. Результат ир.в - :;пчя с выхода блока 8 попадас; инфср.1&.аионный вход триггера 9 и язпэпи- ается там по фронту синх,роимпульса запнск. Если запйсач;Ьй и считанный колы одинаковы, тс на выходе: блока 8 появляется «О н триггер 9 не тменяет своего состояния. Если же при записи произойдет сбой, т. е. коды на входе 23 и на В1 1ходе блока 2 при контрольном считывании оказываются разными (фиг. 2, Aj в режиме записи, синхроимпульсы Ci и Cj), то па выходе блока 8 появится «1 и по фронту следующего синхроимпульса триггер 9 установится в единичное состояние. Логическая «1 с выхода триггера 9, пройдя через элемент ИЛИ-НЕ 7, включает накопитель 5. По фронту этого же синхроUMnVHKra i nu U Y ППимП /nu/ Рл UQ /f IjrO импульса (синхроимпульс С на фиг. 2) на адресном входе накопителя 5 формирует ся адрес, при записи по которому в блоке 2 есть сбой (А), а по спаду - очередной импульс записи, по которому в накопитель 5 с выхода триггера 9 записывается :1. По следующему синхроимпульсу Сз,, если при записи в блок 2 по синхроимпульсу С не было сбоя, триггер 9 возвра щается в нулевое состояние, выключив накопитель 5. После снятия сигнала с БХОДЗ 25 триггер 14 фронтом синхроимпульса перек.лючается в нулевое состояние ив связи , с тем, что триггер 18 находится в нулевом состоянии, ка выходе элемента ИЛИ-НЕ 6 появляется «1, которая, пройдя черезэлемент ИЛИ 12, выключает блок 2. По спаду этого же синхроимпульса в нулевое состояние переключается триггер 15. Еидинца с его инверсного выхода запрещает работу формирователя 16, который все же успевает сформировать еще один импульс записи (М,, на фиг. 2) изза задержки запрещающего импульса относительно спада синхроимпульса на входе синхронизации формирователя 16. По этому последнему импульсу записи в накопитеЛь 5 может записаться результат контроля записи в блок 2 по последнему адресу (А,, в режиме записи на фиг. 2). По концу последнегр импульса записи (Mj на фиг. 2) триггер 18 переключается в нулевое состояние..Единица с его инверсного выхода, поTrtaB на вход элемента ИЛИ-НЕ 6, вызывает включение блока 2 и устанавливает сиг-« нал на выходе 36, свидетельствующий о том, что устройство находится в режиме считывания. Кроме того, сигналы с обоих выходов триггера 18, управляя элементом ИЛИ-И 13, запрещают синхроимпульсы записи на входе 26 и разрешают синхроимпульсы, считывания на входе 27. Сигнал с выхода 36 попадает на вход установки триггера 9, в результате на выходе элемента ИЛИ-НЕ 7 появляется «О и накогтитель 5 включается. Как видно из описания р боты устройства в режиме записи, накопитель 5 включается по второму управляю-, щему в.ходу «Выбор кристалла тачько в случае сбоя в блоке 2 памяти и тапько в этом случае по соответствующему адресу накопителя 5 производится запись «1. Таким образом, если сбоем устройства в целом считать несоответствие информации в накопителе 5 реальным результатам контроля, то вероятность такого сбоя Р можно выразить как Р Р (ОЗУ)- Р(Н), где погл тчт/л - г, Лпг-ч,л О гч Р(ОЗУ) - вероятность сбоя в блоке 2 в режиме записи, Р(Н) - вероятность сбоя накопителя 5. Вероятность же сбоя в известном устройстве равна Р(Н), так как запись результатов контроля в накопитель 5 производится независимо от этих результатов и в случае верной записи информации в ОЗУ («О), и в случае записи со сбоем «1. Учитывая тот факт, что Р(ОЗУ) - величина много меньшая единицы, можно говорить о повышении достоЕ ер юсти контроля в 1/Р(ОЗУ) раз. В режиме считывания триггер 14 находится в нулевом состоянии, поэтому коммутатор 3 подключает информационный вход регистра 4 к входу 22 и по синхроимпульсам считывания адреса для блока 2 и накопителя 5 формируется одновременно, без сдзкга, обеспечивая одновременно считывание информации из блока 2 и. результата ее контроля (нуля, если информация верная и единицы, если неверная) из накО(пителя 5, выход 24 которого служит разрядом (например, старшим) выходной щи-. ны данных блока 2 памяти. Повышение достоверности контроля достигнуто благодаря тому, что при введении элемента ИЛИ-НЕ 7, триггера 19, элеменО ИЛИ 10 и 12 и новых связей появляется возможность сократить количество обращений к накопителю 5 в количество раз, в среднем равное ojyf сбои накопителя 5 могут происходить только в to время, когда в него записываются результаты контроля, .а они записываются только тогда, когда происходит сбой в блоке 2 (ОЗУ), что возможно благодаря то.му, что в режиме установки накопителя 5 по всем адресам устанавливаются «О, а в режиме записи фактически «дописываются «I по тем адресам, по которым информация в ОЗУ записалась со сбоем. Технико-экономическое преимущество предлагаемого устройства заключается в его более высокой достоверности контроля ho сравнению с прототипом.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля записи информации в блоках памяти | 1976 |

|

SU723675A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заяв-ке № 3234132/18-24, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-02-28—Публикация

1982-07-19—Подача