ел

(СО О5

сл

оо

31Ь

Изобретение относится к электросвязи и предназначено для тактовой и цикловой синхронизации приходящих по цифровым трактам сигналов с опорными сигналами станции коммутации каналов.

Цель изобретения повышение точности синхронизации групповых сигналов цифровых трактов.

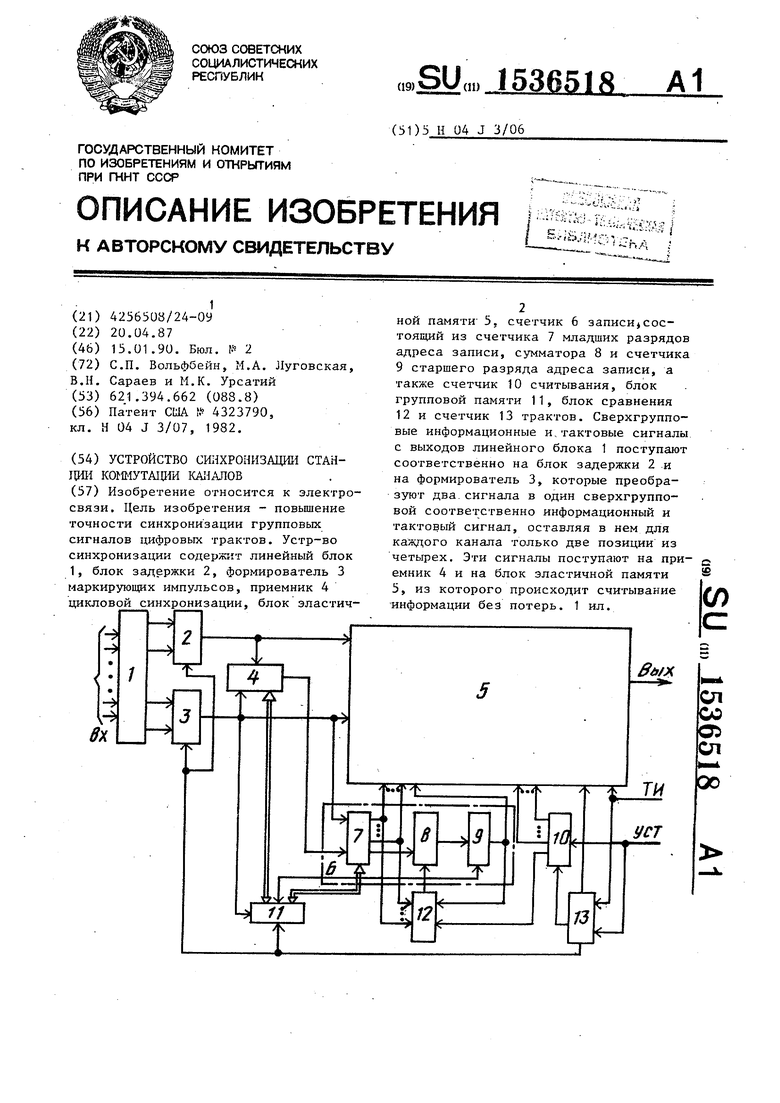

На чертеже представлена структурная электрическая схема устройства синхронизации станции коммутации каналов.

Устройство синхронизации станции коммутации каналов содержит линейный блок 1, блок 2 задержки, формирователь 3 маркирующих импульсов, прием

ник 4 цикловой синхронизации, блок 5 эластичной памяти, счетчик б записи, в состав которого входят счетчик 7 младших разрядов адреса записи, сумматор 8 и счетчик 9 старшего разряда адреса записи, счетчик 10 считывания блок 11 групповой памяти, блок 12 сравнения и счетчик 13 трактов.

Устройство синхронизации станции коммутации каналов работает следующим образом.

На информационные входы устройства по линиям связи поступают сигналы п цифровых трактов, которые обрабатываются в линейном блоке 1.

Сигналы поступают на станцию от независимых источников, вследствие чего их скорости отличаются как друг от друга, так и от задающей частоты станции. Кроме того, в процессе прохождения линий связи сигналы приобретают краевые искажения импульсов. Поэтому, чтобы избежать потерь информации, стробирование сигналов для их объединения осуществляется с частотой, большей номинальной скорости сигналов. В данном устройстве первоначальная частота стробирования в 4 раза выше, чем скорость сигнала. Для передачи одного символа информации в сверхгрупповом сигнале отводится 4 позиции. Четырехкратное увеличение частоты необходимо для избежания потерь информации при входном стробировании, но для дальнейшей безошибочной передачи простробиро- ванного сигнала к станции коммутации достаточно сохранить для этого сигнала в сверхгрупповой последователь- ности только две позиции после соответствующих преобразований.

0

5

0

5

0

5

0

5

0

5

Все приходящие сигналы разделяются на две группы. Одна половина приходящих сигналов стробируется учетверенной частотой и затем объединяется, другая половина обрабатывается аналогично. Стробирование ведется частотой, синхронной с частотой станции. Тактовые последовательности, выделенные из сигналов, стробируются той же учетверенной частотой и объединяются в два сверхгрупповых тактовых сигнала, которые поступают на так товые выходы линейного блока 1, на информационные выходы которого поступают сверхгрупповые информационные сигналы.

В каждом сверхгрупповом сигнале (информационном и тактовом) соответственно блоком 2 задержки и формирователем 3 сохраняется только половина позиций, после чего каждая пара сверхгрупповых сигналов объединяется в один сигнал.

Сверхгрупповые тактовые сигналы с выходов линейного блока 1 поступают на входы формирователя 3, который преобразует два сигнала в один сверхгрупповой тактовый сигнал, оставляя

в нем для каждого канала только две позиции из четырех внутри единичного интервала частоты 2,4 кГц, Причем та позиция тактового сигнала, начало которой совпадает с серединой соответствующей информационной посылки номинальной длительности, передается 1, другая (или две другие при удлиненной посылке) передается О При укороченной информационной посылке ей соответствует передача в тактовом сигнале только одной позиции состоянием 1.

Сверхгрупповые информационные сигналы с выходов линейного блока 1 поступают на блок 2 задержки, преобразующий их в один сверхгрупповой сигнал, в котором также остается только по две позиции из четырех для каждого канала. Кроме того, сигналы задерживаются таким образом, чтобы позиция, начало которой приходится на середину информационной посылки номинальной длительности, совпадала с 1 в соответствующем тактовом сигнале.

Сверхгрупповой информационный сигнал поступает на информационные , входы приемника 4 и блока 5 эластичной памяти. На тактовый вход приемника 4 и вход команды записи блока эластичной памяти поступает сверхгрупповой тактовый сигнал. Запись информации в ячейки блока 5 эластичной памяти и блока 11 -групповой памяти происходит только тогда,когда в сверхгрупповом тактовом сигнале приходит 1, причем каждая информационная посылка как номинальной длительности, так и удлиненная или укороченная записывается в блок эластичной памяти 5 и в блок групповой памяти 11 только один раз.

Приемник 4 ведет поиск регулярных синхрокомбинаций в каждом- из групповых сигналов, составляющих сверхгрупповой информационный сигнал. Поиск синхрокомбинаций ведется во всех групповых сигналах параллельно и независимо, что обеспечивается не только приемником 4, но и блоком 11 групповой памяти.

При обнаружении синхрокомбинаций из приемника 4 выходит сигнал, отмечающий границы цикла и устанавливающий в нулевое состояние счетчика 7 младших разрядов адреса записи, выходы которого подключены к адресным входам блока 5 эластичной памяти. Счетчик 9 старшего разряда адрес записи работает независимо от указанной начальной установки. Этот счетчик 9 определяет одну из двух групп ячеек памяти, выделенных для узаписи информационных посылок каждого канала.

Считывание информации из блока 5 эластичной памяти происходит при подаче определенных адресов считывания формируемых счетчиком 10 считывания и поступающих на адресные входы блока 5 эластичной памяти. Установка в начальное состояние всех разрядов счетчика 10 считывания как младших, так и старших осуществляется одновременно сигналом Установка станции.

Запись и считывание информации от каждого из п цифровых трактов производится раздельно и независимо. Это обеспечивается формированием специальных дополнительных адресных сигналов счетчиком 13 трактов. Длительность существования каждого такого адреса в п раз меньше длительности единичного интервала сигнала, передаваемого по одному цифровому тракту. Указанные адресные сигналы являются общими как для записи, так

и для считывания и поступают на дополнительные адресные входы блока Ь эластичной памяти.

Счетчики 7 и 9 записи являются групповыми устройствами, а счетчик считывания 10 и счетчик трактов 13 - одноканальными устройствами.

При отсутствии расхождения скоростей приходящих сигналов и станционных тактовых импульсов между записью определенных информационных символов и их считыванием проходит один и тот же постоянный отрезок времени. Считывание в этом случае происходит

0

5

без потерь и вставок информации.

5

0

0

Если скорости приходящих сигналов не совпадают со станционными такто-

0 выми импульсами, то моменты считывания начинают отставать (или опережать) от моментов записи, что приводит к выпадению или вставкам информации, но эти потери существенно

5 меньше, чем в прототипе.

В определенные моменты времени из-за систематического отставания моментов считывания по отношению к моментам записи память блока 5 эластичной памяти оказывается переполненной информацией. Это обнаруживается с помощью блока 12 сравнения и сумматора 8 путем сопоставления опредет ленных адресных сигналов записи и счи5 тывания, включая и те дополнительные адресные сигналы, которые в счетчиках 7 и 10 формируются специально для этой цели. Следствием обнаружения переполнения является появление на выходе сумматора 8 сигнала, устанавливающего счетчик 9 старшего разряда адреса записи в состояние, про- , тивоположное тому, в котором он находится. При этом не происходит стирания информации, записанной ранее в память блока 5 эластичной памяти. Изменение старшего разряда адреса записи на противоположное значение при- водит к тому, что при объеме памяти в 2 N бит для каждого тракта запись продолжается с пропуском N символов.Поскольку процесс считывания не прекрат щается ни на один такт,то с определенного момента из устройства после

5 1-го цикла выходит (1+2)-й цикл. Таким,образом пропущен только один цикл, а не два, как это происходит в прототипе.

10

15

Формула изобретения

Устройство синхронизации станции коммутации каналов, содержащее линейный блок, входы которого являются информационными входами устройства, объединенные по информационно-г му входу приемник цикловой синхрони зации и блок эластичной памяти, к входам адресов записи и считывания которого подключены соответственно ад- выходы счетчика записи и счетчика считыванияs причем тактовые приемника цикловой синх1лониза- цйи и счетчшса записи объединены с входом управления записью блока эластичной памяти, а также блок сравнения и счетчик трактов, отличающееся тем, что, с целью повышения точности синхронизации групповых сигналов цифровых трактов, введены блок задержки, формирователь маркирующих импульсов и блок групповой памяти, а счетчик записи выполнен в виде последовательно соединенных счетчика 25 младших разрядов адреса записи,сумматора и счетчика старшего разряда записи, причем адресные выходы счетчика младших разрядов адреса записи и адресный выход счетчика старшего -JQ разряда адреса записи, которые являются адресными выходами счетчика записи, подключены к соответствующим входам блока сравнения, выход которого подключен к второму входу сум15365188

матора, информационные выходы линейного блока через блок задержки подключены к информационному входу блока эластичной памяти, а тактовые выходы линейного блока через формирователь маркирующих импульсов подключены к тактовым входам приемника цикловой синхронизации и блока групповой памяти, соединенного соответствующими цепями чтения-записи с приемником цикловой синхронизации, счетчиком младших разрядов адреса записи и счетчиком старшего разряда адреса записи, выход приемника цикловой синхронизации подключен к установочному входу счетчика младших разрядов адреса записи, тактовый вход счетчика трактов объединен с входом команды записи блока эластичной памяти, который является тактовым входом устройства, установочным входом которого являются объединенные установочные входы счетчика считывания и счетчика трактов, первый и второй адресные выходы которого подключены соответственно к объединенным адресным входам блока групповой памяти и формирователя маркирующих импульсов и к дополнительному адресному сходу блока эластичной памяти, а дополнительный выход счетчика считывания подключен к соответствующему входу блока сравнения .

20

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ГРУППОВОЙ ПРИЕМНИК СИГНАЛОВ УПРАВЛЕНИЯ И ВЗАИМОДЕЙСТВИЯ С АДАПТИВНОЙ ДИФФЕРЕНЦИАЛЬНОЙ ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ | 1993 |

|

RU2103840C1 |

| Групповой приемник сигналов управления и взаимодействия с адаптивной дифференциальной импульсно-кодовой модуляцией | 1991 |

|

SU1829126A1 |

| УСТРОЙСТВО ПРИЕМА И ПЕРЕДАЧИ АСИНХРОННОЙ ИНФОРМАЦИИ | 1992 |

|

RU2030114C1 |

| Коммутационное устройство | 1987 |

|

SU1478371A1 |

| УСТРОЙСТВО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 2006 |

|

RU2306674C1 |

| СИНХРОННЫЙ АДАПТИВНЫЙ МУЛЬТИПЛЕКСОР | 1993 |

|

RU2078401C1 |

| Электронный коммутатор | 1988 |

|

SU1626444A1 |

| Устройство для телеконтроля промежуточных станций систем связи | 1985 |

|

SU1256216A1 |

| Устройство обнаружения кодов групповой синхронизации | 1990 |

|

SU1812628A1 |

| Цифровой формирователь трехфазных синусоидальных сигналов | 1990 |

|

SU1732418A1 |

Изобретение относится к электросвязи. Цель изобретения - повышение точности синхронизации групповых сигналов цифровых трактов. Устройство синхронизации содержит линейный блок 1, блок задержки 2, формирователь 3 маркирующих импульсов, приемник 4 цикловой синхронизации, блок эластичной памяти 5, счетчик 6 записи, состоящий из счетчика 7 младших разрядов адреса записи, сумматора 8 и счетчика 9 старшего разряда адреса записи, а также счетчик 10 считывания, блок групповой памяти 11, блок сравнения 12 и счетчик 13 трактов. Сверхгрупповые информационные и тактовые сигналы с выходов линейного блока 1 поступают соответственно на блок задержки 2 и на формирователь 3, которые преобразуют два сигнала в один сверхгрупповой соответственно информационный и тактовый сигнал, оставляя в нем для каждого канала только две позиции из четырех. Эти сигналы поступают на приемник 4 и на блок эластичной памяти 5, из которого происходит считывание информации без потерь. 1 ил.

| Патент ША № 4323790, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-01-15—Публикация

1987-04-20—Подача