Изобретение относится к технике связи и может использоваться в приемниках многоканальных модемов..

Цель изобретения - повьптение объема принимаемой информации.

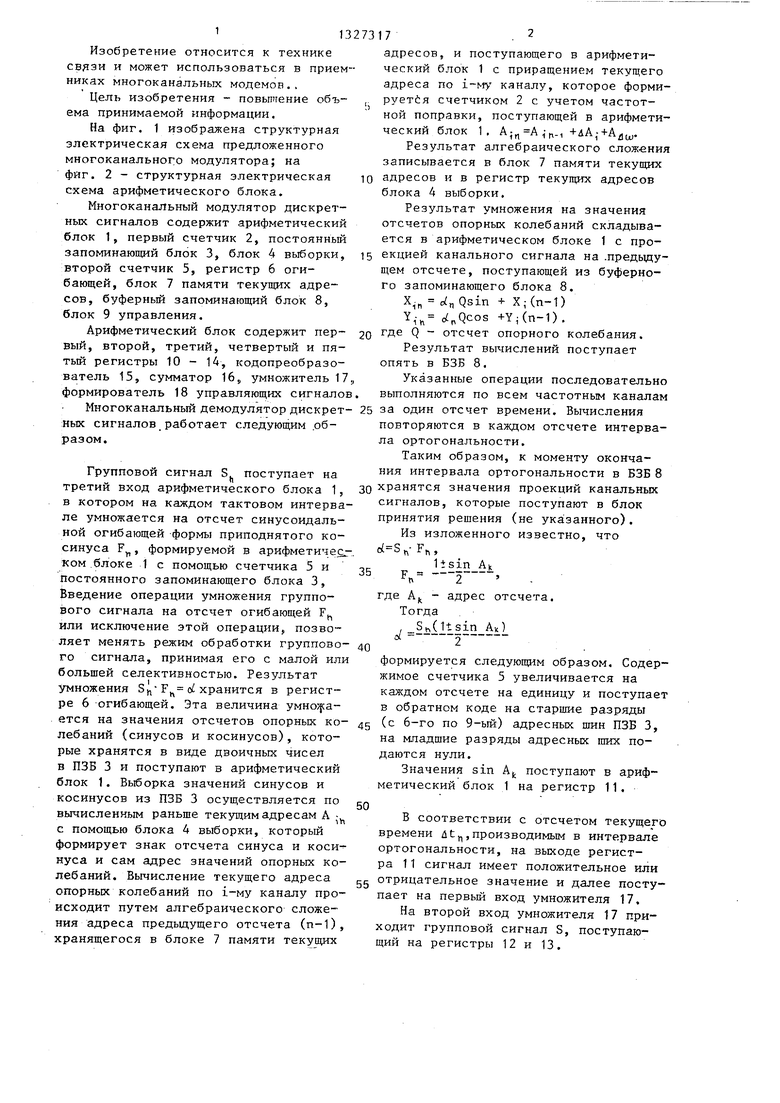

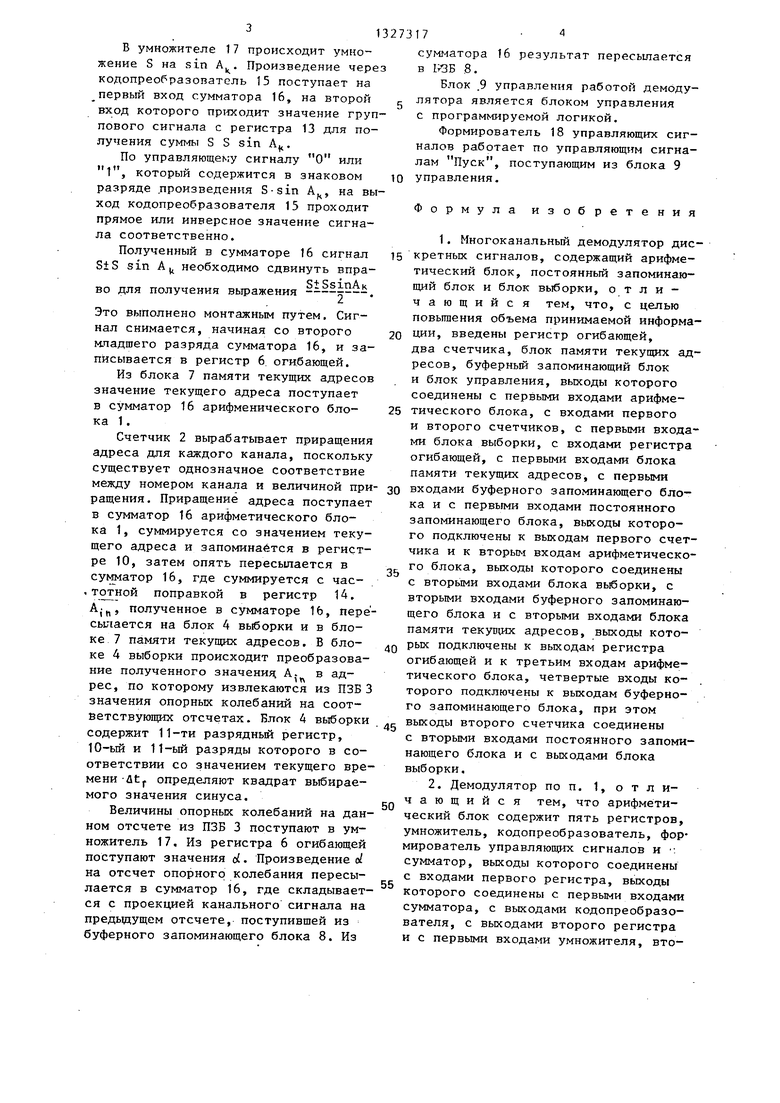

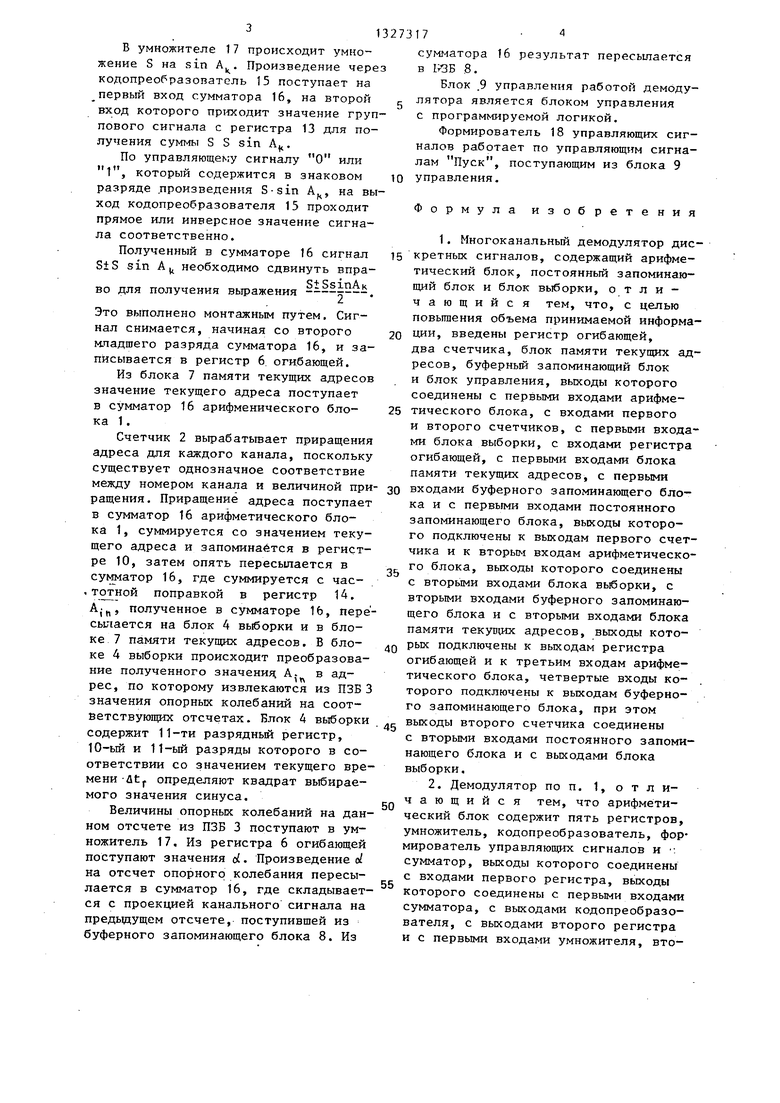

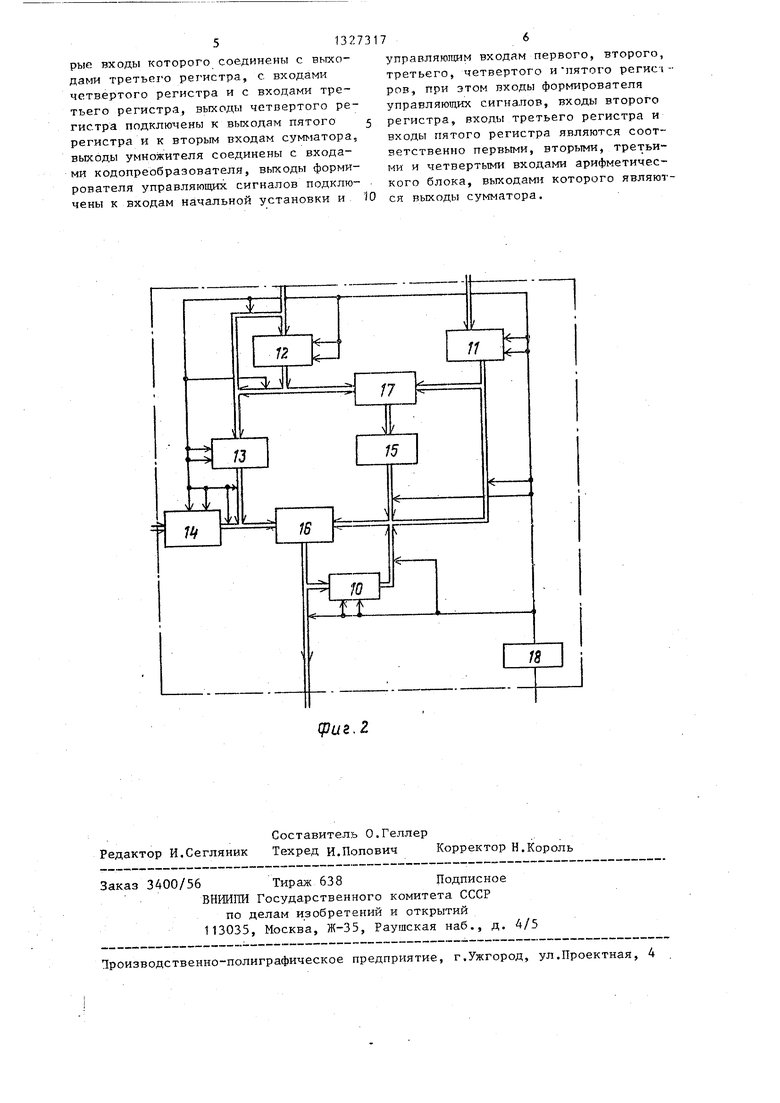

На фиг. 1 изображена структурная электрическая схема предложенного многоканального модулятора; на фиг. 2 - структурная электрическая схема арифметического блока.

Многоканальный модулятор дискретных сигналов содержит арифметический блок 1, первый счетчик 2, постоянный запоминающий блок 3, блок 4 выборки, второй счетчик 5, регистр 6 огибающей, блок 7 памяти текущих адресов, буферный запоминающий блок 8, блок 9 управления.

Арифметический блок содержит пер- 20 Q отсчет опорного колебания, вый, второй, третий, четвертый и пя- Результат вычислений поступает тый регистры 10 - 14, кодопреобразо- опять в БЗБ 8.

ватель 15, сумматор 16, умножитель 17, Указанные операции последовательно формирователь 18 управляющих сигналов, выполняются по всем частотным каналам

Многоканальный демодулятор дискрет- 25 за один отсчет времени. Вычисления

ных сигналов работает следующим образом.

повторяются в каждом отсчете интервала ортогональности.

Таким образом, к моменту окончания интервала ортогональности в БЗБ 8

третий вход арифметического блока 1, зо Р нятся значения проекций канальных

сигналов, которые поступают в блок

Групповой сигнал S поступает на

35

в котором на каждом тактовом интервале умножается на отсчет синусоидальной огибающей формы приподнятого косинуса F, формируемой в арифметичесг. ком блоке 1 с помощью счетчика 5 и Постоянного запоминающего блока 3, Введение операции умножения группового сигнала на отсчет огибающей F, или исключение этой операции, позволяет менять режим обработки группово- 40 го сигнала, принимая его с малой или большей селективностью. Результат умножения oi хранится в регистре 6 огибающей. Эта величина умноз|сапринятия решения (не ука занного) .

Из изложенного известно, что ,-F,,

1

2

где А - адрес отсчета. Тогда

ТГ г

С/

S dtsin Ак)

формируется следуюшЕИм образом. Содержимое счетчика 5 увеличивается на каждом отсчете на единицу и поступает в обратном коде на старшие разряды

на младшие разряды адресных ших подаются нули.

Значения sin Aj, поступают в арифметический блок 1 на регистр 11,

50

ется на значения отсчетов опорных ко- 5 6-го по 9-ый) адресных шин ПЗБ 3, лебаний (синусов и косинусов), которые хранятся в виде двоичных чисел в ПЗБ 3 и поступают в арифметический блок 1, Выборка значений синусов и косинусов из ПЗБ 3 осуществляется по вычисленным раньще тек5пдим адресам А - с помощью блока 4 выборки, который формирует знак отсчета синуса и косинуса и сам адрес значений опорных колебаний. Вычисление текущего адреса оп:орных колебаний по i-му каналу происходит путем алгебраического сложения адреса предыдущего отсчета (п-1), хранящегося в блоке 7 памяти текущих

В соответствии с отсчетом текущего времени it,производимым в интервале ортогональности, на выходе регистра 11 сигнал имеет положительное или gg отрицательное значение и далее поступает на первый вход умножителя 17.

На второй вход умножителя 17 приходит групповой сигнал S, поступающий на регистры 12 и 13,

адресов, и поступающего в арифметический блок 1 с приращением текущего адреса по i-Nfy каналу, которое формируетйя счетчиком 2 с учетом частот- „„ ,

НОИ поправки, поступающей в арифметический блок 1, ,-f,., (.

Результат алгебраического сложения записывается в блок 7 памяти текущих адресов и в регистр текущих адресов блока 4 выборки.

Результат умножения на значения отсчетов опорных колебаний складывается в арифметическом блоке 1 с про- акцией канального сигнала на .предыду- П1ем отсчете, поступающей из буферного запоминающего блока 8. Х,„ « „Qsin -t- X;(n-1) Y,-, ,,Qcos +Y;(n-1).

35

40

принятия решения (не

Из изложенного известно, ,-F,,

1

2

где А - адрес отсчета. Тогда

ТГ г

С/

S dtsin Ак)

формируется следуюшЕИм образом. Содержимое счетчика 5 увеличивается на каждом отсчете на единицу и поступает в обратном коде на старшие разряды

на младшие разряды адресных ших подаются нули.

Значения sin Aj, поступают в арифметический блок 1 на регистр 11,

6-го по 9-ый) адресных шин ПЗБ 3,

50

5 6-го по 9-ый) адресных шин ПЗБ 3,

В соответствии с отсчетом текущего времени it,производимым в интервале ортогональности, на выходе регистра 11 сигнал имеет положительное или gg отрицательное значение и далее поступает на первый вход умножителя 17.

На второй вход умножителя 17 приходит групповой сигнал S, поступающий на регистры 12 и 13,

31

В умножителе 17 происходит умножение S на sin А. Произведение чере кодопреобразователь 15 поступает на первый вход сумматора 16, на второй вход которого приходит значение группового сигнала с регистра 13 для получения суммы S S sin Л.

По yпpaвляюIцe :y сигналу О или 1, который содержится в знаковом разряде произведения S-sin А, на выход кодопреобразователя 15 проходит прямое или инверсное значение сигнала соответственно.

Полученный в сумматоре 16 сигнал SiS sin А необходимо сдвинуть впраSiSsinAKво для получения вьфажения .

Это выполнено монтажным путем. Сигнал снимается, начиная со второго младшего разряда сумматора 16, и записывается в регистр 6. огибающей.

Из блока 7 памяти текущих адресов значение текущего адреса поступает в сумматор 16 арифменического бло- ка 1.

Счетчик 2 вырабатывает приращения адреса для каждого канала, поскольку существует однозначное соответствие между номером канала и величиной при ращения. Приращение адреса поступает в сумматор 16 арифметического блока 1, суммируется со значением текущего адреса и запоминается в регистре 10, затем опять пересылается в сумматор 16, где суммируется с час- ,тотной поправкой в регистр 14. Aj, полученное в сумматоре 16, пересыпается на блок 4 выборки и в блоке 7 памяти текущих адресов, В бло- ке 4 выборки происходит преобразование полученного значенид А- в адрес, по которому извлекаются из ПЗБ 3 значения опорных колебаний на соответствующих отсчетах. Блок 4 выборки содержит 11-ти разрядный регистр, 10-ый и 11-ый разряды которого в соответствии со значением текущего времени -utf определяют квадрат выбираемого значения синуса.

Величины опорных колебаний на данном отсчете из ПЗБ 3 поступают в умножитель 17. Из регистра 6 огибающей поступают значения d. Произведение о на отсчет опорного колебания пересылается в сумматор 16, где складывается с проекцией канального сигнала на предьщущем отсчете, поступившей из буферного запоминающего блока 8. Из

г

s

0

5

о Q

5

0

5

17

сумматора 16 результат пересылается

в гав ,8.

Блок .9 управления работой демодулятора является блоком управления с программируемой логикой.

Формирователь 18 управляющих сигналов работает по управляющим сигналам Пуск, поступающим из блока 9 управления.

Формула изобретения

1.Многоканальный демодулятор дискретных сигналов, содержащий арифметический блок, постоянный запоминающий блок и блок выборки, отличающийся тем, что, с целью повышения объема принимаемой информации, введены регистр огибающей,

два счетчика, блок памяти текущих адресов, буферный запоминающий блок и блок управления, выходы которого соединены с первыми входами арифметического блока, с входами первого и второго счетчиков, с первыми входами блока выборки, с входами регистра огибающей, с первыми входами блока памяти текущих адресов, с первыми входами буферного запоминающего блока и с первыми входами постоянного запоминающего блока, выходы которого подключены к выходам первого счетчика и к вторым входам арифметического блока, выходы которого соединены с вторыми входами блока выборки, с вторыми входами буферного запоминающего блока и с вторыми входами блока памяти текзтцих адресов, выходы которых подключены к выходам регистра огибающей и к третьим входам арифметического блока, четвертые входы которого подключены к выходам буферного запоминающего блока, при этом выходы второго счетчика соединены с вторыми входами постоянного запоминающего блока и с выходами блока выборки.

2.Демодулятор по п. 1, отличающийся тем, что арифметический блок содержит пять регистров, умножитель, кодопреобразователь, формирователь управляющих сигналов и : сумматор, выходы которого соединены с входами первого регистра, выходы которого соединены с первыми входами сумматора, с выходами кодопреобразователя, с выходами второго регистра

и с первыми входами умножителя, вто-

5132731

рые входы которого соединены с выходами третькт о регистра, с. входами четвертого регистра и с входами третьего регистра, выходы четвертого регистра подключены к выходам пятого 5 регистра и к вторым входам сумматора, выходы умножителя соединены с входами кодопреобразователя, выходы формирователя управляющих сигналов подклго- . чены к входам начальной установки и 10

управляющим входам первого, второго, третьего, четвертого и пятого регисч- ров, при этом входы формирователя управляющих сигналов, входы второго регистра, входы третьего регистра и входы пятого регистра являются соответственно первыми, вторыми, третьими и четвертыми входами арифметического блока, выходами которого являются выходы сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровая адаптивная антенная система | 1990 |

|

SU1810943A1 |

| Цифровой обнаружитель-измеритель частоты | 1989 |

|

SU1797127A1 |

| Фурье-коррелятор | 1983 |

|

SU1164731A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| Устройство для сжатия информации | 1982 |

|

SU1056249A1 |

| Адаптивный цифровой декоррелятор | 1984 |

|

SU1234989A1 |

| Устройство для обработки радиосигналов | 1980 |

|

SU955083A1 |

| Устройство для сжатия информации | 1986 |

|

SU1324047A1 |

| Анализатор спектра | 1981 |

|

SU1002977A2 |

Изобретение м.б. использовано в приемниках многоканальных модемов. Цель изобретения - повышение объема принимаемой информации. Устр-во содержит арифметический блок 1, посто- HHHbrfi запоминающий блок 3 и блок 4 выборки. В устр-во введены счетчики 2 и 5, регистр 6 огибающей, блок 7 памяти текущих адресов, буферный запоминающий блок 8, блок 9 управления. В п. 2 ф-лы дано устройство блока 1, содержащего пять регистров, кодопреобразователь, сумматор, умножитель, формирователь управляющих сигналов. 1 3.п. ф-лы. 2 ил. со ю 00 фиг.1

.2

| Многоканальный демодулятор дискретныхСигНАлОВ | 1979 |

|

SU809646A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-07-30—Публикация

1986-03-24—Подача