Изобретение относится к вычислительной технике, в частности, может быть использовано при построении специализированных вычислительных устройств, применяемых в системах автоматического управления и контроля. .

Известно множительное устройство, содержащее ячейки умножения в виде соединенных между собой счетчика импульсов и дешифратора с коммутатором, триггеры управления, выходной вентиль, многоканальный сумматор импульсов 3Недостатком этого устройства является сложность исполнения и аппаратурная избыточность.

Известно также множительное устройство последоватепьного действия, содержащее регистр множимого, выполненный из двух реверсивных счетчиков и двух многовходовых элементов И, регистр результата, схему управления, состоящую из генератора импульсов, триггеров и двух элементов И 2 .

Недостатком этого устройства яв ляется сложность и низкое быстродействие.

Наиболее близким к предлагаемому является множительное устройство, содержащее генератор импульсов, элемент и, старт-стопный триггер, счетчики первого и второго сомножителя и результата, регистр первого сомножителя, информационные шины дополнительного кода второго сомножителя з.

10

Недостатком известного устройства является ограниченное быстродействие, определенное периодом следования тактовых импульсов задающего генератора.

15

Цель изобретения - повышение быстродействия множительного устройства.

Поставленная цель достигается тем, что множительное устройство,

20 содержащее регистр первого сомножителя, счетчики второго сомножителя и произведения, причем входы регистра первого сомножителя подключены к шине первого сомножителя уст25ройства, информационные входы счетчика второго сомножителя подключены к шине второго сомножителя устройства, выходы счетчика произведения подключены к шине произведения

30 устройства, содержит преобразователь кода в серию импульсов, информационные входы которого соединены с соответствующими выходами регистра первого сомножителя, информационный выход- преобразователя кода в серию импульсов подключен j« счетному входу счетчика произведения устройства, управляющий вход преобразователя кодов в серию импульсов подключен к выходу.счетчика второго сомножителя, управляющий выход преобразователя кода в серию импульсов подключен к счетному вход счетчика второго сомножителя.

Кроме того, преобразователь кода в серию импульсов содержит счетчик , выполненный на сдвиговом регис ре, двухвходовые элементы И и элемент ИЛИ, причем информационные входы счетчика подключены к соответствующим информационным входам преобразователя кода в серию импульсов прямой и инверсный выходы каждого триггера, счетчика соединены соответственно с первым и вторым входами соответствующего элемента И, йыходы элементов И подключены к входам элемента ИЛИ, выход которого подк71ючен к счетному входу счетчика и к информационному выходу прёобразователя кода в серию импульсов, управляющий вход элемента ИЛИ, соединен с управляющим входом преобразователя кода в серию импульсов, а .выход переполнения счетчика соединен с его управляющим входом и с управляющим выходом преобразователя кода в серию импульсов.

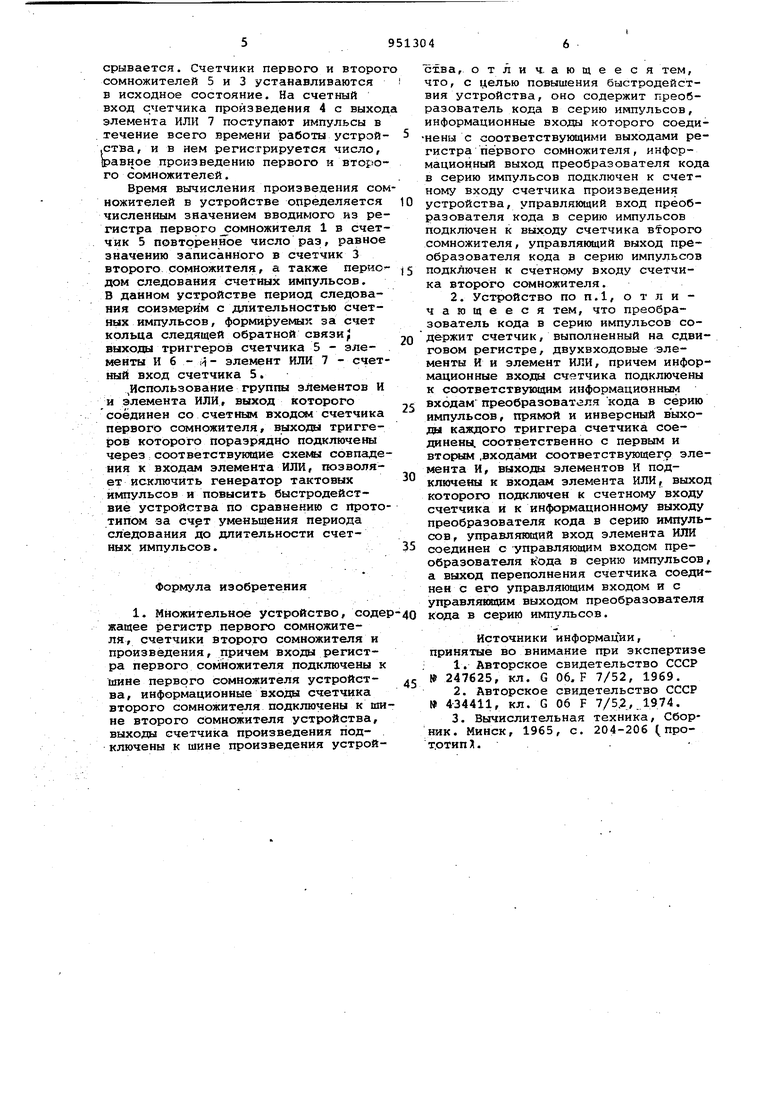

На фиг. 1 представлена блоксхема устройства; на фиг. 2 блок-схема преобразовател я кода в серию импульсов.

Устройство состоит из регистра первого сомножителя 1, преобразователя кода в серию импульсов 2, счетчика второго сомножителя 3, счетчика произведения 4. Информационные входы регистра йервого сомножителя 1 подключены к шине первого сомножителя устройства, а его выходы подключены к информационным входам преобразователя кода в серию импульсов 2, информационный выход которого подключен к счетному входу счетчика произведения устройства 4 , выходы которого ПОДК.7ПО.чены к шине произведения устройства Управляющий вход преобразователя кода в серию импульсов подключен к выходу счетчика второго сомножителя 3, управляющий выход преобразователя кода в сери1о импульсов - к. счетному входу счётчика второго сомножителя 3, информационные входы которого подключены к шине второго сомножи.теля устройства.

Преобразователь кода в серию импульсов состоит из счетчика выполненного на сдвиговом регистре 5, информационные входы которого подключены к информационным входам преобразователя кода в серию импульсов, двухвходовых элементов и 6-1,...6-п,

первый и второй входы каждого из которых соединены соответственно с пряк4лм и инверсным выходами соответствующего триггера счетчика 5 и элемента ИЛИ 7, входыкоторого соеди-у

0 нены с выходами элементов И, управляющий вход соедийен с управляющим входом преобразователя кода в серию импульсов, информационный выход элемента ИЛИ.7 подключен к информационному выходу преобразователя кода в серию импульсов и к счетному входу счетчика.

Устройство работает следующим образом.

0 В исходном состоянии счетчики 3-5 обнулены, элемент ИЛИ 7 закрыт потенциалом, поступанвдим на его управляющий вход с выхода.Ч:четчика второго сомножителя 3. Сомножители в пара лель5 ном коде соответственно заносятся в счетчик второго сомножителя 3, а также-в регистр первого сомножителя 1 и счетчик 5. Открывается элемент ИЛИ 7. Пepekлючeниe i -тых триггеров счетчика 5 из нулевого состояния в единичное приводит и формированию на выходах элемента И б-f (где 1,2,3....п) импульса, который поступает чераз элемент ИЛИ 7 на счетный вход счетчика первого сомножителя 5. При этсям из счетчика 5 вычитается единица, а переключение его -f-тых триггеров вызывает формирование очередного импульса описанным способом на выходе элемента

0 ИЛИ 7. Этим импульсом вычитается следующая единица из счетчика 5, и процесс вычитания продолжается посредством формирования счетных импульсов на выходе элемента ИЛИ 7 за

5 счет переключения триггеров счетчика первого сомножителя 5.

Кактолько из счетчика первого сомножителя 5 вычитается число, пропорциональное первому сомножителю,

Q на его выходе появляется сигнал. При этом из числа, записанного в счетчике второго сомножителя 3, вычитается единица, а в счетчик сомножителя 5 вновь записывается по ине формационным входам из регистра 1

первый сомножитель.

I

Описанное продолжается до тех пор, пока из счетчика второго сомножителя 3 не будет считана последняя единица, т.е. счетчик второго сомножителя 3 обнуляется. Потенциал сфор.мированный при этом на выходе счетчика второго сомножителя 3, закрывает элемент ИЛИ 7 и генерация импульсов на выходе элемента ИЛИ 7 срывается. Счетчики первого и второг сомножителей 5 и 3 устанавливаются в исходное состояние. На счетный вход счетчика произведения 4 с выход элемента ИЛИ 7 поступают импульсы в .течение всего времени работы устрой.ства, и в нем регистрируется число, равное произведению первого и второго сомножителей. Время вычисления произведения сом ножителей в устройстве определяется численным значением вводимого из регистра первого :омножителя 1 в счетчик 5 повторенное число раз, равное значению записанного в счетчик 3 второго сомножителя, а также перио дом следования счетных импульсов. В данном устройстве период следования соизмерим с длительностью счетных импульсов, формируемых за счет кольца следящей обратной связиJ выходы триггеров счетчика 5 - элементы И 6 - й- элемент ИЛИ 7 - счет ный вход счетчика 5. Использование группы элементов И и элемента ИЛИ, выход которого соединен со счетным входсж счетчика первого сомножителя, выходы триггеров которого Поразрядно подключены через соответствующие схемы совпаде ния к входам элемента ИЛИ, позволяет исключить генератор тактовых импульсов и повысить быстродействие устройства по сравнению с прото типом за счет уменьшения периода следования до длительности счетных импульсов. Формула изобретения 1. Множительное устройство, содер жащее регистр первого сомножителя, счетчики второго сомножителя и произведения, причем входы регистра первого сомножителя подключены к шине первого сомножителя устройства, информационные входы счетчика второго сомножителя подключены к ши не второго сомножителя устройства, выходы счетчика произведения подключены к шине произведения устрой схва, отлич, ающееся тем, что, с целью повышения быстродействия устройства, оно содержит преобразователь кода в серию импульсов, информационные входы которого соединены с соответствующими выходами регистра первого сомножителя, информационный выход преобразователя кода в серию импульсов подключен к счетному входу счетчика произведения устройства, управляющий вход преобразователя кода в серию импульсов подключен к выходу счетчика второго сомножителя, управляниций выход преобразователя кода в серию импульсов подключен к счетному входу счетчика второго сомножителя. 2. Устройство по п.1, о т л и чающееся тем, что преобразователь кода в серию импульсов содержит счетчик, выполненный на сдвиговом регистре, двухвходовые элементы И и элемент ИЛИ/ причем информационные входы счетчика подключены к соответствующим информационным входам преобразователя кода в серию импульсов, прямой и инверсный выхода каждого триггера счетчика соеда1нены. соответственно с первым и вторьш .входами соответствующего элемента И, выходы элементов И подключены к входам элемента ИЛИ, выход которого подключен к счетному входу счетчика и к информационному выходу преобразователя кода в серию импульсов, управляющий вход элемента ИЛИ соединен с -управляющим входом преобразователя кода в серию импульсов, а выход переполнения счетчика соединен с его управляющим входом и с управлякядам выходом преобразователя кода в серию импульсов. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 247625, кл. G 06. F 7/52, 1969. 2.Авторское свидетельство СССР 434411, кл. G 06 F 7/5.2, .1974. 3.Вычислительная техника. Сборник. Минск, 1965, с. 204-206 (прототип Л.

ф ф

Ч (

V V W У

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотно-импульсное множительное устройство | 1979 |

|

SU857988A1 |

| Вычислительное устройство | 1981 |

|

SU1001114A1 |

| Множительно-делительное устройство | 1981 |

|

SU1015373A1 |

| Преобразователь кода угла в коды синуса и косинуса | 1977 |

|

SU684554A1 |

| Способ управления @ -фазным преобразователем и устройство для его осуществления | 1983 |

|

SU1115200A1 |

| Множительно-делительное устройство | 1981 |

|

SU982002A1 |

| Множительно-делительное устройство | 1978 |

|

SU813419A1 |

| Вероятностное множительное устройство | 1984 |

|

SU1251073A1 |

| Аналого-цифровое множительное устройство | 1983 |

|

SU1117655A1 |

| Устройство для вычисления суммы произведений двух массивов чисел | 1980 |

|

SU985782A1 |

I Ч/ Ч/

I

jKjk.

S-fr

ff-f

Фиг1

Авторы

Даты

1982-08-15—Публикация

1980-04-25—Подача