(5) ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифро-аналоговый функциональный преобразователь | 1980 |

|

SU895973A1 |

| Гибридный функциональный преобразователь | 1982 |

|

SU1582190A1 |

| Гибридный функциональный преобразователь | 1982 |

|

SU1076918A1 |

| Гибридный функциональный преобразователь | 1980 |

|

SU879610A1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU960837A1 |

| Вычислительное устройство | 1981 |

|

SU1001114A1 |

| Цифро-аналоговый многофункциональный преобразователь | 1982 |

|

SU1062732A2 |

| Устройство для цифрового функционального преобразования | 1981 |

|

SU985792A1 |

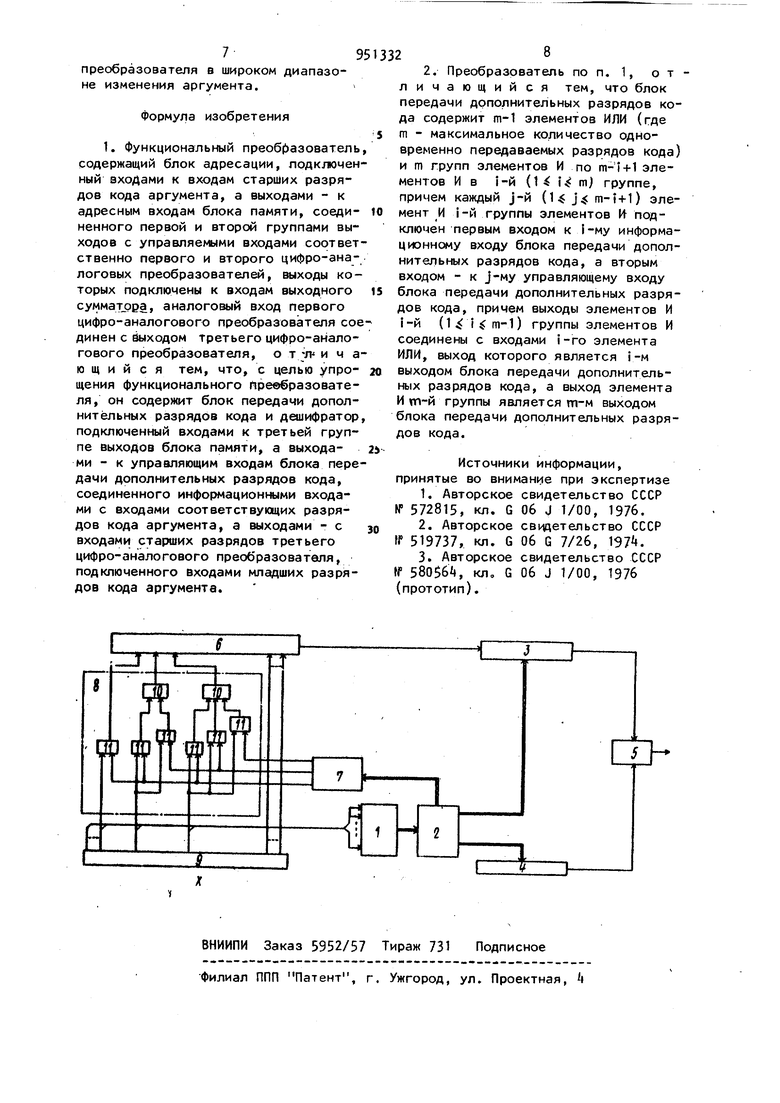

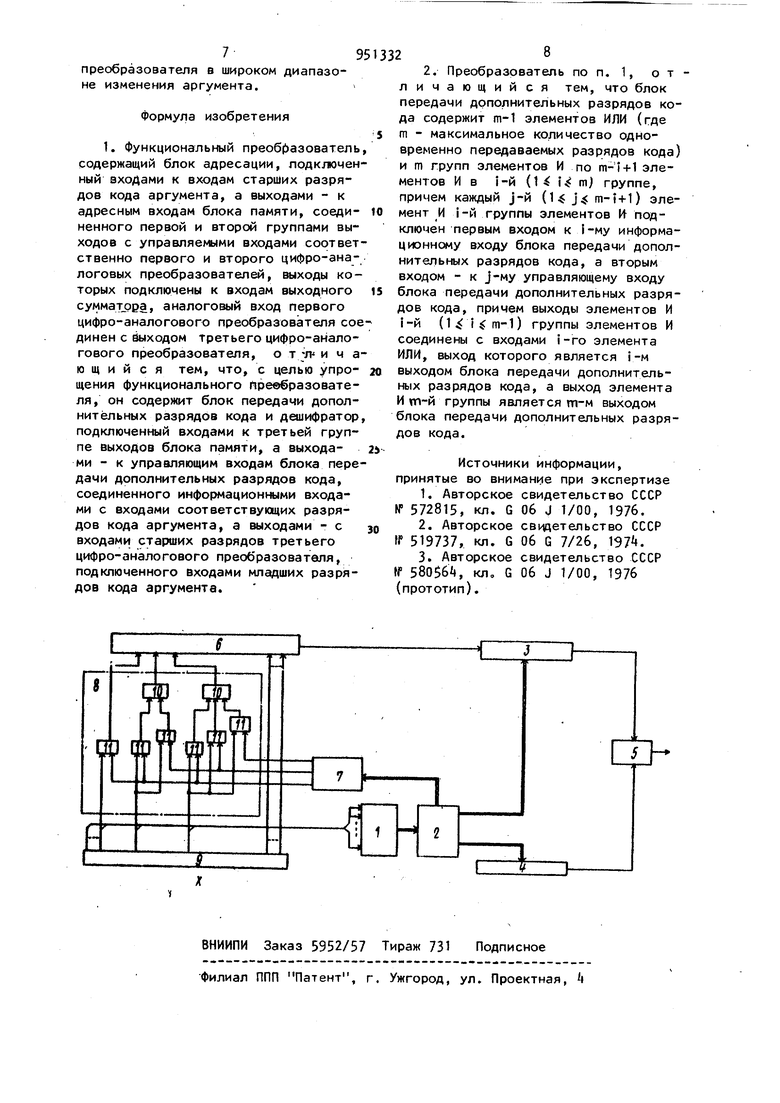

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам воспроизведения аналоговых функций, аргумент которых представлен цифровым кодом. Известен функциональный преобразователь, содержащий входной регистр, блок адресации, блок памяти .цифро-аналоговые преобразователи и выходной сумматор 1 Недостатком преобразователя явля ется пониженная точность воспроизведения функций из-за равномерного разбиения функций на подинтервалы аппроксимации. Известен также функциональньй пр образователь, , содержащий блок адресации, блок памяти, цифро-аналоговы преобразователи, вычитающий усилите и суммирующий усилитель 2. Недостатками данного преобразова теля являются сложность технической реализации и повышенная инструментальная погрешность воспроизведения функций. Наиболее близким к предлагаемому является преобразователь, содержащий блок адресации, подключенный входами к входам старших и младших разрядов аргумента, а выходами - к адресным входам блока памяти, соединенного первой и второй группами выходов с цифровыми входами соответственно первого и второго цифро-аналоговых преобразователей, выходы которых подключень к входам выходного сумматора, а аналоговый вход первого цифро-аналогового преобразователя соединен с выходом третьего цифро-аналогового преобразователя, подключенного входами к выходам блока формирования приращения аргумента, соединенного входами с дополнительными выходами блока адресации, причем блок адресации выполнен на дешифраторе и первой группе элементов ИЛИ, а блок формирования приращения 39 аргумента выполнен на второй группе элементов ИЛИГзЗНедостатком известного преобразов теля является сложность его техничес кой реализации при воспроизведении функций с заданной точностью в широком диапазоне изменения аргумента. Цель изобретения - упрощение функ ционального преобразоват.еля. Поставленная цель достигается тем что преобразователь, содержащий блок адресации, подключеннь1Й входами к входам старших разрядов кода аргумен та, а выходами - к адресным входам блока памяти, соединенного первой и второй группами выходов с цифровыми входами соответственно первого и вто рого Цифро-аналоговых преобразователей , выходы которых подключены к вхо дам выходного сумматора, аналоговый вход первого цифро-аналогового преоб разователя соединен с выходом третьего цифро-аналогового преобразователя, содержит блок передачи дополнительных разрядов кода и дешифратор подключенный входами к третьей группе выходов блока памяти, а выходами к управляющим входам блока передачи дополнительных разрядов кода, соединенного информационными входами с входами соответствующих разрядов код аргумента, а выходами - с входами старших разрядов третьего цифро-аналогового преобразователя, подключенного входами младших разрядов к входам младших разрядов кода аргумента. При этом блок передачи дополнител ных разрядов кода содержит т-1 элементов ИЛИ,где m - максимальное коли чество одновременно передаваемых раз рядов кода и т-групп элементов И по m-i-t-1 элементов И в i-ой 14- i ш группе, причем каждый J-ый ($.:т1+1) элемент И 1-ой групЛы элементов И подключен первым входом к i-ому информационному входу блока передачи дополнительных разрядов кода, а вторым входом - к j-ому управляющему входу блока передачи дополнительных разрядов кода, причем выходы элементов И i-ой (1 i m-1) группы элемен тов И соединены с входами i-ro элемента ИЛИ, выход которого является i-ым выходом блока передачи дополнительных разрядов кода, а выход эле мента И т-ои группы является т-ным выходом блока передачи дополнительных разрядов кода. 4 Сущность изобретения поясняется чертежом. На чертеже изображена блок-схема функционального преобразователя. Преобразователь содержит блок 1 адресации, подключенный входами к входам старших разрядов кода аргумента X, а выходами - к адресным входам блока 2 памяти, соединенного первой и второй группами выходов с цифровыми входами соответственно первого и второго цифро-аналоговых преобразователей 3 и . Выходы преобразователей 3 и 4 подключены к входам выходного сумматора 5, а аналоговый вход первого преобразователя 3 соединен с выходом третьего цифро-аналогового преобразователя 6, Третья группа выходов блока 2 памяти подключена к входам дешифратора 7, соединенного выходами с управляющими входами блока 8 передачи дополнительных разрядов кода. Блок 8 подключен информационными входами к входам соответствующих разрядов кода аргумента, а выходами - к входам старших разрядов третьего преобразователя 6, соединенного входами младших разрядов с входами младших разрядов кода аргумента Для промёжуТОЧНОГО хранения кода аргумента на входах кода аргумента функционального преобразователя может быть, например, включен входной регистр 9. Блок 8 передачи дополнительных разрядов кода может быть выполнен содержащим т-1 элементов ИЛИ 10, где m - максимальное количество одновременно передаваемых разрядов кода и т-групп элементов И 11 по m-i+1 элементов И в i-ой 1 группе, причем каждый j-ый t j m-i+1 элемент И 11 i-ой группы элементов И подключен первым и вторым входами соответственно к i-ому информационному и к j-ому управляющему входам блока 8. Выходы элементов И 11 i-ой группы 1- i т-1 соединены с входами i-ro элемента ИЛИ 10, выход которого является i-ым выходом блока 8, а выход элемента И 11 ш-ой группы является т-ным/ выходом блока 8 (на чертеже отображен случай построения блока 8 для ). Перед началом работы функционального преобразователя производится его программирование путем записи в блок 2 памяти кодовых значений па595раметров аппроксимации. Для этого предварительно выполняется кусочнолинейная аппроксимаций исходной функциональной зависимости. Уравнение аппроксимируюи;ей прямой на интервале Х,+(,2,3,.. . имеет вид Ч(Х)а ЪЛХ-Хк), (1) где а,, параметры аппроксимации. Для нормальной работы преобразователя в процессе аппроксимации необходимо выполнить условие, по которому длина К-го интервала должна соответCTBOBaTbAX,Xj,-X , где шаг квантования аргумента, q 1,2, 3,... Указанное условие означает, что количество интервалов разной длины может быть произвольным, однако отношение длин может быть произвольМым, однако отношение длин этих интер валов должно быть кратным степени двойки После выполнения аппроксимации выделяются группы интервалов одинаковой длины. Первую группу интервалов составляют интервалы наименьшей длиныдХ|(. Вторую группу составляют интервалы, у которых длина равна . Если таких интервалов не окажется, но вторую группу будут образовывать интервалы длиной и т.д. Последнюю группу образуют интервалы наибольшей длины . Каждая из полученных групп ставится в соответствии двоичный код номера группы, разрядность которого определяется числом различных- групп интервалов. Далее в каждую ячейку блока 2 памяти, соответствующую определенному интервалу аппроксимации, записываются кодовые значения параметров а| и ty, а также код номера группы интервалов, к которой принадлежит данный интервал аппроксимации. Работа функционального преобразова теля .начинается с подачи на его входы (на входной регистр 9) кода аргуме нта. 1Ъсле обращения к блоку 2 памя ти со стороны блока 1 адресации происходит считывание содержимого соответствующей ячейки памяти блока 2, после чего код величины Ь поступает на цифровые входы преобразователя 3, код Эц - на цифровые входы преобра...„ .. -. ., „-. зователя Ц, а код номере группы интер валов - на дешифратор 7, управляю1ДИЙ работой блока 8 передачи дополнительных разрядов кода. Преобразовател 26 6 имеет q разрядных входов, из которых q входов младших разрядов подключены непосредственно к входам младших разрядов кода аргумента (регистра 9), а остальные дов старших разрядов могут быть частично или полностью подключены к соответствующим разрядам кода аргумента через блок 8 передачи дополнительных разрядов кода. В зависимости от значения кода номера группы интервалов аппроксимации, дешифру- емого дешифратором 7 блок 8 не подключает (для первой группы интервалов), либо подключает к входам разрядов преобразователя 6 определенное число дополнительных разрядов аргумента. Так, например, если возбуждающий сигнал от дешифратора 7 пода тся на первый управляющий вход блока 8, то в блоке 8 через первые элементы И 11 всех т-групп элементов И и соответствующие им элементы ИЛИ 10 передаются на входы старших разрядов преобразователя 6 значения всех дополнительных разрядов кода агрумента, а если сигнал подается на т-ный управляющий вход блока 8, то этим сигналом открывеется толькогп-ный элемент И 11 первой группы элементов И и на вход преобразователя 6 через блок 8 передается значение только одного дополнительного разряда Напряжение на выходе преобразователя 6, воспроизводящее приращение аргумента X с помощью преобразователя 3 умножается на bk и суммируется на выходном сумматоре 5 с выходным сигналом преобразователя , в результате чего на выходе функционального преобразователя воспроизводится функция (11 Использование в предлагаемом функциональном преобразователе блока передачи дополнительных разрядов кода и дешифратора, при подключении младших разрядов третьего цифроаналогового преобразователя непосредственно к входам младших разрядов кода аргумента, позволяет упростить техническую реализацию функционального преобразователя по сравнению с известным за счет соответствующего упрощения реглизации блока адресации и третьего цифро-аналогового преобразователя и исключения блока формирования приращений аргумента при сохранении заданной точности функционального

Авторы

Даты

1982-08-15—Публикация

1980-09-12—Подача