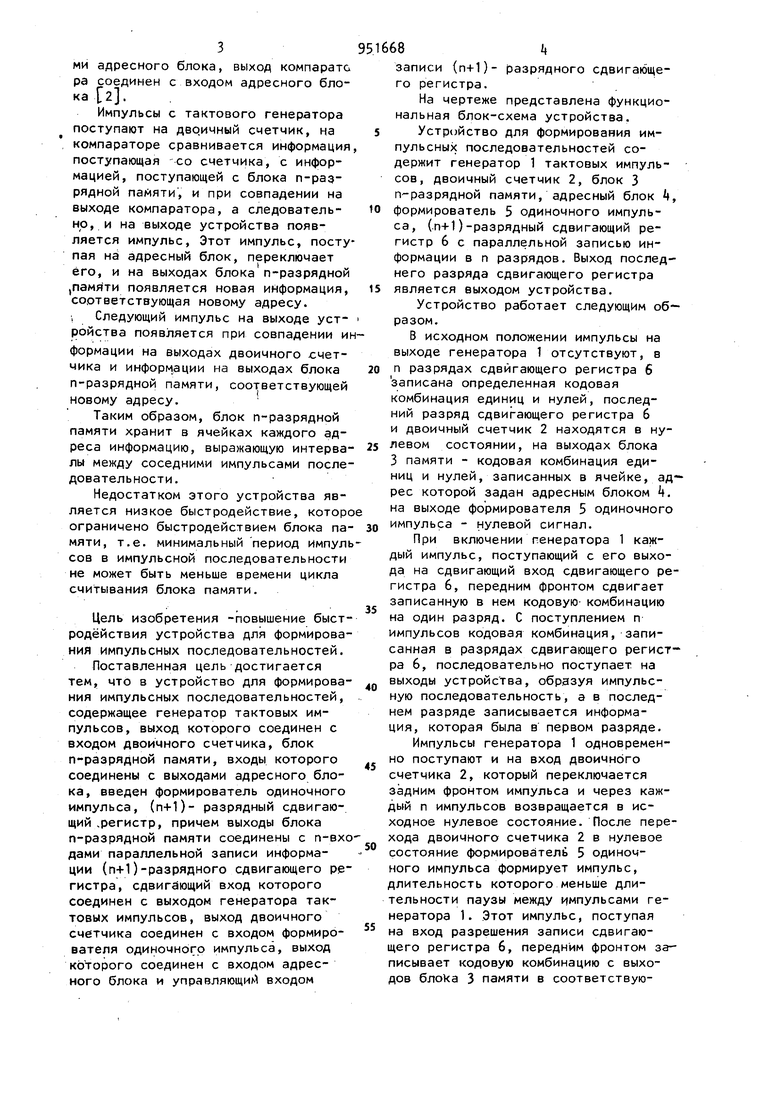

(5А) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ Изобретение относится к импульсной технике, в частности к генераторам, вырабатывающим серии импульсов, и может быть использовано в устройствах автоматики, в системах контроля цифровых электронных схем и т.д. Известно устройство для формирования импульсных последовательностей, содержащее тактовый генератор, декадный счетчик; пШоков элементов совпадений,блок сравнения кодов.,прог раммный блок (блок памяти),распреде тель импульсов вспомогательный счетчик, триггер, блок добавления импульса и элемент ИЛИ l J. В этом устройстве при каждом сов падении состояния младшей декады счетчика с младшей цифрой программного блока блок сравнения кодов осуществляет поразрядное сравнение состояния всех декад с заданными программынм блоком значениями. Сигнал на выходе устройства появляется ТОЛЬКО в случае совпадения состояния кодов всех декад с заданными программным блоком значениями. Под воздействием выходного импульса в программном блоке вырабатывается следующий код. Однако данное устройство обладает низким быстродействием, ограниченным быстродействием программного блока (блока памяти), так как минимальный период импульсов в импульсной последовательности не может быть меньше времени цикла считывания блока памяти. Наиболее близко к предложенному, устройство для формирования импульсных последовательностей, в котором выход тактового генератора соединен с входом двоичного счетчика, выходы которого соединены с первыми входами компаратора, вторые входьЗ компаратора соединены с выходами блока п-разрядной памяти, адресные ;входы которой соединены с выходами адресного блока, выход компарато ра соединен с входом адресного блока 2. Импульсы с тактового генератора поступают на двричный счетчик, на , компараторе сравнивается информация поступающая со счетчика, с информацией, поступающей с блока п-разрядной памяти, и при совпадении на выходе компаратора, а следовательно, и на выходе устройства появляется импульс. Этот импульс, посту пая на адресный блок, переключает его, и на выходах блока п-разрядной ,памяти появляется новая информация, соответствующая новому адресу. , Следующий импульс на выходе устройства появляется при совпадении и формации на выходах двоичного счетчика и информации на выходах блока п-разрядной памяти, соответствующей новому адресу. Таким образом, блок п-разрядной памяти хранит в ячейках каждого адреса информацию, выражающую интерва лы между соседними импульсами после довательности. Недостатком этого устройства является низкое быстродействие, котор ограничено быстродействием блока па мяти, т.е. минимальный период импул сов в импульсной последовательности не может быть меньше времени цикла считывания блока памяти. Цель изобретения -повышение быст родействия устройства для формирова ния импульсных последовательностей. Поставленная цель достигается тем, что в устройство для формирова ния импульсных последовательностей, содержащее генератор тактовых импульсов, выход которого соединен с входом двоичного счетчика, блок п-разрядной памяти, входы которого соединены с выходами адресного блока, введен формирователь одиночного импульса, (п+1)- разрядный сдвигающий .регистр, причем выходы блока п-разрядной памяти соединены с п-вх дами параллельной записи информации (п+1)-разрядного сдвигающего ре гистра, сдвигающий вход которого соединен с выходом генератора тактовых импульсов, выход двоичного счетчика соединен с входом формирователя одиночного импульса, выход которого соединен с входом адресного блока и управляющий входом записи (п+1)- разрядного сдвигающего регистра. На чертеже представлена функциональная блок-схема устройства. Устройство для формирования импульсных последовательностей содержит генератор 1 тактовых импульсов, двоичный счетчик 2, блок 3 п-разрядной памяти, адресный блок Ц, формирователь 5 одиночного импульса, (.п+1)-разрядный сдвигающий регистр 6 с параллельной записью информации в п разрядов. Выход последнего разряда сдвигающего регистра является выходом устройства. Устройство работает следующим об разом. В исходном положении импульсы на выходе генератора 1 отсутствуют, в п разрядах сдвигающего регистра 6 записана определенная кодовая комбинация единиц и нулей, последний разряд сдвигающего регистра 6 и двоичный счетчик 2 находятся в нулевом состоянии, на выходах блока 3 памяти - кодовая комбинация единиц и нулей, записанных в ячейке, ад-рее которой задан адресным блоком k. на выходе формирователя 5 одиночного импульса - нулевой сигнал. При включении генератора 1 каждый импульс, поступающий с его выхода на сдвигающий вход сдвигающего регистра 6, передним фронтом сдвигает записанную в нем кодовую комбинацию на один разряд. С поступлением п импульсов кодовая комбинация, записанная в разрядах сдвигающего регистра 6, последовательно поступает на выходы устройства, образуя импульсную последовательность, а в последнем разряде записывается информация, которая была в первом разряде. Импульсы генератора 1 одновременно поступают и на вход двоичного счетчика 2, который переключается задним фронтом импульса и через каждый п импульсов возвращается в исходное нулевое состояние. После перехода двоичного счетчика 2 в нулевое состояние формирователь 5 одиночного импульса формирует импульс, длительность которого меньше длительности паузы между импульсами генератора 1. Этот импульс, поступая на вход разрешения записи сдвигающего регистра 6, передним фронтом записывает кодовую комбинацию с выходов блока 3 памяти в соответствующие разряды сдвигающего регистра 6 и, поступая одновременно на вход адресного блока ,задним фронтом переключает его на новый адрес. Таким образом, в паузе между дв мя импульсами генератора 1 в п ра рядов сдвигающего регистра 6 запис вается кодовая комбинация с выходо блока 3-памяти, и адресный блок k мирует адрес новой ячейки 3 памяти а кодовая комбинация, записанная в этой ячейке, появляется на выходах блока 3 памяти чере время, определяемое его быстродействием, С поступлением следующей серии п импульсов процесс повторяется. К моменту записи новой кодовой комбинации в сдвигающий регистр 6 на выходах блока 3 памяти устанавливается новая кодовая комбина ция, записанная в ячейках, адрес ко торых выбран адресным блоком k в предыдущем цикле. Количество разрядов сдвигающего 1 регистра 6 и блока 3 памяти должно Ьыть таким, чтобы при необходимой . частоте тактового генератора 1 время, в течение которого кодовая комбинация со сдвигающего регистра 6 передается на выход устройства, был больше, чем время цикла считывания блока 3 памяти. В общем случае минимальный перио выходных импульсов Т равен 2Ti w , время цикла считывания блока памяти;. период импульсов тактового генератора; количество разрядов регистра 6 и блока 3 памяти. Таким образом, для получения необходимого быстродействия, т.е. минимального периода выходных импульсов, при иcпoльзoвaнi1и блока 3 памяти с любым быстродействием колимество разрядов блока 3 памяти и сдвигающего регистра 6 и период им пульсов генератора 1 равны т Твых Тг -J- . . При и .более быстродействие устройства превышает быстродействие блока 3 памяти. Так как быстродействие блоков па мяти за смет сложности внутренней 686 структуры ограничено, а быстродействие сдвигающих регистров 6 может быть достаточно высоким, то применение в устройстве (п+1)-разрядного сдвигающего регистра, в п разрядов которого производится параллельная запись информации с выходов блока п-разрядной памяти, а потом происхо, дит последовательная передача этой информации на выход устройства, позволяет получить быстродействие устройства не зависимо от быстродействия блока памяти. Использование в сдвигающем регистре (п+1) разрядов, в последний из которых не записывается информация с блока памяти, позволяет исключить разрывы между группами импульсов в импульсной последовательности, а запись единичного или нулевого сигнала в несколько смежных разрядов сдвигающего регистра позволяет получить начВыходе устройства импульсные последовательности с импульсами и паузами различной длины. При этом максимальная длительность цикла импульсной последовательности опреде1ляется емкостью блока памяти. Формула изобретения Устройство для формирования импульсных последовательностей, содержащее генератор тактовых импульсов, выход которого соединен с входом двоичного счетчика, блок п-раз-. рядной памяти, входы которого соединены с выходами адресного блока, отличающееся тем, что, с целью повышения быстродействия, в него введен формирователь одиночного импульса, (п+1)-разрядный сдвигающий регистр, причем выходы блока п-разрядной памяти соединены с п.входами параллельной записи информа:ции (п+1)- разрядного сдвигающего регистра, сдвигающий вход которого соединен с выходом генератора тактовых импульсов, выход двоичного счетника соединен с входом формирователя одиночного импульса, выход которого соединен с входом адресного блока, и управляющим входом записи (п+1)- разрядного сдвигающего регистра. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 6б9478,кл, Н 03 К 3/72, 19772.Патент ФРГ № 2 +55039, л. Н 03 К З/б, опублик. 1975.

- -

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО | 1990 |

|

RU2007866C1 |

| Декодирующее устройство | 1990 |

|

SU1783626A1 |

| Устройство для исправления ошибок | 1985 |

|

SU1327297A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Цифровой фильтр с дельта-модуляцией | 1988 |

|

SU1527713A1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| Формирователь импульсных последовательностей | 1988 |

|

SU1539973A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| Дешифратор времяимпульсных кодов | 1987 |

|

SU1462307A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

Авторы

Даты

1982-08-15—Публикация

1980-07-09—Подача