4 Од

СО

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор времяимпульсных кодов | 1989 |

|

SU1646058A1 |

| Дешифратор времяимпульсных кодов | 1989 |

|

SU1736004A1 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

| Устройство декодирования тональных сигналов | 1988 |

|

SU1570034A1 |

| Мажоритарное декодирующее устройство | 1987 |

|

SU1471313A1 |

| Устройство для мажоритарного декодирования | 1987 |

|

SU1517137A1 |

| Мажоритарное декодирующее устройство | 1986 |

|

SU1372627A1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ ИМПУЛЬСНО-ВРЕМЕННЫХ СИГНАЛОВ | 1990 |

|

RU2028732C1 |

| Устройство для медианной фильтрации двумерных массивов | 1987 |

|

SU1524067A1 |

| УСТРОЙСТВО ДЛЯ СИНТЕЗА РЕЧЕВЫХ СИГНАЛОВ | 1991 |

|

RU2020608C1 |

Изобретение относится к импульсной технике и может использоваться в системах встроенного контроля. Цель изобретения - повышение быстродействия дешифратора. Дешифратор осуществляет дещифрирование времяимпульс- ных кодов, поступающих на D-вход триггера 2. Длина кодовой комбинации задается числом, поступаня 1им на D-входы счетчика 5, и соответствует группе, номер которой устанавливается на входах блока 8 постоянной памяти, что повьппает быстродействие декодера. Декодер содержит генератор 1 тактовых импульсов, триггеры 2,3, элемент И 4, счетчик 5, элементы НЕ 6,7, блок 8 постоянной памяти, регистр 9 и шину 10 нулевого потешща- ла. 3 ил. о $

0(/е.Г

Изобретение относится к импульс- йой технике и может использоваться в Системах встроенного контроля.

Целью изобретения является повышение быстродействия дешифратора.

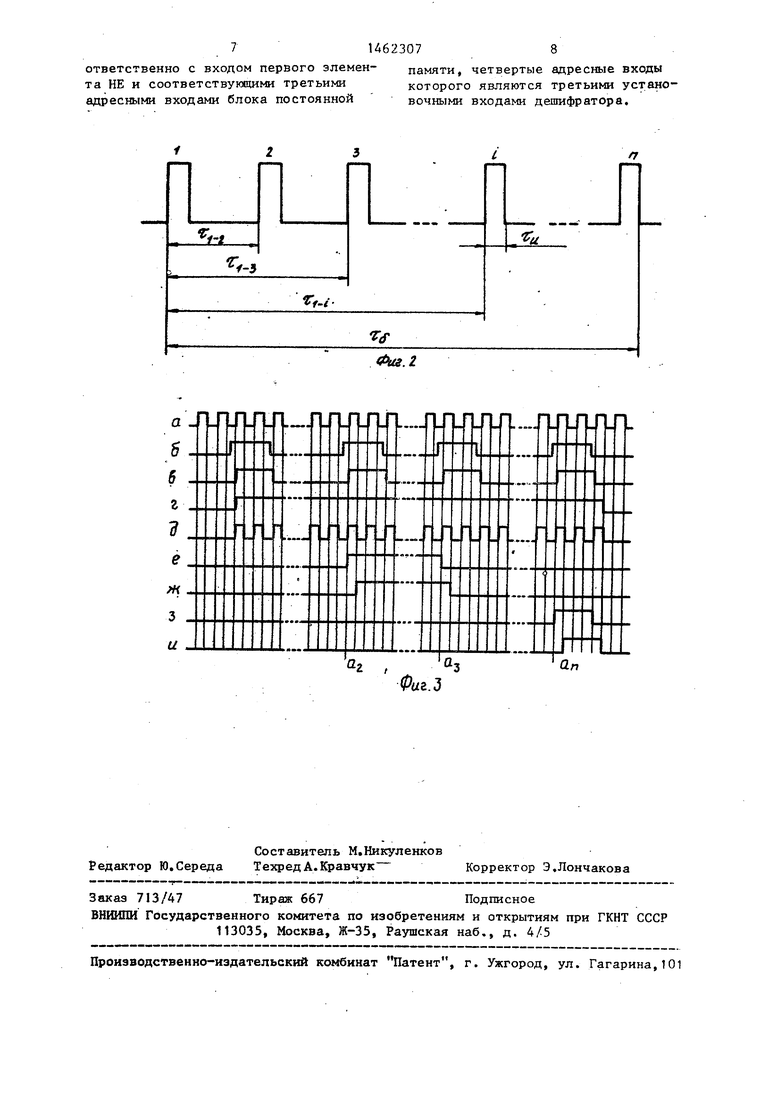

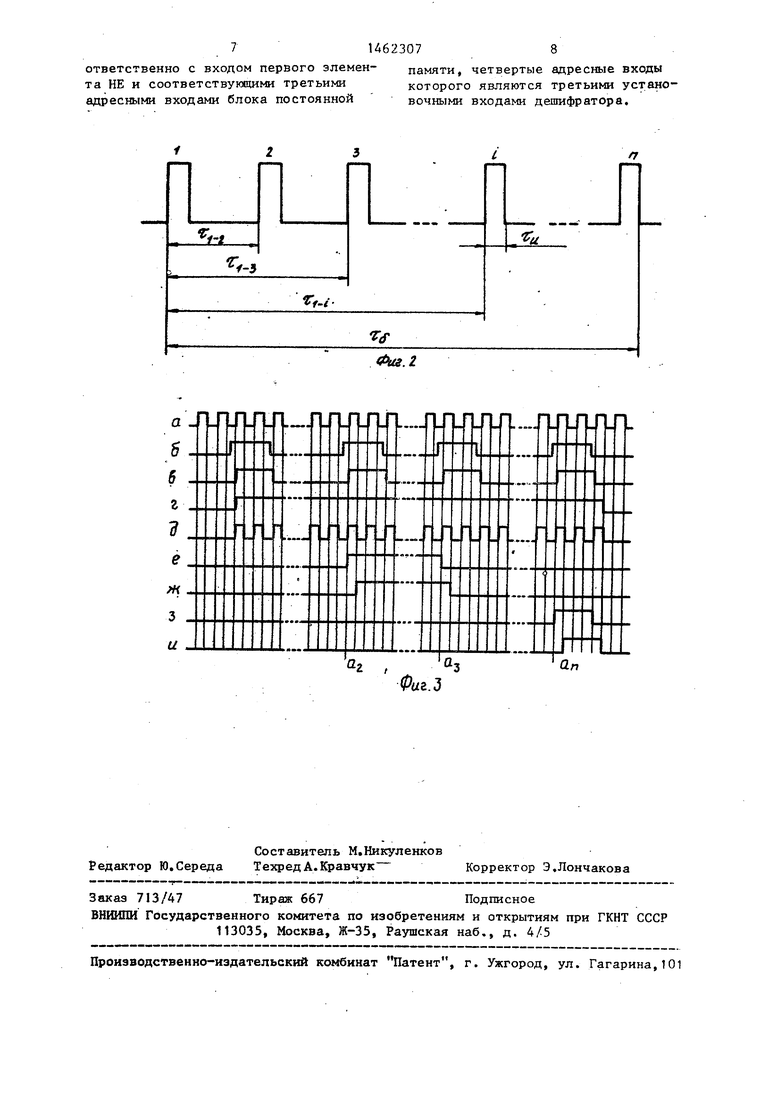

На фиг.1 представлена функциональная схема предлагаемого дешифратора йа фиг.2 - декодируемая кодовая груп ijia из п импульсов, где€;., - время

1|1ежду первым и i импульсами, ,п; Гц - длительность импульса; - вре фенная база кодовой группы; на фиг.З : ременные диаграммы, поясняющие ра- фоту дешифратора.

Дешифратор времяимпульсных кодов | фиг.1) .содержит генератор 1 такто- )ых импульсов, второй, первый D-триг 1 еры 2 и 3, элемент И А, счетчик 5, первый и второй элементы.НЕ 6 и 7, «шок 8 постоянной памяти, регистр 9 параллельной записи и шину 10 нулево to потенциала.

: На тактовый вход счетчика 5 пос- fynajoT тактовые импульсы генератора I с периодом, удовлетворяющим условию

.

На второй установочный вход пода- ется в двоичном коде целочисленное Значение длительности временной базы (фиг. 2) декодируемой группы

/.

. . .N -рГ 7

о

где N величина предустановки счетчика 5 в де сятичной форме.

Дешифратор работает следующим образом.

Импульс, -поступаюпдай на вход на- чальной установки дешифратора, подается на R-вход триггера 3 и устанавливает его в нулевое состояние. Нулевой потенциал с выхода триггера 3 .(фиг.Зг) поступает на вход элемента И 4, запрещая прохождение тактовых импульсов на вход счетчика 5, Кроме того, нулевой потенциал с выхода Триггера 3 поступает на вход управления счетчика 5, устанавливая его :а состояние, соответствунндее временной базе декодируемой кодовой группы целочисленное значение которой поступает на второй установочный вход дешифратора.

Первый импульс декодируемой группы (фиг.,36) поступает на D-вход триггера 2, на С-вход которого поступают тактовые импульсы (фиг.За) с

ю

15

20

25

30

35

40 45 -

5

выхода генератора 1. На выходе триггера 2 передний и задний фронты импульса декодируемой группы будут появляться по переднему фронту такто- вых импульсов при соответственно-наличии и отсутствии импульсов декодируемой группы на D-входе (фиг.Зв).

Первый синхронизированный импульс декодируемой группы (фиг.Зв) с выхода триггера 2 поступает на вход триггера 3 и устанавливает его в единич- ное состояние (фиг.Зг). Единичньй потенциал с выхода триггера 3 разрешает прохождение тактовых импульсов через элемент И 4 на тактовый вход вычитания счетчика 5 (фиг.Зд) Этот же единичньй- потенциал поступает на вход управления счетчика 5 и разрешает счет. Синхронизированный импульс декодируемой группы поступает на вход КИ блока 8, модифицируя адрес.

Под действием тактовых импульсов, поступаюпдах на тактовый вход вычитания, счетчик 5 формирует убыванщую последовательность aj, поступающую на входы А блока 8. Длительность адресной последовательности тождественна дпительности базы кодовой группы Пои поступлении второго импульса (фиг.За) на вход КИ блока 8, с выходов счетчика 5 на входы А блока 8 поступает текущий адрес a,j., соответствующий временному интервалу,2 (фиг.2) в двоичном представлении;

.-

где N - количество ПОСТУПИВШ.ИХ на

счетчик 5 тактовых импуль сов.

в блоке 8 предварительно записа- с на информация о временном положении . импульсов декодируемой группы в пределах % этой группы. На входы А дд блока. 8 поступает код выбора текущей кодовой расстановки с|код который определяет ту .область памяти блока 8, в которой хранится информация о временном положений, импульсов декодируемой группы.

Таким образом, полный адрес, поступающий на адресные входы блока 8,, имеет вид

А в., Is 5 Р{,...,0б

По этому адресу в блоке 8 хранится признак декодирования второго импульса кодовой группы в разряде Р, ячейки памяти (фиг.Зе).

Выходы признаков декодирования очередного импульса Р, ,... ,Ргу,4-е по цепи обратной связи через регистр 9 соединены с адресными входами блока 8.

В пределах текущего адреса а через 1/2 б по переднему фронту импульса, поступающего с выхода элемента НЕ 7, информация с выхода блока 8 (фиг.Зе) запишется в регистр 9 (фиг.Зж), в результате чего произойдет модификация полного адреса блока 8, который примет вид

(124-1

а,..1.

10,...,0,

где о - длительность такта

Предварительно в блоке 8 в ячейках, в адресе которых разряд А. для конкретной кодовой группы установлен в единицу, записана единица в разряде РП, .

Появление единицы в разряде Р., блока 8 (фиг.Зе) означает декодирование второго импульса кодовой группы и переход в область памяти блока 8, имеющей единицу в разряде ., адреса.

В момент прихода третьего импульса декодируемой кодовой группы ((иг.Зв) на вход КИ блока 8, с выходов счетчика 5 на адресные входы А поступает текущий адрес а, соот- .ветствующий временному интервалу € ,(фиг.2) в двоичном представлении

1-3 N3; а, N,.

Таким образом, полный адрес, пос- тупаюпщй на адресные входы блока 8 имеет вид

П

Э

1, а.., 10,... ,0.

По этому адресу в блоке 8 хранится признак декодирования третьего импульса кодовой группы в разряде ячейки памяти.

В пределах текущего адреса а че- рез /2 С по переднему фронту импульса, поступакодего с выхода элемента НЕ 7 информация с выхода блока 8 запишется в регистр 9, в результа- те чего- произойдет модиЛикация полного адреса, который примет вид

а,010,.,.,0.

62307

Предварительно в блоке 8 в ячейках, в адресе которых разряд А. для конкретной кодовой группы установлен в единицу, записана единица в разряде Р,

Появление единицы в разряде . блока 8 означает декодирование треть- го импульса кодовой группы (фиг,36) и переход в область памяти блока 8,

10

имекщей единицу в разряде А . , адреса.

В момент прихода i-ro импульса декодируемой кодовой группы на вход КИ блока 8, с выходов счетчика 5 на адресные входы А блока 8 поступает текущий адрес а, соответствующий временному интервалу с,, двоичном представлении

5N, :

(фиг.2) в

е-.

N;

25

Таким образом, полный адрес, поступающий на адресные входы блока 8 имеет вид

Я

1

а,

(i-2) 0,...,0

где (i-2).g| - число (i-2) в двоичном

представлении.

По этому адресу в блоке 8 хранится признак декодирования i-ro импульса кодовой группы в виде числа F i-1 в двоичном представлении в § разрядах разрядной области ОС блока 8, где S - наибольшее целое число, еньшее или равное logj,()

ffS.

к

(1-2)дв Оо F

В пределах текущего адреса а- через /2Z по переднему фронту импульса, поступающего с выхода элемента НЕ 7, информация с выхода блока 8 запишется в регистр 9, в результате чего произойдет модификация полного адреса блока 8, который примет следуюпщй вид:

1, a,(i-l) 0,...,0.

Предварительно в блоке 8 в ячейках, имеющих в разрядах А K+I ,.. , адреса двоичное число (i-l)Аазаписа- но число (1-1)дв в разрядах Р, , , Рт+5

Р, ,..., а;,1, а, (i-l)gO,.. .о| F.

Таким образом, наличие числа (I-OAB разрядах разрядной области ОС блока 8 означает декодирование i-ro импульса кодовой группы и переход в область памяти, имеющей число (1-)дц в S разрядах адрес- ной области 3 блока 8,

В прихода п-го (последнего) импульса декодируемой группы : на вход КИ блока 8-, с выходов счет- iчика 5 на адресные входы А блока 8 поступает текущий адрес а , соответствующий временному интервалу С,,, в двоичном представлении

N,;;

N.

а

: где N - количество поступивпшх на ;счетчик 5 тактовых импульсов.

; Таким образом, на адресные входы блока 8 поступает адрес

п

l,(i-2).-0,....0.

АВ

По адресу в блоке 8 хранится декодирование кодовой группы в виде единицы в Р; разряде блока 8,

.Появление единицы в Р- разряде блока 8 (фиг.Зз) означает декодирование кодовой группы,

В гфеделах текущего адреса а через /2 по переднему фронту импульса, поступающего с выхода элемента НЕ 7, информация о декодировании кодовой группы запишется в регистр 9 (фиг.Зи) и поступит на выход дешифратора.

Если не будет декодирован хотя бы один следующий после первого импульс декодируемой кодовой группы, то не будет декодирована вся кодовая группа, так как не будет произведен переход на соответствующую этому им пульсу область памяти блока 8.

По истечении времени C g на синх- ровход счетчика 5 поступит Н„ импульсов, что вызовет появление по заднему фронту тактового импульса отрицательного импульса переполнения на первом выходе счетчика 5. Этот импульс через элемент НЕ 6 поступает на С-вход триггера 3, D-вход которого соединен с шиной нулевого потенциала.

gПо переднему фронту импульса, снимаемого с выхода элемента НЕ 6, триггер 3 устанавливается в нулевое состояние и запрещает прохождение тактовых импульсов от генератора 1 че10 рез элемент. И 4 на вход счетчика 5. Кроме того, нулевой потенциал с выхода триггера 3, поступая на вход управления счетчика 5, вызывает его предустановку. Дешифратор устанавли15 вается в состояние ожидания прихода первого импульса очередной декодируемой группы.

Формула изобретения

20

Дешифратор времяимпульсных кодов, содержащий первый элемент НЕ, выход которого соединен с тактовым входом первого триггера, блок постоянной

25 памяти, выходы которого соединены с одноименными информационными входами регистра, первый и вторые выходы котород-о соответственно соединены с первым адресным входом лока постоян30 ной памяти и являются выходами дешифратора, генератор тактовых импульсов и шину нулевого потенциалЯр отличающийся тем, что,, с целью повышения быстродействия дешифрато2g pa, в него введены второй триггерj элемент И, счетчик и второй элемент НЕ, выход генератора тактовых импульсов соединен с первым входом элемента И и тактовым вх.одом второго триг4Q гера, информационный вход которого является информационным входом дешифратора, выход второго триггерам соединен с вторым адресным входом блока постоянной памяти и входом уста45 новки в единицу первого триггера, вход установки в ноль и информационный вход которого соответственно подключены к первому установочному входу дешифратора и к шине нулевого

gQ потенциала, выход первого триггера соединен с управляющим входом счетчика и вторым входом элемента И, выход которого соединен -непосредственно с тактовым входом счетчика и чеgg рез второй элемент НЕ с тактовым входом регистра, информационные входы счет чика являются вторыми установоч-vl ными входами дешифратора, первый и . вторые выходы счетчика соединены со71462307

ответственно с входом первого элемента НЕ и соответствующими третьими адресными входами блока постоянной

па ко во

1-1

5 5

е

т

ъ

и.

8

памяти, четвертые адресные входы которого являются третьими установочными входами дешифратора.

Й

Фиг. г

di

Фиг.д

йп

| Дешифратор интервально-временных сигналов | 1983 |

|

SU1120485A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство управления | 1983 |

|

SU1126953A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-02-28—Публикация

1987-08-11—Подача