Изобретение относится к автоматике и может быть использовано в аналоговых вычислительных системах и устройствах.

Известны операционные усилители (ОУ), содержащие суммирующий выходной каскад, входные и выходные транзисторы, генератор тока, с помощью которых осуществляется следящая связь по синфазной составляющей сигнала }1 .

Недостатком таких ОУ является невысокое быстродействие.

Наиболее близким к изобретению является ОУ, содержащий суммирующий выходной каскад с двумя входами, два входных усилительных транзистора, . эмиттеры которых подключены к выходу генаратора тока, первый и второй выходные усилительные транзисторы, базы которых соединены между собой, а эмиттеры подключены к коллекторам соответствующих входных усилительных транзисторов, первый и второй полевые усилительные транзисторы, затворы которых соединены с соответствующими базами входных усилительных транзисторов и образуют входы операционного усилителя, первый блок нагрузки, подключенный к стокам полевых усилительных транзисторов, второй, блок нагрузки, подключенный к коллекторам выходных усилительных транзисторов, коллектор второго из которых соединен с первым входом суммирующего каскада 2.

Недостатком этого ОУ является сравнительно невысокая скорость нарастания выходного напряжения, ограниченная величиной

V , ff-p - частота среза ОУ;

где

и - напряжение ограничения

входного каскада. Целью изобретения является повышение быстродействия и упрощение операционного усилителя.

Поставленная цель достигается тем, что в усилителе истоки полевых усилительных транзисторов соединены с базами выходных усилительных транзисторов, а второй вход суммирующего каскада подключен к стоку второго полевого усилительного транзистора.

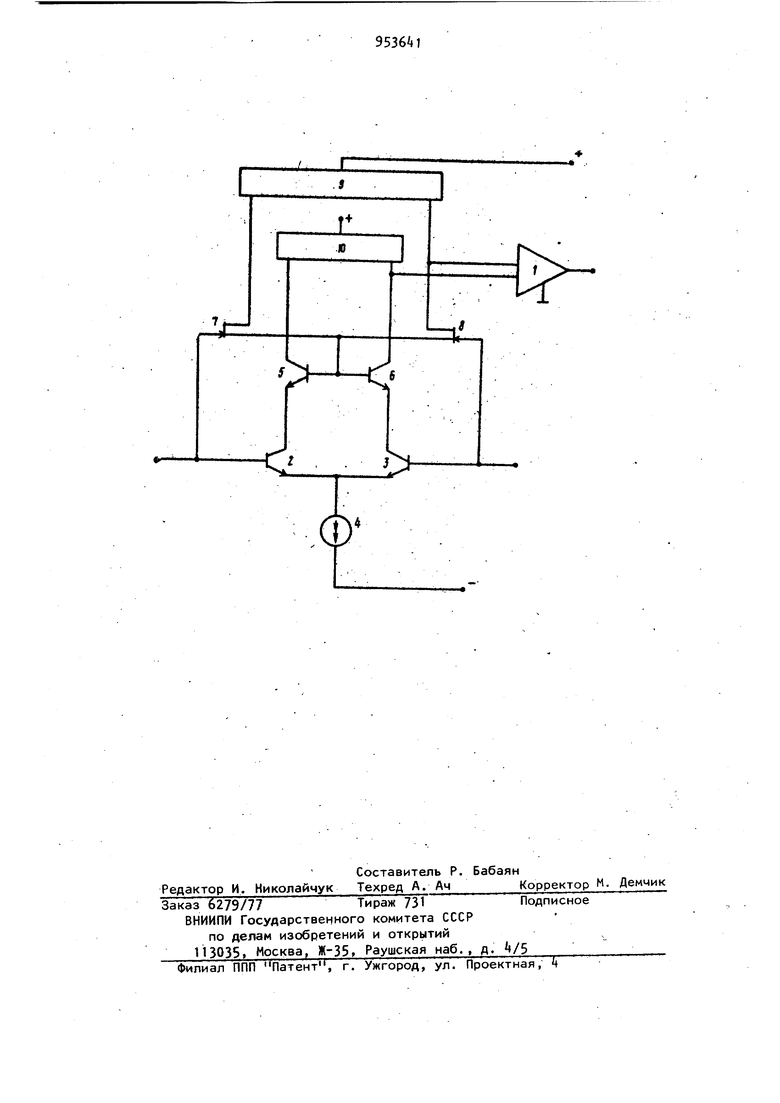

На чертеже приведена схема ОУ.

Усилитель содержит двухвходовой суммирующий каскад 1, два входных усилительных транзистора 2 и 3 эмит теры которых подключены к генератору k тока, два выходных усилительных транзистора 5 и 6, базы которых соединены между собой, а эмиттеры подключены к коллекторам соответствующих входных усилительных транзисторов, два полевых усилительных транзистора 7 и 8, затворы которых соединены с соответствующими базами входных транзисторов и образуют входы ОУ, первый блок 9 нагрузки в цепях стоков полевых усилительных транзисторов, второй блок 10 нагрузки в коллекторных цепях выходных усилительных транзисторов, коллектор второго из которых.соединен с первым входом суммирующего каскада.

Усилитель работает следующим образом.

При подаче перепада напряжения на вход ОУ выходное напряжение блока 10 нарастает с небольшой скорост тью, так же, как в известных ОУ. Однако напряжение на выходе блока 9 нарастает со значительно большей скоростью, поскольку полевые транзисторы обладают значительно лучшим отношением выходного тока к крутизне, чем биполярные транзисторы. Поэтому в начале переходного процесса напряжение на выходе суммирующего каскада 1 определяется более быстродействующим каскадом йа полевых транзисторах 7 и 8. После этого успевает нарасти напряжение на выходе блока 10, и напряжение на выходе суммирующего каскада 1 определяется каскадом на биполярных транзисторах 2 и 3.

Таким образом, в предлагаемом операционном усилителе при малом напряжении смещения нуля, характерном для входных каскадов ОУ на биполярных транзисторах, достигается высокая скорость нарастания, такая же, как. в усилителях на полевых транзисторах.

Формула изобретения

Операционный усилитель, содержащий двухвходовой суммирующий каскад,

5 два входных усилительных транзисто ра, эмиттеры которых подключены к выходу генератора тока, первый и второй выходные усилительные транзисторы, базы которых соединены между

0 собой, а эмиттеры подключены к коллекторам соответствующих входных усилительных транзисторов, первый и второй полевые усилительные транзисторы, затворы которых соединены

с соответствующими базами входных усилительных транзисторов и образуют входы операционного усилителя, первый блок нагрузки подключен к стокам полевых усилительных транзисторов,

второй блок нагрузки - к коллекторам выходых усилительных транзисторов, коллектор второго из которых соединен с первым входом суммирующего каскада, отличающийся тем, что, с целью повышения быстродействия и упрощения операционного усилителя, в нем-истоки полевых усилительных транзисторов соединены с базами выходных усилительных транзисторов, а второй вход суммирующего каскада подключен к стоку второго полевого усилительного транзистора.

Источники информации, принятые во внимание при экспертизе

1.-Linear integrated circuit D.A.T.A. Book, D.A.T.A, Inc A. Cordura Company. USA, 197, Model

LM 108.A.

2.Патент Великобритании № 12123 2, кл. Н 3 Т (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизатор напряжения | 2023 |

|

RU2795284C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2015 |

|

RU2595923C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2016 |

|

RU2642337C1 |

| Арсенид-галлиевый операционный усилитель на p-n-p биполярных и полевых транзисторах с управляющим p-n переходом | 2023 |

|

RU2813281C1 |

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| ВЫХОДНОЙ КАСКАД BIJFET ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2017 |

|

RU2668981C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2015 |

|

RU2613842C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2615066C1 |

| Арсенид-галлиевый операционный усилитель | 2023 |

|

RU2813140C1 |

| НЕИНВЕРТИРУЮЩИЙ ВЫХОДНОЙ КАСКАД АРСЕНИД-ГАЛЛИЕВОГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2784049C1 |

L

Авторы

Даты

1982-08-23—Публикация

1980-12-15—Подача