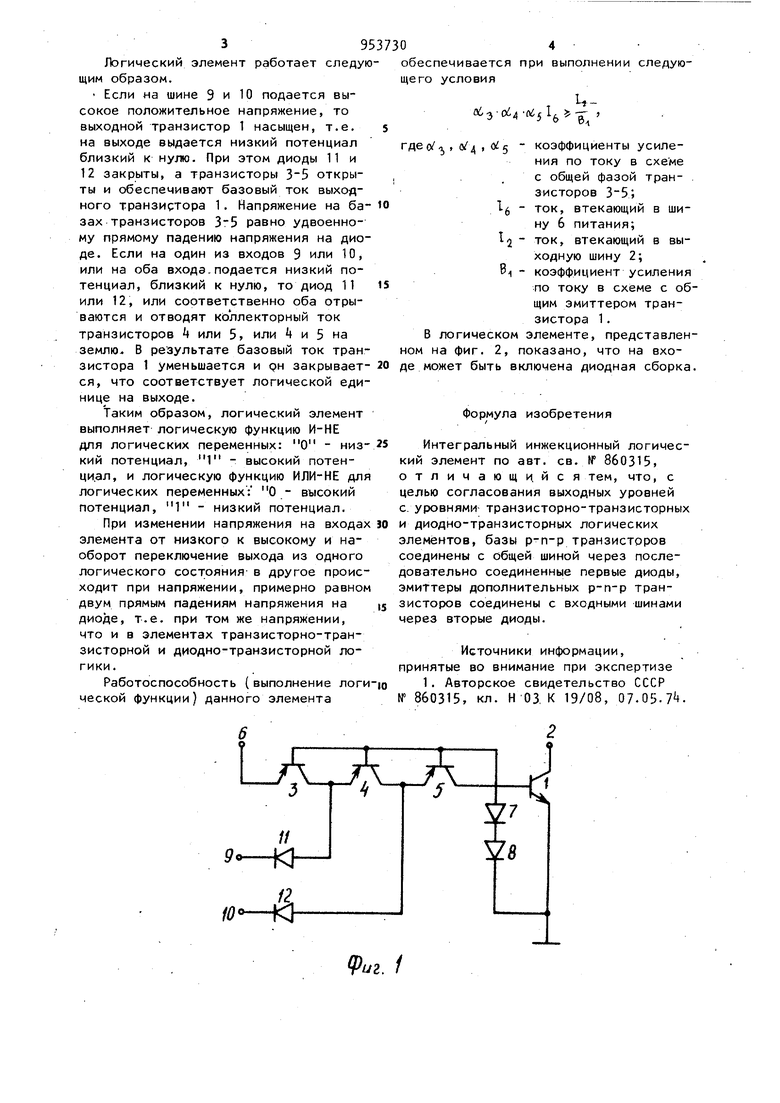

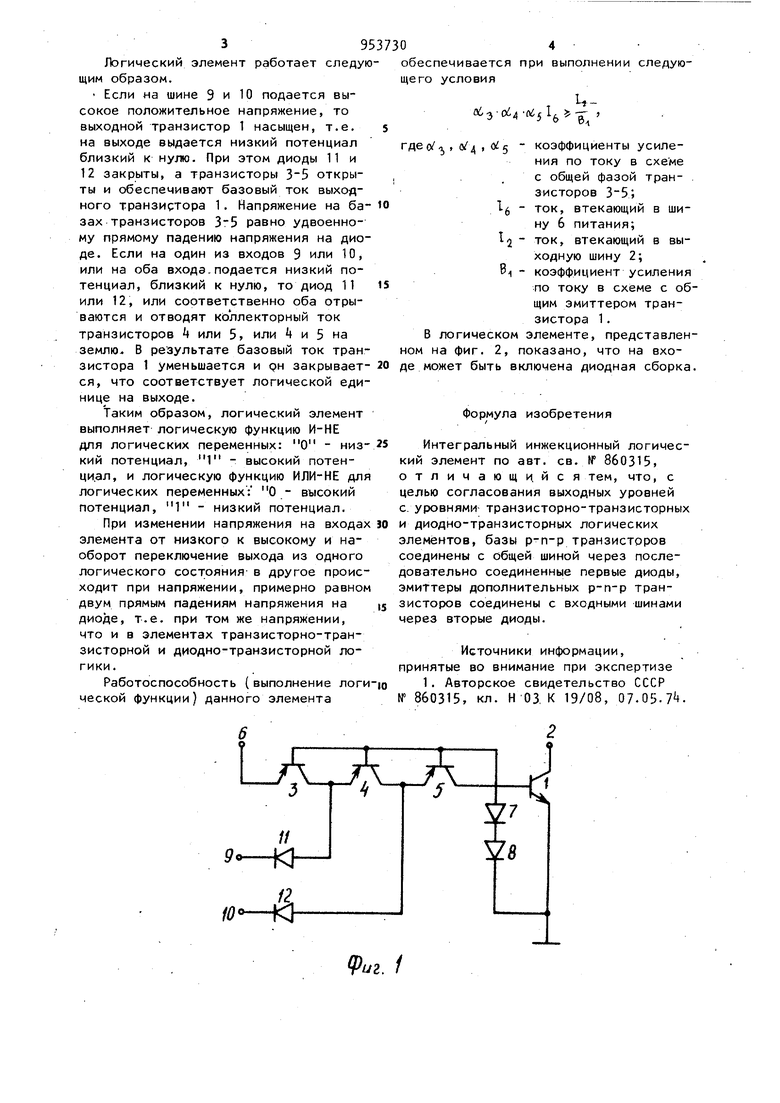

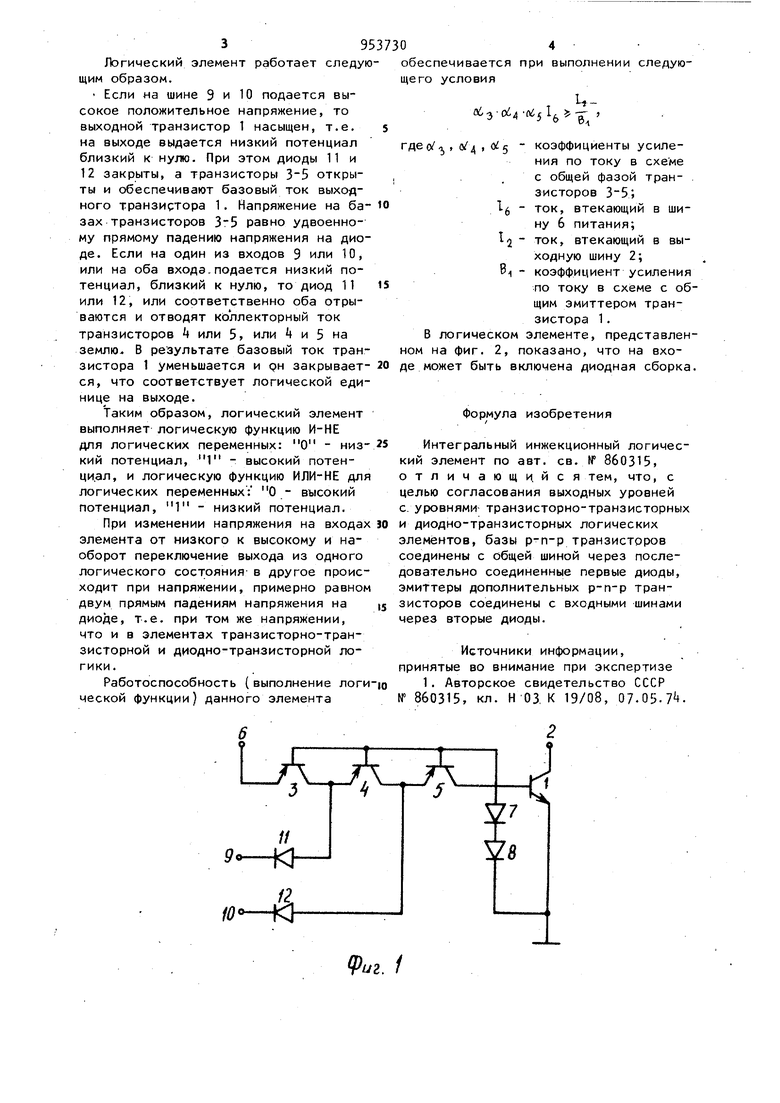

Изобретение относится к логическим и запоминающим устройствам и может найти широкое применение в разли ных устройствах автоматики и вычисли тельной техники. По основному авт. св. N 860315 известен интегральный инжекционный логический элемент, содержащий интек тируюций, выходной и дополнительные транзисторы l . Недостатком известного логическог элемента является отсутствие согласо вания его выходных уровней с уровням транзисторно-транзисторных логически элементов. Целью изобретения является соглас вание выходных уровней с уровнями транзисторно-транзисторных и диоднотранзисторных логических элементов. Поставленная цель достигается тем, что в интегральном инжекционном логическом элементе базы инжектирующего и дополнительных р-п-р транзисторов соединены с общей шиной через последовательно соединенные первые диоды, эмиттеры дополнительных р-п-р транзисторов соединены с входными шинами через вторые диоды. На фиг. 1 приведена электрическая схема интегрального инжекционного логического элемента; на фиг. 2 вариант его выполнения. Логический элемент содержит выходной п-р-р транзистор 1, эмиттер которого соединен с общей шиной, коллектор - с выходной шиной 2, инжектирую-щий транзистор 3, последовательно с ним и между собой соединенные дополнительные р-п-р транзисторы j и 5. Эмиттер транзистора 3 подключен к шине 6 питания, базы транзисторов 3-5 через последовательно соединенные диоды 7 и 8 соединены с общей шиной, эмиттеры транзисторов t и 5 соединены с входными шинами 9 и 10 через диоды 11 и 12 соответственно.

Логический элемент работает следующим образом.

Если на шине 9 и 10 подается высокое положительное напряжение, то выходной транзистор 1 насыщен, т.е. на выходе выдается низкий потенциал близкий к нулю. При этом диоды 11 и 12 закрыты, а транзисторы открыты и обеспечивают базовый ток выходного транзистора 1. Напряжение на базах транзисторов равно удвоенному прямому падению напряжения на диоде. Если на один из входов 9 или 10, или на оба входа.подается низкий потенциал, близкий к нулю, то диод 11 или 12, или соответственно оба отрываются и отводят кйллекторный ток транзисторов 4 или 5, или 4 и 5 на землю. В результате базовый ток транзистора 1 уменьшается и QH закрывается, что соответствует логической единице на выходе.

Таким образом, логический элемент выполняет логическую функцию И-НЕ для логических переменных: О - низкий потенциал, 1 - высокий потенциал, и логическую функцию ИЛИ-НЕ для логических переменных: О - высокий

потенциал, 1 - низкий потенциал.

При изменении напряжения на входах элемента от низкого к высокому и наоборот переключение выхода из одного логического сост;ояния в другое происходит при напряжении, примерно равном двум прямым падениям напряжения на диоде, т.е. при том же напряжении, что и в элементах транзисторно-транзисторной и диодно-транзисторной логики.

Работоспособность (выполнение логи ческой функции) данного элемента

обеспечивается при выполнении следующего условия

Uо6э-0 4 5Ч в,

коэффициенты усиле(У -,, , о/ 4 , oi 5 ния по току в схеме с общей фазой тран- . зисторов ,

б ток, втекающий в шину 6 питания;

чток, втекающий в выходную шину 2;

8. коэффициент усиления по току в схеме с общим эмиттером транзистора 1.

В логическом элементе, представленна фиг. 2, показано, что на вхоможет быть включена диодная сборка.

Формула изобретения

Интегральный инжекционный логический элемент по авт. св. № 860315, отличающи. йся тем, что, с целью согласования выходных уровней с. уровнями транзисторно-транзисторных и диодно-транзисторных логических элементов, базы р-п-р транзисторов соединены с общей шиной через последовательно соединенные первые диоды, эмиттеры дополнительных р-п-р транзисторов соединены с входными шинами через вторые диоды.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 860315, кл. НОЗ, К 19/08, 07.05.7+.

. 1

Vt.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегральный инжекционный логический элемент | 1974 |

|

SU860315A1 |

| Интегральная схема | 1974 |

|

SU587808A2 |

| Цифровая полупроводниковая интегральная схема с тремя состояниями на выходе | 1980 |

|

SU900454A1 |

| Динамический логический элемент | 1979 |

|

SU822370A1 |

| Дешифратор | 1975 |

|

SU610298A1 |

| Адресный формирователь для интегрального постоянного запоминающего устройства | 1975 |

|

SU593250A1 |

| Устройство для адресно-разрядной выборки системы 2,5 д | 1973 |

|

SU531277A1 |

| Элемент для согласования насыщенных и ненасыщенных логических схем | 1972 |

|

SU438119A1 |

| Элемент памяти | 1981 |

|

SU978328A1 |

| МИКРОМОЩНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ С ВЫСОКОЙ НАГРУЗОЧНОЙ СПОСОБНОСТЬЮ | 1999 |

|

RU2172064C2 |

Авторы

Даты

1982-08-23—Публикация

1974-12-30—Подача