1

Изобретение относится к области вычислительной техники и предназначено для использования в качестве одного из элементов управления матрицей памяти интегрального оперативногозапоминающего устройства.

Известны многоканальные дешифраторы, состоящие из входного и выходного деформирующих каскадов l.

Недостаток их - сложность, -значительное потребление мощности.

Известен также дешифратор, состоящий из симметричного входного каскада содержащего в каждом из двух каналов входные, переключающие и инвертирующие транзисторы, причем эмиттеры входных транзисторов соединены со входами дешифратора, а эмиттеры инвертирующих п-р-п транзисторов подключены к .общей шине, и выxojb;нoгo каскада 2.

Однако отмечается значительная потребляемая мощность, низкое быстродействие и надежность.

Цель изобретения - повышение быстродействия, снижение потребляемой мощ ности.

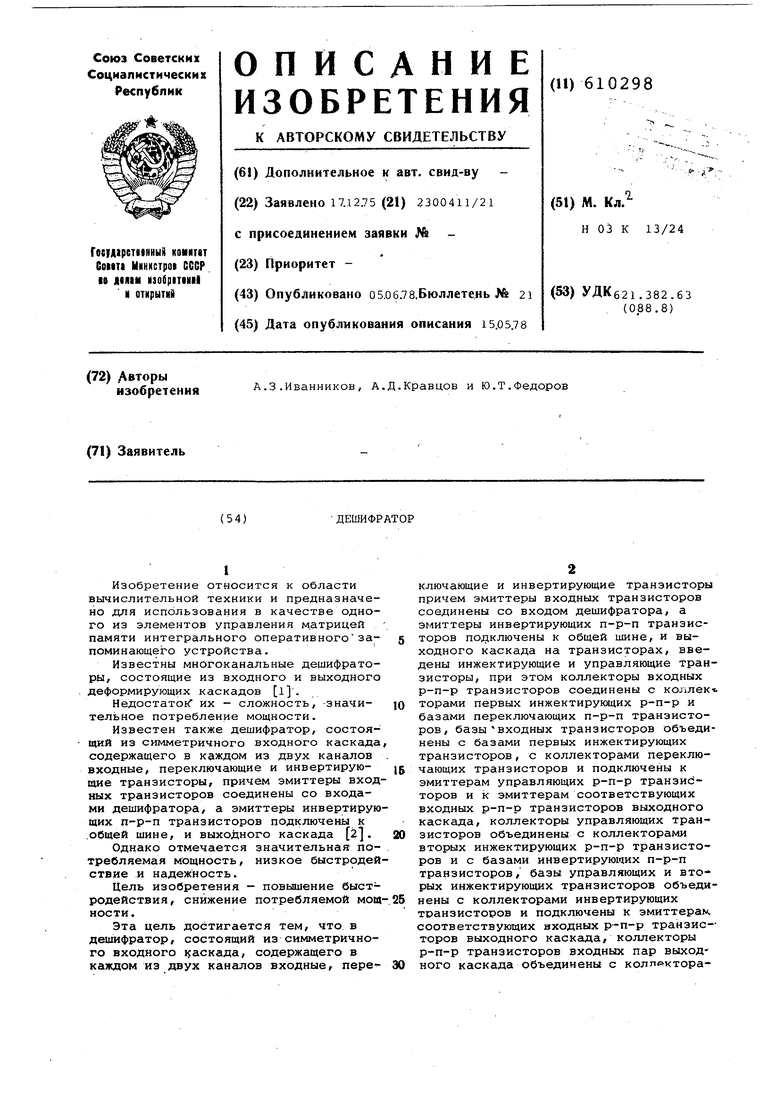

Эта цель достигается тем, что. в дешифратор, состоящий из симметричного входного 1{аскада, содержащего в каждом из двух каналов входные, переключающие и инвертирующие транзисторы причем эмиттеры входных транзисторов соединены со входом дешифратора, а эмиттеры инвертирующих п-р-п транзисторов подключены к общей шине, и выходного каскада на транзисторах, введены инжектирующие и управляющие транзисторы, при этом коллекторы входных р-п-р транзисторов соединены с коллек торами пер1вых инжектирующих р-п-р и базами переключающих п-р-п транзисторов, базы входных транзисторов объединены с базами первых инжектирующих транзисторов, с коллекторами переключающих транзисторов и подключены к эмиттерам управляющих р-п-р транзисторов и к эмиттерам соответствующих входных р-п-р транзисторов выходного каскада, коллекторы управляющих транзисторов объединены с коллекторами вторых инжектирующих р-п-р транзисторов и с базами инвертирующих п-р-п транзисторов, базы управляющих и вторых инжектирующих транзисторов объединены с коллекторами инвертирующих транзисторов и подключены к эмиттерак соответствующих входных р-п-р транзисторов выходного касксща, коллекторы р-п-р транзисторов входных пар выходного каскада объединены с колп кторами соответствующих инжектирующих р-п-р транзисторов выходного каскада и с базами соответствующих выходных п-р-п транзисторов, базы транзисторов входных пар объединены с базами соответствующих инжектирующих транзисторов вьоходного каскада и с коллекторами соответствующих выходных п-р-п транзисторов, коллекторы которых подключены к соответствующим выходам дешифратора, причем эмиттеры всех инжек тирующих транзисторов соединены с шиной питания, а эмиттеры инвертирующих и выходных транзисторов - с общей щиной. На фиг. 1 показана принципиальная схема предлагаемого инжeкциoннQгo дешифратора, на фиг. 2 - временные диаграммы прохождения импульсных сигна.лов на входе и выходе устройства. Дешифратор содержит в каждом канале входного каскада входной р-п-р транзистор 1, эмиттер которого подклю чен к соответствующим входам дешифратора. Базы транзисторов 1 объединены с базами р-п-р первых инжектирующих транзисторов 2 и с коллекторами п-р-п переключающих транзисторов 3 и подклю чены к эмит.терам р-п-р управляющих транзисторов 4 и к эмиттерам р-п-р транзисторов 5,6 и 7,8 входных транзисторных пар выходного каскада соответственно для левого и правого каналов входного каскада. Коллекторы тран зисторов 1 объединены с коллекторами транзисторов 2 и с базами транзисторо 3. Коллектора транзисторов 4 объедине ны с коллекторами вторых инжектирующих р-п-р транзисторов 9 и с базами инвертирующих п-р-п транзисторов 10, коллекторы которых связаны с эмиттера ми р-п-р транзисторов 11,12 и 13,14 входных транзисторных пар выходного каскада соответственно для левого и правого каналов входного каскада. Эми тары инжектирующих транзисторов 2 и 9 соединены с шиной питания, к которо также подключены эмиттеры инжектирующих р-п-р транзисторов 15-18 выходного каскада. При этом база транзистора 15 подключена к объединенным базам транзисторов 11 и 13, образующих первую входную пару выходного каскада, и к коллектору выходного п-р-п транзистора 19, соединенного с первым выходом дешифратора. База транзистора 16 подключена к объединенным базам транзисторов 5 и 8, образующих вторую входную пару выходного каскада, и к коллектору выходного п-р-п транзистора 20, соединённого со вторым выходом дешифратора. База транзистора 17 подключена к объединенным базам транзисторов 7 и 12, образующих третью входную пару выходного каскада, и к коллектору выходного п-р-л транзистора 21, соединенного с третьим выходом 22 дешифратора. Точно также база транзистора 18 подключена к объединенным базам транзисторов 6 и 14, образующих четвертую входную пару выходного каскада, и к коллектору выходного транзистора 23, соединенного с четвертым выходом 24 дешифратора. Коллектор транзистора 15 соединен с объединенными коллекторами транзисторов 11 и 13 и с базой выходного транзистора 19. Коллектор транзистора 16соединен с объединенными коллекторами транзисторов 5 и 8 и с базой транзистора 20. Коллектор транзистора 17соединен с объединенными коллекторами транзисторов 7 и 12 и с йазой транзистора 21. Точно также коллектор транзистора 18 соединен с объединенными коллекторами транзисторов 6 и 14 и с базой транзистора 23. Эмиттеры транзисторов 3,6,19,20,21 и 23 соединены с общей шиной. Предлагаемый инжекционный дешифратор работает следующим образом. Ко входам 25 и 26 приложен высоки уровень потенциала. Тогда р-п-р транзистор 1 в каждом канале будет заперт. Ток от источника питания через р-п-р транзистор 2 откроет п-р-п транзистор 3, потенциал коллектора которого « О , соответствующий уровню логи ческого О, поступает на эмиттеры транзисторов 5 и 6 выходного каскада для левого канала и транзисторов 7 и 8 для правого канала входного каскада дешифратора, а также на эмиттеры р-п-р транзисторов 4. Ток через р-п-р . транзистор 5, открытый р-п-р транзис- тор 4 и насыщенный п-р-п транзистор 3 замыкается на общую шину. Базовый ток транзистора 6 отсутствует, и высокий потенциал его коллектора постут- пает на эмиттеры р-п-р транзисторов 11 и 12 выходного каскада для левого канала и транзисторов 13 и 14 для правого. Из рассмотрения уровней потенциалов , поступающих на эмиттеры каждой пары входных р-п-р транзисторов выходного каскада при подаче на входы дешифратора логической 1, следует, что только на эмиттерах одной пары транзисторов 11 и 13 имеется высокий потенциал. Это обеспечивает их запертое состояние. Ток через р-п-р транзистор 15 открывает выходной п-р-п транзистор 19, потенциал коллектора которого устанавливает на выходе 27 дешифратора уровень логического 0. Остальные входные пары р-п-р транзисторов 5и8, 7 и 12, 6и14 имеют низкий потенциал хотя бы на одном из эмиттеров, что определяет уровень логической выходах 28,22 и 24 дешифратора. На эмиттер транзистора А поступает низкий потенциал, а на эмиттер транзистора 12 - высокий. Ток, протекающий через переход эмиттер-база р-п-р транзистора 17, открывает р-п-р транзистор 7. Через открытые транзистор 7 и транзистор 3 правого канала входного каскада базовый ток выходного п-р-п .транзистора 21 замыкается на общую шину, что приводит к запиранию транзистора 21. На выходе 22 дешифратора устанавливается логическая 11 Если на ЮДИН из входов дешифратора, .например, на вход 26, подать низкий уровень, то ток от шины питания через переход: эмиттер-база р-п-р транзистора 2 правого канала откроет транзистор 1 правого канала. По цепи открытый р-п-р транзистор 1 - вход 26 дешифратора, базовый ток п-р-птранзистора 3 правого канала замкнется на общую шину, что обеспечит запирание транзистора 3. Высокий потенциал с коллектора транзистора 3 поступит на эмиттеры р-п-р транзисторов 7 и 8 выходного каскада и на эмиттер р-п-р транзистора 4 правого канала, что пр ведет к его запиранию. Ток через р-п-р транзистор 9 правого канала вв дит в насыщение транзистор 10 правого канала, низкий потенциал коллектора которого поступает на эмиттеры.р-п-р транзисторов 13 и 14 входных пар выходного каскада. Следовательно, при подаче на вход 25 логической , а на вход 26 логиче кого о только на эмиттерах одной пары входных р-п-р транзисторов 7 и 12 вы ходного каскада имеются высокие поте циалы, что ведет к установлению на выходе 22 дешифратора уровня логичес Остальные входные пары р-п-р транзисторов выходного каскада имеют низкий потенциал хотя бы на одном эмиттере, что определяет уровень логической l на выходах 27,28 и 24 дешифратора . Таким образом, двухразрядный код на входах дешифратора преобразуется в четырехразрядный адресный код на выходах в соответствии с таблицей истинности. ром мошность, т.е. предлагаемый инжекционный дешифратор работает в нано-микромощном режиме .Напряжение питания деифратора всего 1,0-1,4 В. Слаботочный режим работы дешифратора повышает его надежность. Надежность повышается также за счет уменьшения числа межсоединений, числа элементов и контактов. Формула изобретения Дешифратор, состоящий из симметричного входного каскада/ содержащего в каждом из двух каналов входные, переключающие и инвертирующие транзисторы, причем эмиттеры входных вранзисторов соединены со входом дешифратора. а эмиттеры инвертирующих п-р-п транзисторов подключены к общей шине, и выходного каскада на транзисторах. отличающийся тем, что, с целью повышения быстродействия, снижения потребляемой мощности, в дешифратор введены инжектирующие и управляющие транзисторы, при этом коллекторы входных р-п-р транзисторов соединены с коллекторами первых инжектирующих р-п-р и базами переключающих п-р-п транзисторов, базы входных транзисторов объединены с базами первых инжектирующих транзисторов, с коллект торами переключающих транзисторов и подключены к эмиттерам управляющих р-п-р транзисторов и к эмиттерам соответствующих входных р-п-р транзисторов выходного каскада, коллекторы управляющих транзисторов объединены с коллекторами вторых инжектирующих р-п-р транзисторов и с базами инвертирующих п-р-п транзисторов, базы упра ляющих и вторых инжектирующих транзисторов Объединены с- коллекторами инвертирующих транзисторов и подключ ны к эмиттерам соответствующих входных р-п-р транзисторов выходного каскада, коллекторы р-п-р транзисторов входных пар выходного каскада объедиг нены с коллекторами соответствующих инжектирующих р-п-р транзисторов выходного каскада и с базами соответст- вующих выходных п-р-п транзисторов, базы транзисторов входных пар объеди нены с базами соответствующих инжектирующих транзисторов выходного каскада и с коллекторами соответствующий выходных п-р-п транзисторов, коллекторы которых подключены к соответствую- щим выходам дешифратора, причем эмит- теры. всех инжектирующих транзисторов соединены с шиной питания, а эмиттеры инвертирующих и выходных транзисторов - с общей шиной. Источники информации, принятые во внимание при экспертизе 1.Патент США 3444462, кл. И 324-64, 1973. ,, 2.Каталог фирмы Texas anstuments . 1969, серия 7488.

27

19

Вып. 1

t f in ,7 f 2,i Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор | 1977 |

|

SU1050110A1 |

| Дешифратор | 1975 |

|

SU547968A1 |

| Формирователь импульсов | 1975 |

|

SU656192A1 |

| Коммутатор | 1977 |

|

SU684742A1 |

| Устройство для считывания информации из блоков памяти | 1977 |

|

SU693434A1 |

| Двухканальный дешифратор | 1974 |

|

SU512575A1 |

| Логический элемент "запрет" | 1976 |

|

SU587627A1 |

| Д-триггер | 1973 |

|

SU468360A1 |

| Дешифратор | 1977 |

|

SU681557A1 |

| Преобразователь логических уровней | 1978 |

|

SU790327A1 |

Авторы

Даты

1978-06-05—Публикация

1975-12-17—Подача