писывающих токов (считывающих) подключена к соответствующему выходу дешифратора адреса, эмиттер - к шине нулевого потенциала, коллектор - через резистор к базе транзистора обратной проводимости, которая через второй резистор соединена с положительным потенциалом источника напряжения, коллектор - через третий резист подключен к шине нулевого потенциала, а также к входу транзисторного ключа втекающего (вытекающего) записывающего тока (считывающего) каждого разряда через резистор, эмиттеры транзисторов обратной проводимости лбьединены и через прямо включенный диод подключены к шине положительного потенциала источника напряжения.

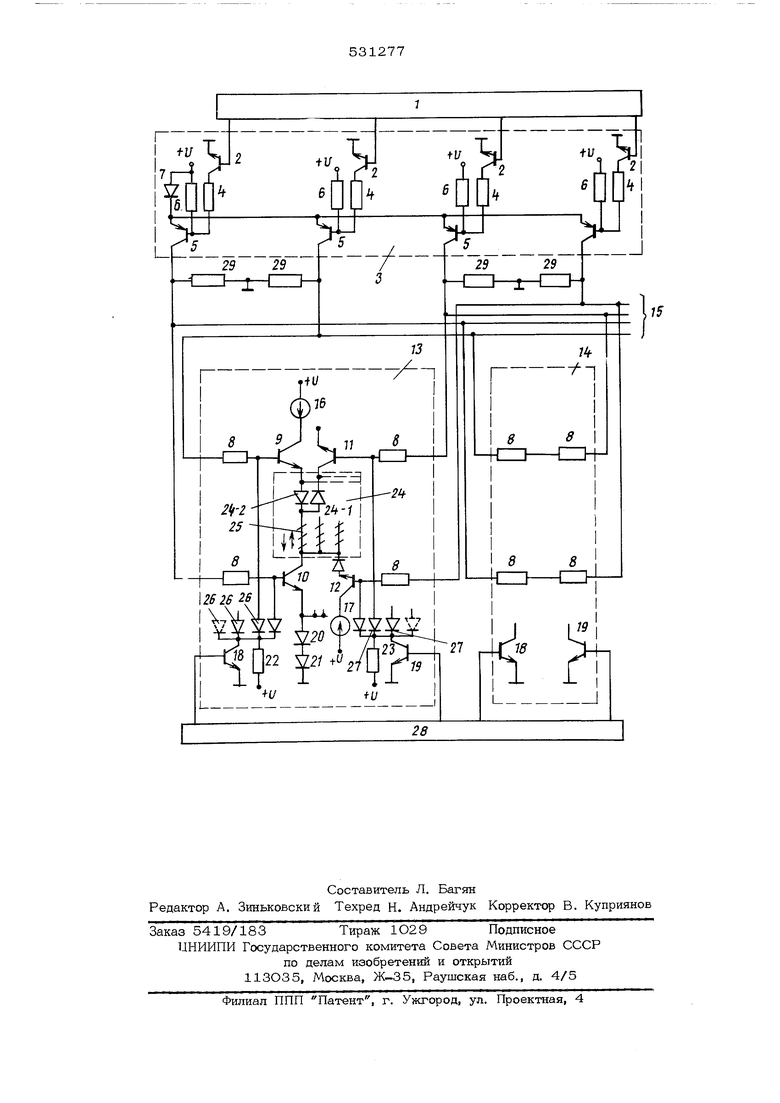

На чертеже приведена принципиальная электрическая схема устройства.

Устройство для адресно-разрядной выборки системы 2,5 Д содержит дешифратор адреса 1, выполненный, например, на логических интегральных узлах типа ТТЛ, выходы которого соединены с базами транзисторов 2 согласуюшего блока 3, коллектор каждого из которых через резистор 4 соединен с базой соответствующего транзистора 5 другого типа проводимости, база которого через резистор 6, а эмиттер через диод 7 соединены с положительным потенциалом источника напряжения, ,

Эмиттеры транзисторов 5 объединены, а коллекторы через резисторы 8 соединены с базами транзисторов ключей 9-12 вытекающего и втекающего считывающих токов и втекающего и вытекающего записывающих токов соответственно, которые образуют переключатель адресного тока одного разряда 13 и последующих подобных разрядов 14, 15 и т.д. запоминающего устройства структуры 2,5 Д.

Кроме того, переключатель адресного тока одного разряда содержит генераторы 16 и 17 считывающих и записывающих токов, ключи 18 и 19, управляющие считывающими и записывающими токами соответственно, два последовательно соединенных диода 20 и 21, резисторы 22 и 23, диодный дешифратор 24 с выходом на нагрузку25 (адресные линии разряда).

Коллекторы ключей 18 и 19 через диоды 26 и 27 соединены с базами транзисторов ключей 9и1Ои11и12 соответственно, а базы - с выходами управляющего блока (регистра числа 28).

Коллектор каждого из транзисторов 5 через резистор 29 соединен с землей, а коллектор транзистора ключа 1О - с катодами диодов 24-1 дещифратора 24 адресных линий другого разряда, а эмиттер транаисторов ключа 9 - с анодами других диодов 24-2 дещифратора 24.

В исходном состоянии транзисторы 2 за1крыты сигналами с выхода дещифратора адреса 1 и закрыты транзисторы 5. Ключи 9-12 разомкнуты, а ключа 18 и 19замкнуты, при этом базы транзисторов ключей 9-12 через диоды 26 и 27 привязаны к потенциалу земли.

При обращении к запоминающему устройству , например по первому адресу с блока 28 запирается ключ 18, диоды 26 запираются положительным потенциалом череф резистор 22 и тем самым устраняется вли;яние паразитных емкостей этих диодов на динамические процессы и базах транзисторов ключей 9 и 1О. Последние удерживаются в закрытом состоянии нулевым потенциалом через резис торы 8 и 2 9.

При появлении считывающих импульсов с выходов дешифратора адреса 1 соответствующие транзисторы 2 и 5 отпираются и на базы транзисторов ключей 9 и 10 всех разрядов 13-15 подается отпирающий потенциал. Ключи 9 и 1О замыкаются, и через выбранную адресную линию протекает считывающий ток генератора 16. Одновременно с окончанием считывающего импульса кончается импульс с блока 28, ключ 18 замыкается ичерез диоды 26 на базы транзисторов ключей 9 и 10 поступает нулевой потенциал.

Ключи 9 и 1О размыкаются и считываю-

96 щий ток в выбранной линии обрывается, не дождавшись запирания транзисторов 5.

При возбуждении записывающего тока предварительно выключается ключ 19 данного разряда, С задержкой на время, не

40 меньшее времени выключения ключа 19, с вьтходов дещифратора адреса 1 появляются записывающие импульсы и соответствующие транзисторы 2 и 5 отпираются и ключи 11 и 12 данного разряда замыкаются, и через

45 выбранную линию протекает записывающий ток генератора 17,

При записи О, например, в разряде 14 ключ 19 этого разряда не размыкается и ключи 11 и 12 этого разряда остаются ра-

90 зомкнутыми, так как базы их транзисторов через диоды 27 и резистор 23 привязаны к нулевому потенциалу, а эмиттер транзистора ключа 11 смещен на два диодных перехода,

fg, При записи 1 окончание записывающего тока происходит аналогично окончанию считывающего тока. Назначение ключей 9,10,18 может поменяться с назначением ключей 11,12,19 при изменении фазы тока.

Таким образом, в предложенном устройстве при относительной простоте его конструкции временные параметры записывающего и считывающего токов получаются Ьысокостабильными.

Формула изобретения

1. Устройство для адресно-разрядной выборки системы 2,5 Д содержащее в каждом разряде транзисторные ключи втекающего и вытекающего записывающего и считывающего токов, входы которых через согласующий блок подключены к дещифратору адреса, генераторы записывающего и считывающего токов, ключ, управляющий записывающим током, вход которого подключен к выходу регистра числа, диодный дещЕфратор адресных линий разряда и источник напряжения, отличающеес я тем, что, с целью упрощения устройства и повыщения стабильности временных параметров токов, в каждый разряд дополнительно введены ключ, управляющий считывающим током, и два последовательно согласно включенных диода, причем входы каждого транзисторного ключа втекающего и вытекающего записывающего и считывающего токов соединены через другой дополнительный диод и соответствующий ключ, управляющий записывающим током (считывающим) с шиной нулевого потенциала, которая через два дополнительных последовательно согласно включенных диода соединены с точкой соединения ключей втекающего считывающего тока.

2, Устройство по п. 1, о т л и ч а ю - щ е е с я тем, что согласующий блок выполнен на транзисторах разного типа проводимости, причем база каждого транзистора с проводимостью такой же, как и проводимость транзисторов ключей втекающих записывающих токов (считывающих) подключена к соответствующему выходу дешифратора адреса, эмиттер - к шине нулевого потенциала, коллектоо - через резистор к базе транзистора обратной проводимости, которая через второй резистор соединена с

положительным потенциалом источника напряжения, коллектор - через третий резистор подключен к шине нулевого потенциала, а также к входу транзисторного ключа втекающего (вытекающего) записывающего то-

ка (считывающего) каждого разряда через резистор, эмиттеры транзисторов обратной проводимости объединены и через прямо включенный диод подключены к Ш1ше положительного потенциала источника напряжеНИН.

Источники информации, приняты во внимание при экспертизе.

1. Запоминающие устройства современных ЭЦВМ, Сборник статей под ред. А.А. Круп- ского, М., 1968, с. 120.

2.3111 Transactions on ГЕес-Ьготс Computers, 966,voe-IC--ff, N4-, p-48i

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU385314A1 |

| Устройство для выборки информации из блоков памяти типа 2,5д | 1978 |

|

SU765874A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| Формирователь адресных токов | 1979 |

|

SU924752A1 |

| Запоминающее устройство | 1976 |

|

SU690564A1 |

| ПЬЕЗОТРАНСФОРМАТОРНОЕ ЗАПОЛИШАЮЩЕЕ УСТРОЙМТ?|11е0-1ЕЛКГ1:: | 1972 |

|

SU331421A1 |

| Устройство для выборки координатных шин магнитного накопителя | 1983 |

|

SU1140177A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| Устройство для выбора информации из блоков памяти | 1982 |

|

SU1019491A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1133621A1 |

Авторы

Даты

1976-10-05—Публикация

1973-10-16—Подача