.(54) ЭЛЕМЕНТ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Полупроводниковый элемент памяти | 1980 |

|

SU942150A1 |

| Интегральная ячейка памяти | 1973 |

|

SU566268A1 |

| ТТЛ-вентиль | 1985 |

|

SU1324105A1 |

| Логический вентиль | 1980 |

|

SU940308A1 |

| Динамический логический элемент | 1979 |

|

SU822370A1 |

| Ячейка памяти | 1974 |

|

SU1327185A1 |

| D-триггер | 1985 |

|

SU1332380A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU752482A1 |

| Элемент транзисторно-транзисторной ложки (его варианты) | 1985 |

|

SU1274149A1 |

| Схема согласования уровней ТТЛ-ЭСЛ | 1985 |

|

SU1309301A1 |

1

Изобретение относится к цифровсЛ вычислительной технике и может быть ис пользовано в полупроводниковых запоминающих устройствах большой информационной емкости.

Известен элемент памяти, содержащий первый и второй г -р- п транзисторы, sfMKTTepbi которых соединены с обшей шиной, а коллекторы соединены с катодами соответственно первого и второго диодов Q Шоттки, аноды которых соединены через диоды с управляющими шинами и щиной питания 1 .

Недостатком этого элемента памяти является относительно низкая помехо- 5 устойчивость.

Известен также элемент памяти, содержащий первый и второй n-p-ri транзисторы, первый и второй р - п - р транзисторы и четыре диода Шоттки, первая и 20 вторая шины управления элемента памяти соединены с анодами соответственно первого и второго диодов Шоттки, катоды которых соединены с анодами соответственно третьего и четвертого диодов Шот- ТКИ, катоды KOTOfa ix соединены с коллекторами соответственно первого и второго п-р-п. транзисторов, базы которых соединены с коллекторами соответственно первого и второго р-п-р транзисторов, базы которых соединены с шиной смешения, а эмиттеры п-р-п транзисторов соединены с общей шиной 2 .

Недостатком известного элемента памяти является относительно низкая достоверность функционирования.

Цель изобретения - повышение достоверности функционирования.

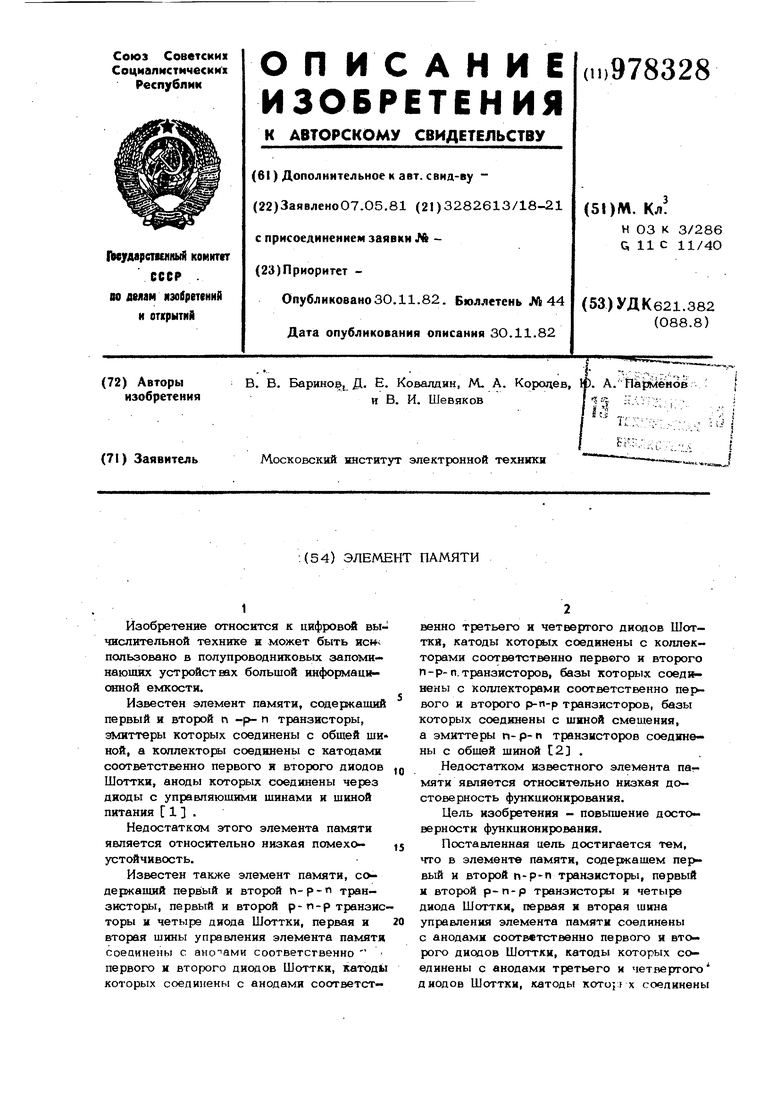

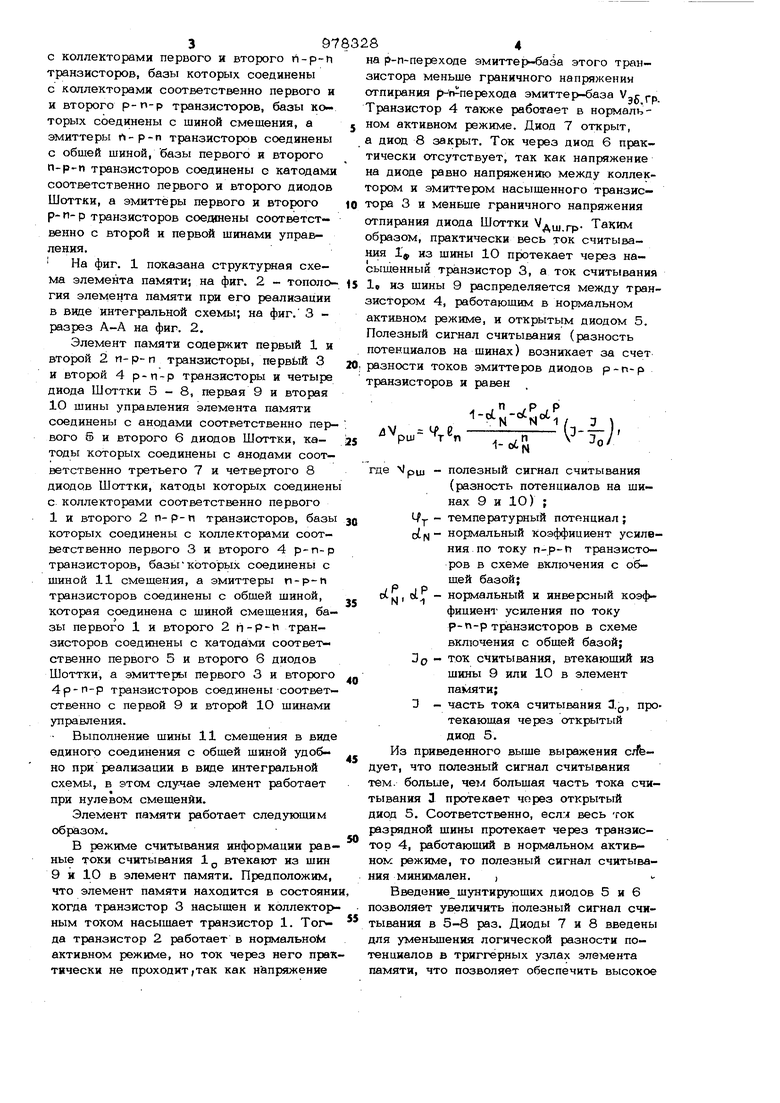

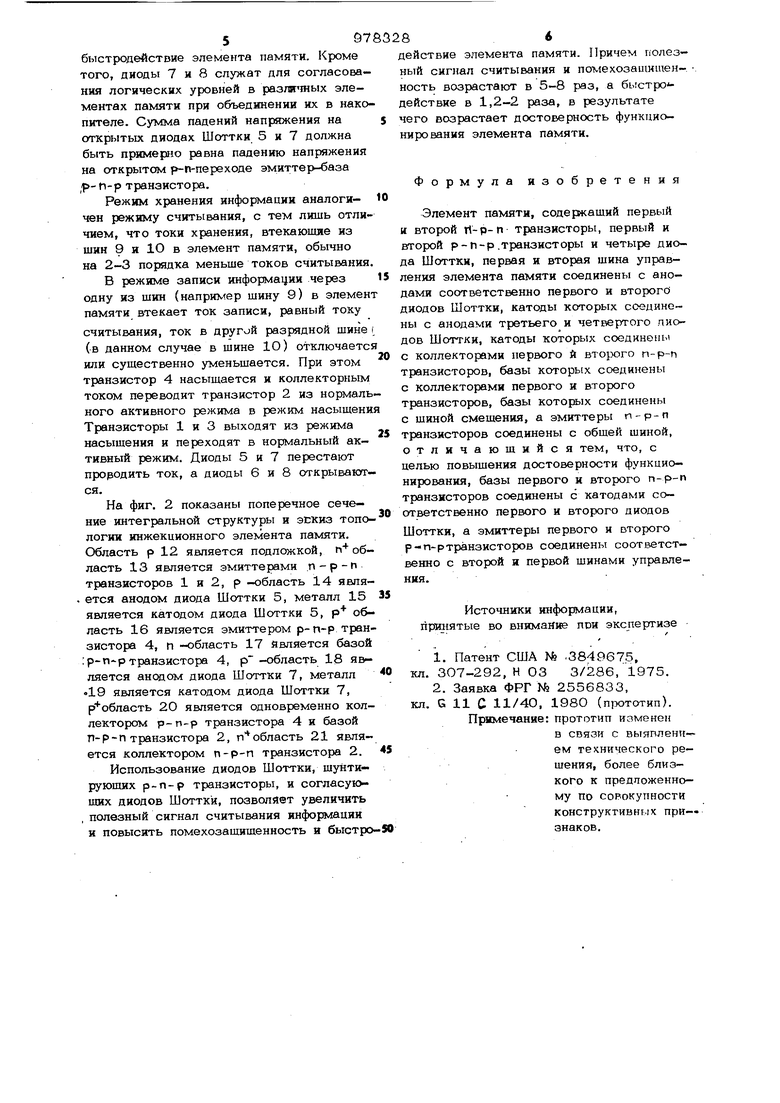

Поставленная цель достигается тем, что в элементе памяти, содержащем первый и второй h-p-n транзисторы, первый и вторюй р-п-р транзисторы и четыре диода Шоттки, первая и вторая шина упр авления элемента памяти соединены с анодами соответственно первого и второго диоаов Шоттки, катоды которых соединены с анодами третьего и четвертого диодов Шоттки, катоды кото; г х соединены с коллекторами первого и второго t1-p-n транзисторов, базы которых соединены с коллекторами соответственно первого и и второго р-п-р транзисторов, базы которых соединены с шиной смещения, а эмиттеры rt-p-n транзисторов соединены с обшей шиной, базы первого и второго п-р-п транзисторов соединены с катодами соответственно первого и второго диодов Шоттки, а эмиттеры первого и второго р- п- р транзисторов соедшены соответственно с второй и первой шинами управления, На фиг. 1 показана структурная схема элемента памяти; на фиг. 2 - топология элемента памяти при его реализации в вице интегральной схемы; на фиг. 3 разрез А-А на фиг. 2. Элемент памяти содержит первый 1 и второй 2 п-р-п транзисторы, первьШ 3 и второй 4 р-п-р транзисторы и четыре диода Шоттки 5-8, первая 9 и вторая 1О шины управления элемента памяти соединены с анодами соответственно первого 5 и второго 6 диодов Шоттки, катоды которых соединены с анодами соответственно третьего 7 и четвертого 8 диодов Шоттки, катоды которых соединены с коллекторами соответственно первого 1 и второго 2 п-р-п транзисторов, базы которых соединены с коллекторами соответственно первого 3 и второго 4 р-п-р транзисторов, базыкоторых соединены с шиной 11 смещения, а эмиттеры n-p-ti транзисторов соединены с обшей шиной, которая соединена с шиной смешения, базы первого 1 и второго 2 h-P-n транзисторов соединены с катодами соответственно первого 5 и второго 6 диодов Шоттки, а эмиттеры первого 3 и второго 4р-п-р транзисторов соединены-соответственно с первой 9 и второй 1О шинами управления. Выполнение шины 11 смешения в виде единого соединения с обшей шиной удобно при реализации в вице интегральной схемы, в этом случае элемент работает при нулевом смешении. Элемент памяти работает следующим образом. В режиме считывания информации равные токи считывания 1 втекают из шин 9 к 10 в элемент памяти. Предположим, что элемент памяти находится в состояни когда транзистор 3 насыщен и коллектор ным током насыщает транзистор 1. Тогда транзистор 2 работает в нормально1|Л активном режиме, но ток через него прак тически не проходит,так как напряжение ма р-п-переходе эмитте(-база этого транзистора меньше граничного напряжении отпирания р -п перехода эмиттер-база V,r р Транзистор 4 также работает в нормальном активном режиме. Диод 7 открыт, диод 8 закрыт. Ток через диод 6 практически отсутствует, так как напряжение на диоде равно напряжению между коллекором и эмиттером насыщенного транзис- тора 3 и меньше граничного напряжения отпирания диода Шоттки Удщ pp. Таким образом, практически весь ток считывания 1ф из шины 1О протекает через насыщенный транзистор 3, а ток считывания 1, из шины 9 распределяется между транзистором 4, работающим в нормальном активном режиме, и открытым диодом 5 Полезный сигнал считывания (разность потенциалов на шинах) возникает за счет. разности токов эмиттеров диодов р-п-р транзисторов и равен П р р тя ,.п (-Tj где vlpio - полезный сигнал считывания (разность потенциалов на шинах 9 и 10) ; Ц - температурный потенциал ; df)- нормальный Коэффициент усиления по току п-р-п транзисторов в схеме включения с обшей базой; otjg, ol - нормальный и инверсный коэффициент усиления по току р-п-р тр анзисторов в схеме включения с общей базой; DO - ток считывания, втекающий из щины 9 или 10 в элемент памяти; tJ - часть тока считывания 3., протекающая через открытый диод 5. Из приведенного выще выражения c/fe- дует, что полезный сигнал считывания тем. больше, чем больщая часть тока считывания Л протекает через открытый диод 5. Соответственно, есл:/с весь ток разрядной шины протекает через транзистор 4, работающий в нормальном активном режиме, то полезный сигнал считывания минимален. , Введение щунтирующих диодов 5 и 6 позволяет увеличить полезный сигнал считывания в 5-8 раз. Диоды 7 и 8 введены для уменьшения логической разности по- тенциалов в триггерных узлах элемента памяти, что позволяет обеспечить высокое быстродействие элемента памяти. Кроме того, диоды 7 и 8 служат для согласования логических уровней в различных элементах памяти при объединении их в нако пителе. Сумма падений напряжения на опгкрытых диодах Шоттки 5 и 7 должна быть примерю равна падению напряжения на открытом | -п-переходе эмиттер-база р-п-р транзистора. Режим хранения информации аналогичен режиму считывания, с тем лишь отличием, что токи хранения, втекающие из шин 9 и 1О в элемент памяти, обычно на 2-3 порядка меньше токов считывания В режиме записи информации через одну из шин (Hanpm fep шину 9) в элемен памяти втекает ток записи, равный току считывания, ток в другой разрядной шине (в данном случае в шине 1О) отключаетс или существенно уменьшается. При этом транзистор 4 насыщается и коллекторным током переводит транзистор 2 из нормаль ного активного режима в режим насыщени Транзисторы 1 и 3 выходят из режима насыщения и переходят в нормальный активный режим. Диоды 5 и 7 перестают прюэодить ток, а диоды 6 и 8 открываются. На фиг. 2 показаны поперечное сечение интегральной структуры и эскиз топологии инжекционного элемента памяти. Область р 12 является подложкой, п область 13 является эмиттерами п-р-п транзисторов 1 и 2, р -область 14 явпя. ется анодом диода Шоттки 5, металл 15 является катодом диода Шоттки 5, р область 16 является эмиттером р-п-р транзистора 4, п -область 17 Является базой :р-Пр транзистора 4, р -область 18 является анодом диода Шоттки 7, металл 19 является катодом диода Шоттки 7, р область 20 является одновременно коллекторхзм р-п-р транзистора 4 и базой п-р-п транзистора 2, п область 21 является коллектором п-р-п транзистора 2. Использование диодов Шоттки, шунтирующих р-п-р транзисторы, и согласующих диодов Шоттки, позволяет увеличить , полезный сигнал считывания информации и повысить помехозащищенность и быстро- действие элемента памяти. Причем полезный сигнал считывания и помехозащищенность возрастают в 5-8 раз, а быстро действие в 1,2-2 раза, в результате чего возрастает достоверность функционирования элемента памяти. Формула изобретения Элемент памяти, содеркаший первый и второй rt-p-n транзисторы, первый к впгорой р-п-р.транзисторы и четыре диода Шоттки, первая и вторая шина управления элемента памяти соединены с анодами соответственно первого и второго диодов Шоттки, катоды которых соединены с анодами третьего и четвертого пиодов Шоттки, катоды которых соединены с коллекторами первого ft вто1к го п-р-п транзисторов, базы которых соединены с коллекторами первого и второго транзисторов, базы которых соединены с шиной смешения, а эмиттеры п-р-п транзисторов соединены с обшей шиной, отличающийся тем, что, с целью повыщения достоверности функционирования, базы первого и вторюго п-р-п транзисторов соединены с катодами соответственно первого и второго диодов Шоттки, а эмиттеры первого и второго р-п-ртранзисторов соединены соответственно с второй и первой шинами управления. Источники информации, принятые во внимание при экспертизе . 1.Патент США Ng .3849675, кл. 307-292, Н 03 3/2.86, 1975. 2.Заявка ФРГ № 2556833, кл. G 11 С 11/40, 1980 (прототип). Примечание: прототип изменен в связи с выявлением технического решения, более близкого к предложенному по сорокупности KoHcrpyKTHBHt.ix признаков.

ff

s

A-A

Авторы

Даты

1982-11-30—Публикация

1981-05-07—Подача