(Sk) УСТРОЙСТВО для ВВОДА-ВЫВОДА ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки сообщений | 1990 |

|

SU1803919A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для управления обменом информацией | 1990 |

|

SU1783525A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ | 1990 |

|

RU2007865C1 |

| Устройство КЭШ-памяти | 1988 |

|

SU1675881A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ИСТОЧНИКА ИНФОРМАЦИИ С ПРОЦЕССОРОМ | 1991 |

|

RU2033636C1 |

| Устройство для сопряжения двух вычислительных машин | 1986 |

|

SU1405064A1 |

| Устройство для формирования тестов субблока логического блока | 1987 |

|

SU1513453A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1688229A1 |

| Устройство для сопряжения ЭВМ с каналом передачи данных | 1989 |

|

SU1647580A1 |

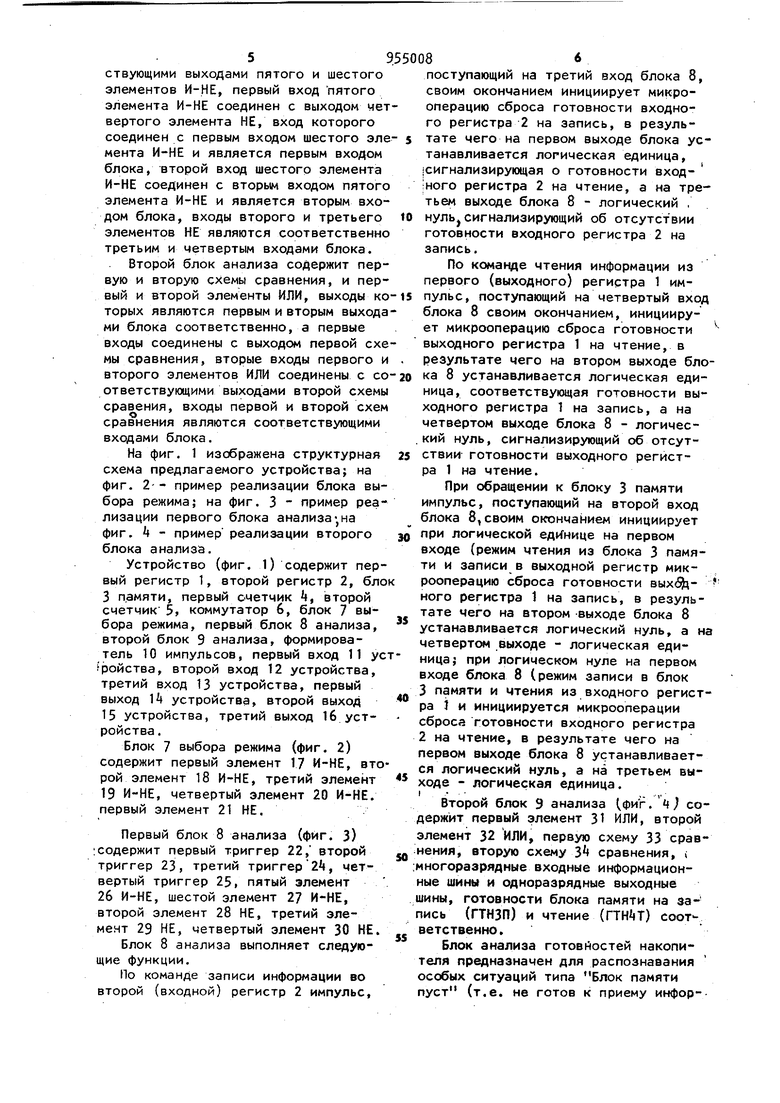

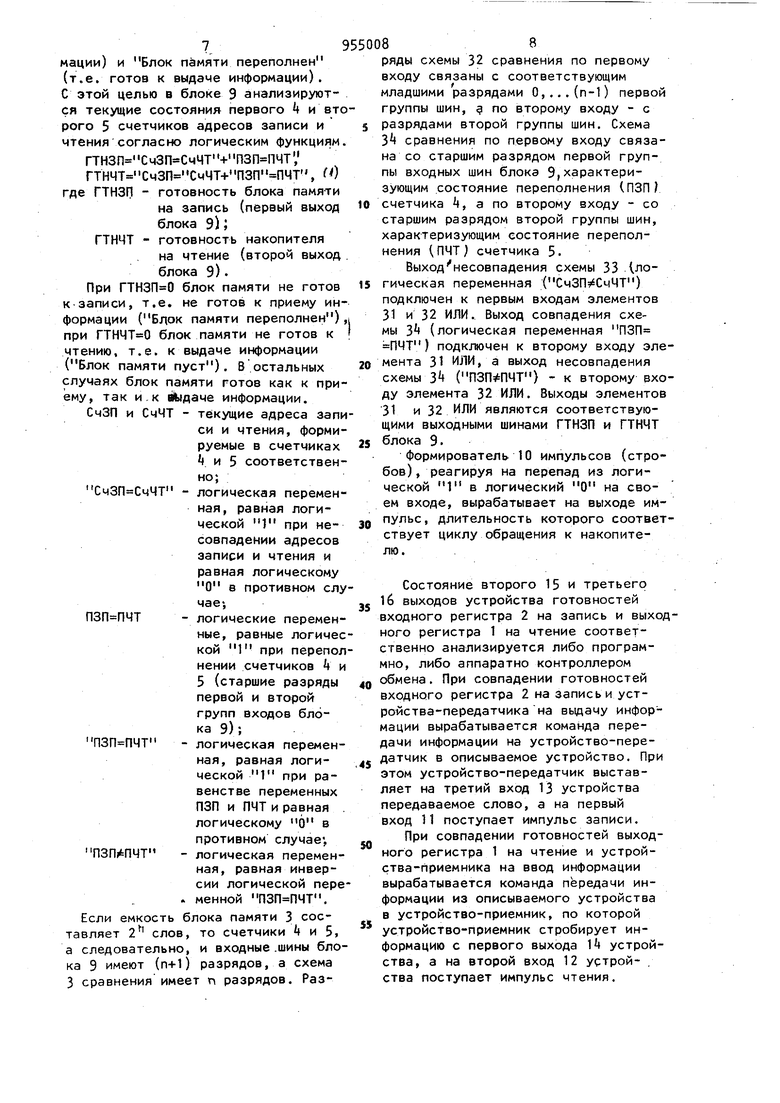

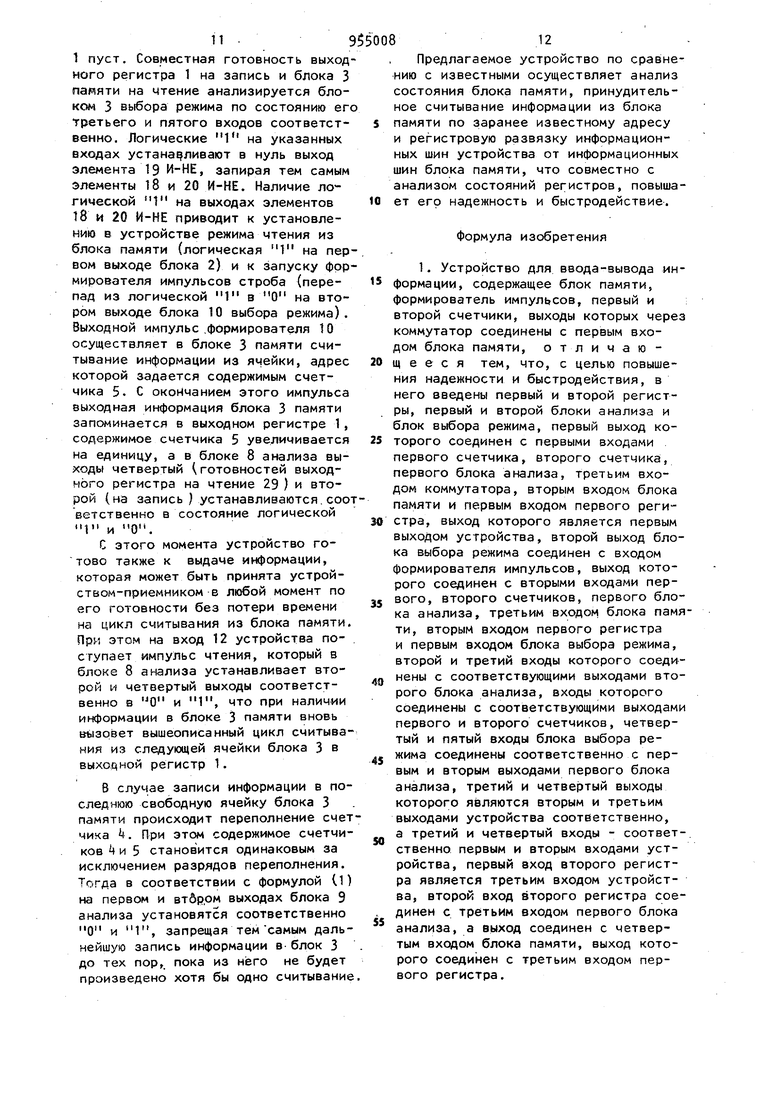

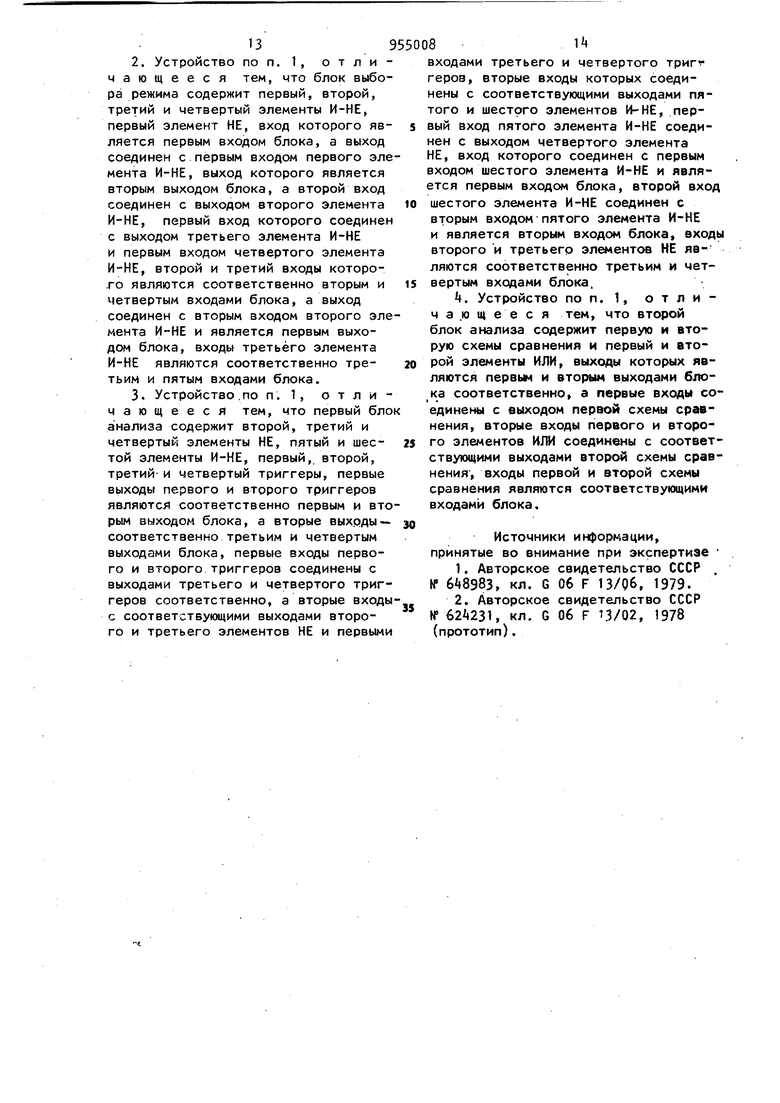

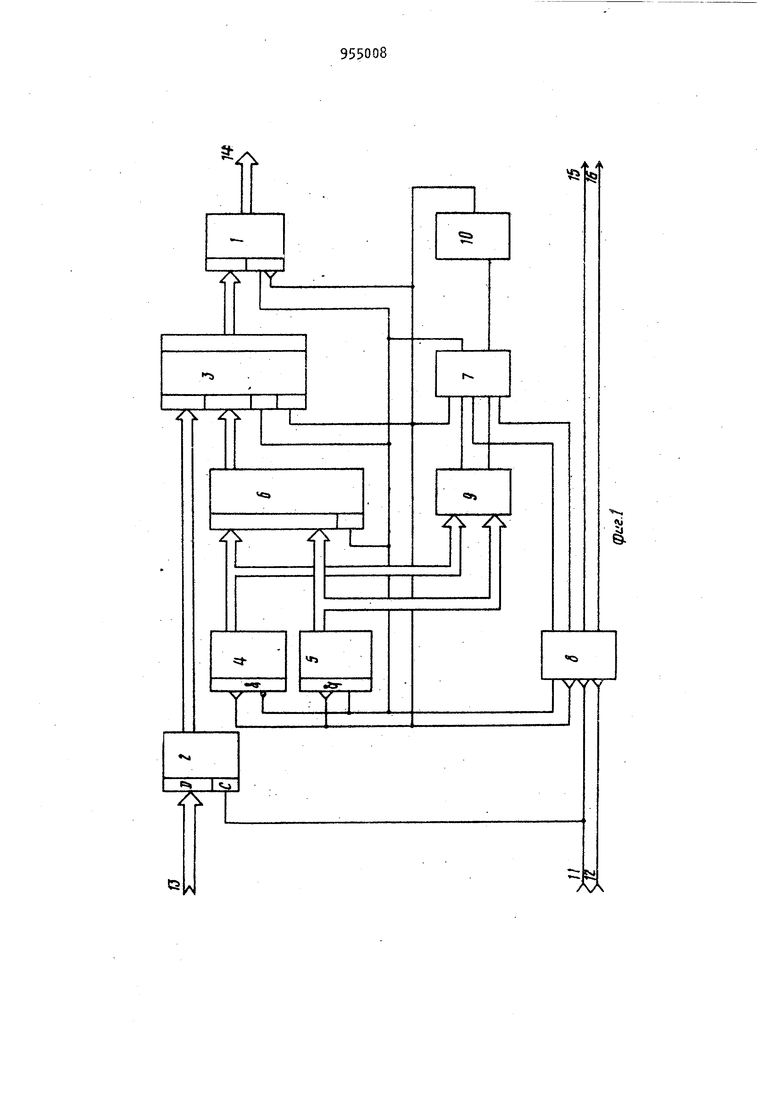

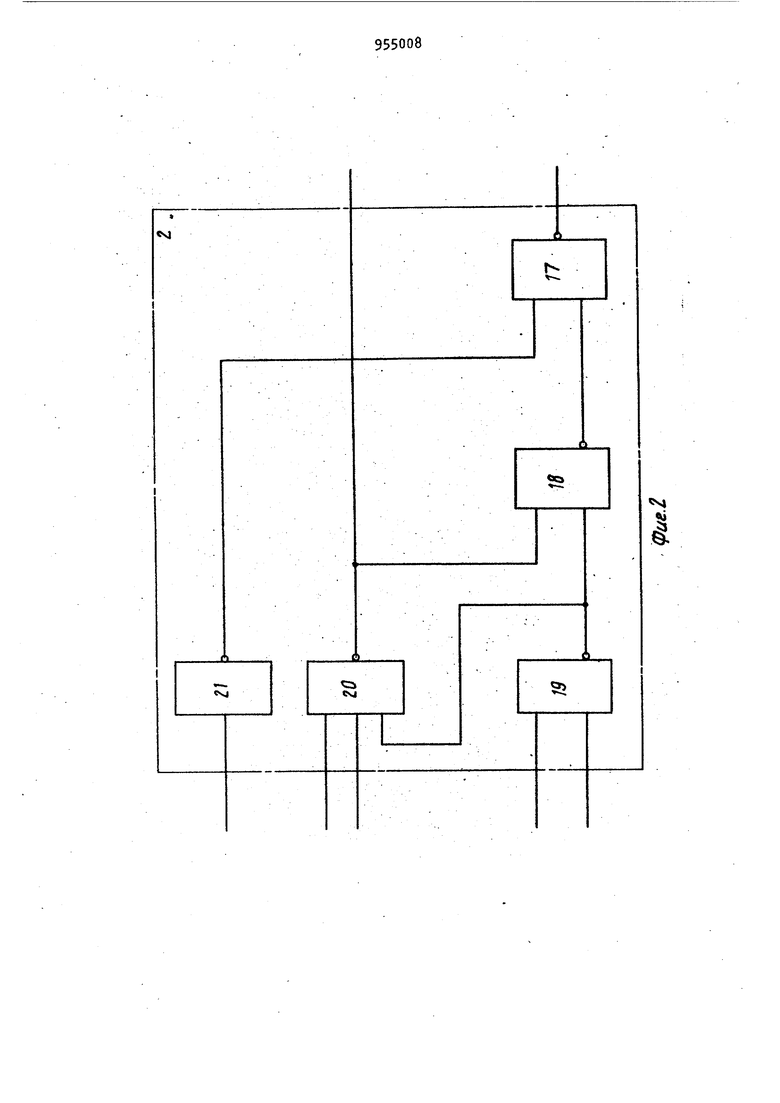

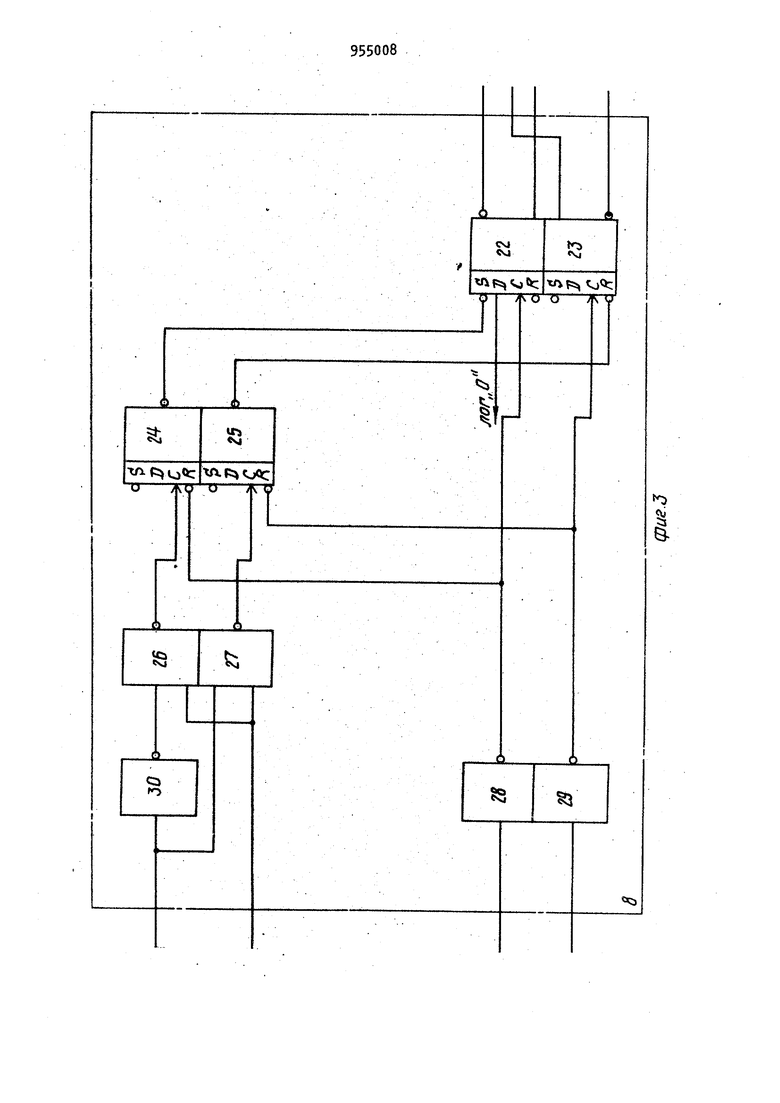

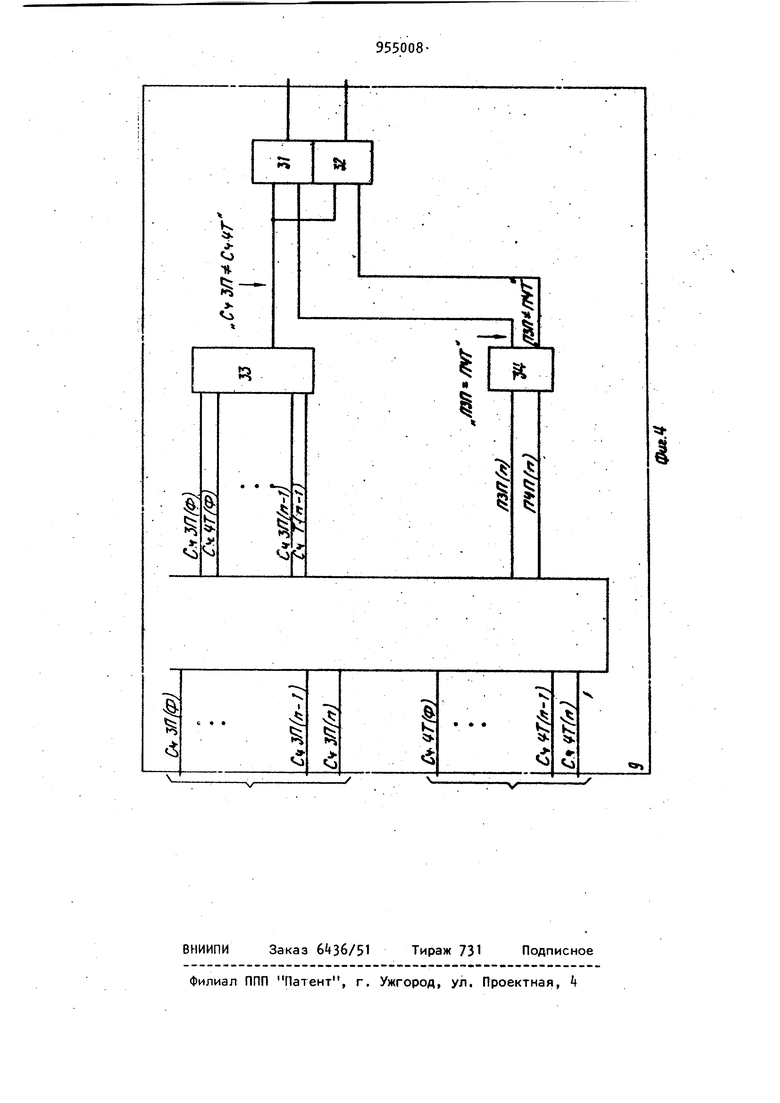

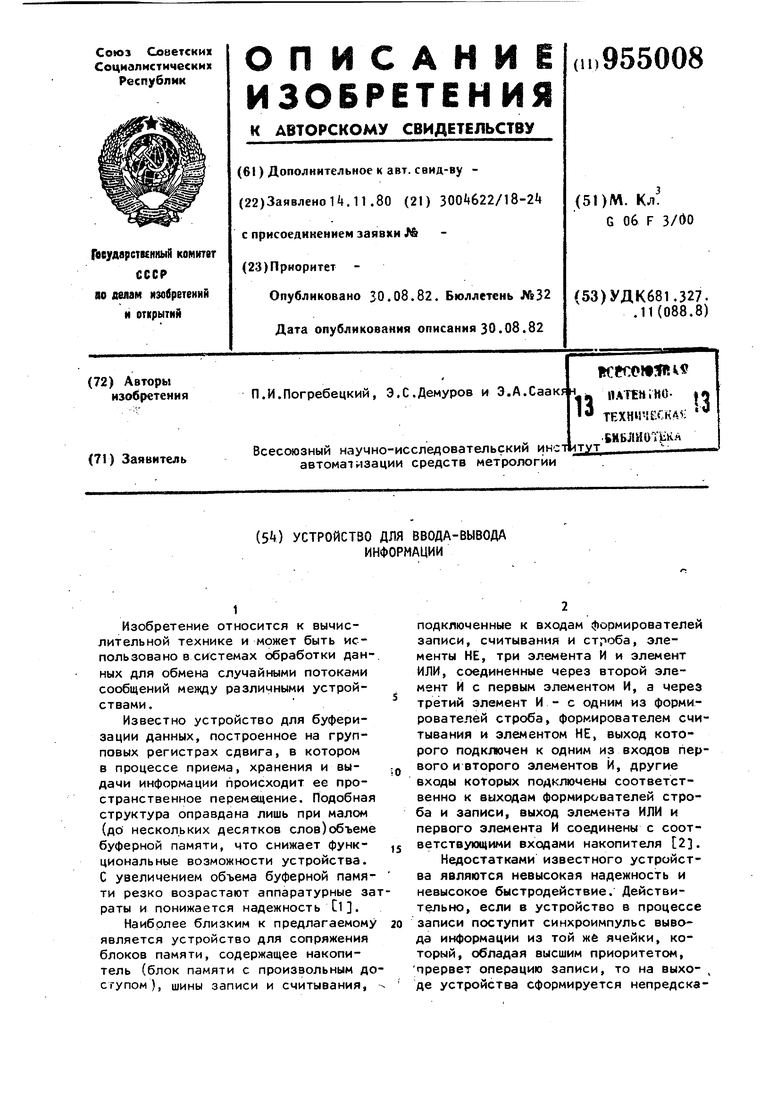

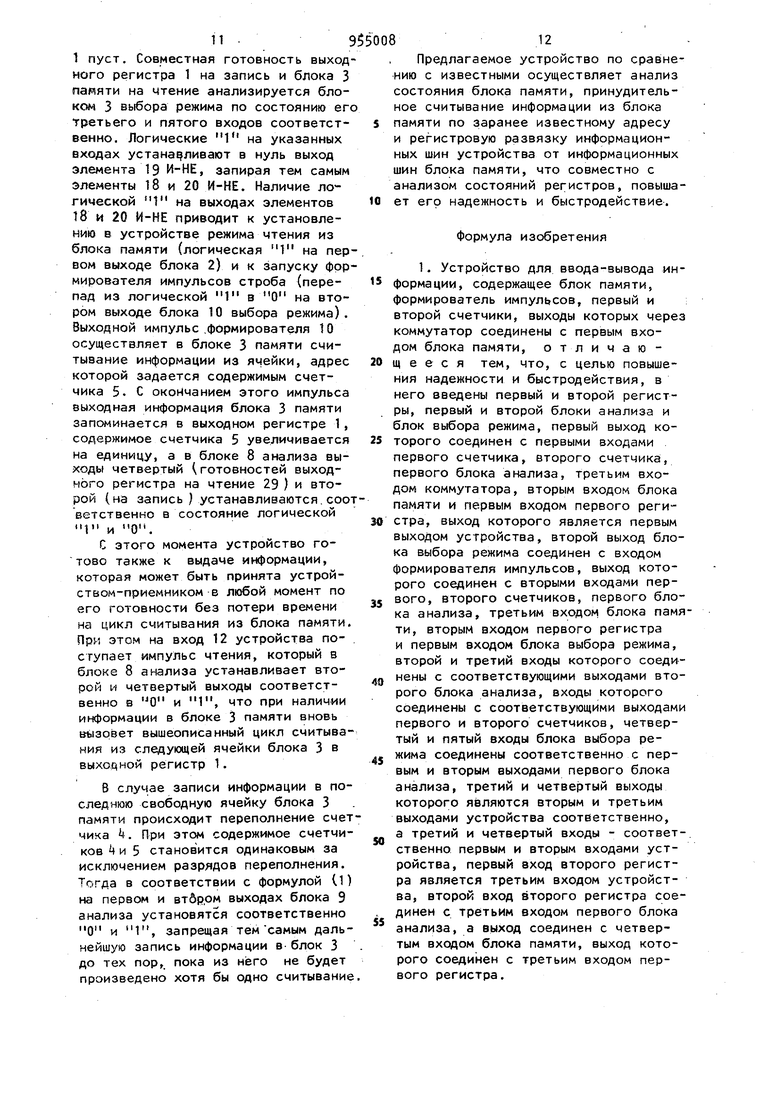

Изобретение относится к вычислительной технике и может быть использовано в системах обработки данных для обмена случайными потоками сообщений между различными устройствами. Известно устройство для буферизации данных, построенное на групповых регистрах сдвига, в котором в процессе приема, хранения и выдачи информации происходит ее пространственное перемещение. Подобная структура оправдана лишь при малом (до нескольких десятков слов)объеме буферной памяти, что снижает функциональные возможности устройства. С увеличением объема буферной памяти резко возрастают аппаратурные за раты и понижается надежность Cl . Наиболее близким к предлагаемому является устройство для сопряжения блоков памяти, содержащее накопитель (блок памяти с произвольным до ступом), шины записи и считывания, подключенные к входам формирователей записи, считывания и строба, элементы НЕ, три элемента И и элемент ИЛИ, соединенные через второй элемент И с первым элементом И, а через третий элемент И - с одним из формирователей строба, формирователем считывания и элементом НЕ, выход которого подключен к одним из входов первого и второго элементов И, другие входы которых подключены соответственно к выходам формирователей строба и записи, выход элемента ИЛИ и первого элемента И соединены с соответствующими входами накопителя 2. Недостатками известного устройства являются невысокая надежность и невысокое быстродействие. Действительно, если в устройство в процессе записи поступит синхроимпульс вывода информации из той же ячейки, который, обладая высшим приоритетом, прервет операцию записи, то на выходе устройства сформируется непредска3 .9 зуемый код. Необходимо отметить, что р. этом устройстве вообще отсутствуют средства для диагностики особых ситуаций, таких как Буфер пуст и Буфер заполнен, что, как правило, приводит к искажению передаваемой информации. Невысокое быстродействие обусловливается следующими факторами. В отсутствие синхроимпульсов ввода-выв да указанное устройство простаивает. Это обстоятельство не сказывается на быстродействии устройства по вводу, однако при выводе информации происходит неоправданная потеря аремени, равного задержке от момента поступления синхроимпульса вывода до завершения формирования кода на выходных шинах устройства. В то же время адрес ячейки, из которой предстоит считывание информации, известен заранее, и цикл считывания можно бы начинать, не дожидаясь соответ ствующего синхроимпульса вывода. Быстродействие этого устройства по вводу также невелико и практически в три раза меньше, чем быстродействие накопителя. Кроме того, непосредственная связь информационных входов-выходов устройства с накопителем снижает производительность сис темы, в которой используется известное устройство, поскольку скорость обмена данных по системным линиям связи при такой организации ограничивается быстродействием буферной па мяти. Цель изобретения - повышение быстродействия и надежности. Поставленная цель достигается тем что в устройство для ввода-вывода ин формации, содержащее блок памяти; формирователь импульсов, первый и вт рой счетчики, выходы которых через к мутатор соединены с первым входом бл ка памяти, введены первый и второй блоки анализа и блок выбора режима, п вый выход которого соединен с первым входами первого счетчика, второго счетчика, первого блока анализа, тре тьим входом коммутатора,вторым входом блока памяти и первым входом первого регистра, выход которого является первым выходом .устройства, второй выход блока выбора режима соединен с входом формирователя имп ульсов, выхо которого соединен с вторыми входами первого, второго счетчиков, первого блока анализа, третьим входом блока памяти, вторым входом первого регистра и первым входом блока выбора режима, второй и третий входы которого соединены с соответствующими выходами второго блока анализа, входы которого соединены с соответствующими выходами первого и второго счетчиков, четвертый и пятый входы блока выбора режима соединены соответственно с первым и вторым выходами первого блока анализа, третий и четвертый выходы которого являются вторым и третьим выходами устройства соответственно, а третий и четвертый входы соответственно первым и вторым входами устройства, первый вход второго регистра является третьим входом устройства, второй вход второго регистра соединен с третьим входом первого блока аколиза, а выход соединен с четвертым входом блока памяти, выход которого соединен с третьим входом первого регистра. Блок выбора режима содержит первый, второй, третий и четвертый элементы И-НЕ, первый элемент НЕ, вход которого является первым входом блока, а выход соединен с первым входом первого элемента И-НЕ, выход которого является вторым выходом блока, а второй вход соединен с выходом второго элемента И-НЕ, первый вход которого соединен с выходом третьего элемента И-НЕ, и первым входом четвертого элемента И-НЕ, второй и третий входы которого являются соответственно вторым и четвертым входами блока, а выход соединен с вторым входом второго элемента И-НЕ и является первым выходом блока, входы третьего элемента И-НЕ являются соответственно, третьим и пятым входами блока. Первый блок анализа содержит второй, третий и четвертый элементы НЕ, пятый и шестой элементы И-НЕ, первый, второй, третий и четвертый триггеры, первые выходы первого и второго триггеров являются соответственно первым и вторым выходом блока, а вторые выходы - соответственно третьим и четвертым выходами блока, первые входы первого и второго триггеров соединены с выходами третьего и четвертого триггеров соответственно, а вторые входы - с соответствующими выходами второго и третьего элементов НЕ и первыми входами третьего и четвертого триггеров, вторые входы которых соединены с соответствующими выходами пятого и шестого элементов И-НЕ, первый вход пятого элемента И-НЕ соединен с выходом чет вертого элемента НЕ, вход которого соединен с первым входом шестого эле мента И-НЕ и является первым входом блока, второй вход шестого элемента И-НЕ соединен с вторым входом пятого элемента И-НЕ и является вторым входом блока, входы второго и третьего элементов НЕ являются соответственно третьим и четвертым входами блока. Второй блок анализа содержит первую и вторую схемы сравнения, и первый и второй элементы ИЛИ, выходы ко торых являются первым и вторым выхода ми блока соответственно, а первые входы соединены с выходом первой схе мы сравнения, вторые входы первого и второго элементов ИЛИ соединены с со ответствующими выходами второй схемы сравения, входы первой и второй схем сравнения являются соответствующими входами блока. На фиг. 1 изображена структурная схема предлагаемого устройства; на фиг. 2- - пример реализации блока выбора режима; на фиг. 3 пример реализации первого блока анализа-,на фиг. - пример реализации второго блока анализа. Устройство (фиг. 1) содержит первый регистр 1, второй регистр 2, бло 3 памяти, первый счетчик k, второй счетчик 5, коммутатор 6, блок 7 выбора режима, первый блок 8 анализа, второй блок 9 анализа, формирователь 10 импульсов, первый вход 11 ус ройства, второй вход 12 устройства, третий вход 13 устройства, первый выход И устройства, второй выход 15 устройства, третий выход 16 устройства. Блок 7 выбора режима (фиг. 2) содержит первый элемент 17 И-НЕ, вто рой элемент 18 И-НЕ, третий элемент 19 И-НЕ, четвертый элемент 20 И-НЕ. первый элемент 21 НЕ. Первый блок 8 анализа (фиг. 3) ; содержит первый триггер 22, второй триггер 23, третий триггер 2, четвертый триггер 25, пятый элемент 26 И-НЕ, шестой элемент 27 И-НЕ, второй элемент 28 НЕ, третий элемент 29 НЕ, четвертый элемент 30 НЕ. Блок 8 анализа выполняет следующие функции. По команде записи информации во второй (входной) регистр 2 импульс. поступающий на третий вход блока 8, своим окончанием инициирует микрооперацию сброса готовности входного регистра 2 на запись, в результате чего на первом выходе блока устанавливается логическая единица, |сигнализирующая о готовности вход;ного регистра 2 на чтение, а на третьем выходе блока 8 - логический , нуль сигнализирующий об отсутствии готовности входного регистра 2 на запись. По команде чтения информации из первого (выходного) регистра 1 импульс, поступающий на четвертый вход блока 8 своим окончанием, инициирует микрооперацию сброса готовности выходного регистра 1 на чтение, в результате чего на втором выходе блокз 8 устанавливается логическая единица, соответствующая готовности выходного регистра 1 на запись, а на четвертом выходе блока 8 - логический нуль, сигнализирующий об отсутствии готовности выходного регистра 1 на чтение. При обращении к блоку 3 памяти импульс, поступающий на второй вход блока 8,своим окончанием инициирует при логической едйнице на первом входе (режим чтения из блока 3 памяти и записи в выходной регистр микрооперацию сброса готовности выхб ного регистра 1 на запись, в результате чего на втором -выходе блока 8 устанавливается логический нуль, а на четвертом выходе - логическая единица; при логическом нуле на первом входе блока 8 (режим записи в блок 3 памяти и чтения из входного регистра J и инициируется микрооперации сброса готовности входного регистра 2 на чтение, в результате чего на первом выходе блока 8 устанавливается логический нуль, а на третьем выходе - логическая единица. Второй блок 9 анализа (фиг. Ц) содержит первый элемент 31 ИЛИ, второй элемент 32 ИЛИ, первую схему 33 сравнения, вторую схему 3 сравнения, i многоразрядные входные информационные шины и одноразрядные выходные шины, готовности блока памяти на запись (ГТНЗП) и чтение () соответственно. Блок анализа готовйостей накопителя предназначен для распознавания особых ситуаций типа Блок памяти пуст (т.е. не готов к приему информации) и Блок памяти переполнен (т.е. готов к выдаче информации). С этой целью в блоке 9 анализируются текущие состояния первого и вто рого 5 счетчиков адресов записи и чтения согласно логическим функциям ГТНЗП СчЗП СчЧТ + ПЗП-ПЧТ, ГТНЧТ СчЗП СчЧТ+ ПЗП ПЧТ, N) где ГТНЗП - готовность блока памя-ти на запись (первый выход блока 9)J ГТНЧТ - готовность накопителя на чтение (второй выход блока 9). При ГТНЗП 0 блок памяти не готов к записи, т.е. не готов к приему информации (БЛОК памяти переполнен) при ГТНЧТ 0 блок памяти не готов к чтению, т.е. к выдаче информации (Блок памяти пуст). Востальных случаях блок памяти готов как к приему, так и,к информации. СчЗП и СчЧТ текущие адреса запи си и чтения, формируемые в счетчиках ( и 5 соответственно;СчЗП СчЧТ логическая переменная, равная логической 1 при несовпадении адресов записи и чтения и равная логическому О в противном слу чае-, логические переменные, равные логичес кой 1 при перепол нении счетчиков k и 3 (старшие разряды первой и второй групп входов блока 9); логическая переменная, равная логической 1 при равенстве переменных ПЗП и ПЧТ и равная логическому 6 в противном случае , n3n(tn4T - логическая переменная, равная инверсии логической пере . менной . Если емкость блока памяти 3 составляет 2 слов, то счетчики 4 и 5, а следовательно, и входные .шины блока 9 имеют (п+1) разрядов, а схема 3 сравнения имеет п разрядов. Раз88ряды схемы 32 сравнения по первому входу связаны с соответствующим младшими разрядами 0,...(п-1) первой группы шин, по второму входу - с разрядами второй группы шин. Схема 3 сравнения по первому входу связана со старшим разрядом первой группы входных шин блока 9,характеризующим состояние переполнения (ПЗП счетчика , а по второму входу - со старшим разрядом второй группы шин, характеризующим состояние переполнения 1ПЧТ) счетчика 5. Выходнесовпадения схемы 33 Л-погическая переменная () подключен к первым входам элементов 3 и 32 ИЛИ. Выход совпадения схемы 3 (логическая переменная ПЗП ) подключен к второму входу элемента 31 ИЛИ, а выход несовпадения схемы З () - к второму входу элемента 32 ИЛИ. Выходы элементов 31 и 32 ИЛИ являются соответствующими выходными шинами ГТНЗП и ГТНЧТ блока 9. Формирователь 10 импульсов (стробов), реагируя на перепад из логической 1 в логический О на своем входе, вырабатывает на выходе импульс , длительность которого соответствует циклу обращения к накопителю. Состояние второго 15 и третьего 1б выходов устройства готовностей входного регистра 2 на запись и выходного регистра 1 на чтение соответственно анализируется либо программно, либо аппаратно контроллером обмена. При совпадении готовностей входного регистра 2 на запись и устройства-передатчика на выдачу информации вырабатывается команда передачи информации на устройство-передатчик в описываемое устройство. При этом устройство-передатчик выставляет на третий вход 13 устройства передаваемое слово, а на первый вход 11 поступает импульс записи. При совпадении готовностей выходного регистра 1 на чтение и устройства-приемника на ввод информации вырабатывается команда передачи информации из описываемого устройства в устройство-приемник, по которой устройство-приемник стробирует информацию с первого выхода И устройства, а на второй вход 12 устройства поступает импульс чтения. Структура предлагаемого устройства такова, что при выполнении соответствующих условий допускается одновременное выполнение команд пере дачи информации из устройства-передатчика в предлагаемое устройство и из него - в устройство-приемник. Устройство работает следующим обра зом. Предварительно, покоманде началь ной установки (шина начальной установки не показана) счетчики j адресо записи и 5 адресов чтения приводятся в одинаковое состояние со Сброшенными разрядами переполнения. Без потери общности можно считать, что оба счетчика сбрасываются в ноль. Кроме того, по этой команде в уст ройстве устанавливаются состояния го товностей на запись входного 2 и выходного 3 регистров. При этом на третьем выходе блока 8 (готовностей входного регистра 2 на запись) и втором выходе (готовность выходного регистра 1 на запись) присутствует сиг нал логической единицы, а на первом выходе.блока 8 (готовностей входного регистра 2 на чтение) и четвертом выхсде блока 8 (готовность выходного регистра на чтение) - логический ноль, формирователь 10 во время начальной установки блокирован. В соответствии с логической формулой (1), реализуемой блоком 9 ана лиза, на первом выходе блока 9 (готовностей блока памяти на запись устанавливается сигнал логической 1, а на втором выходе (готовности блока памяти на чтение) - О. При этом элементы 19 и 20 И-НЕ блока 10 выбора режима заперты соответственно по первому и второму входам, элемент 18 И-НЕ открыт, а 17 И-НЕ закрыт логическим нулем, поступающим с выхода элемента 18 И-НЕ. В результате на первом и втором выходах блока 2 присутствует логическая 1. На выходе формирователя 10 присутствует логический нуль, вследствие чего в устройстве не происходит никаких действий. На выходах 15 и 16 устройства присутствуют соответственно сиг налы логической 1.и О. При этом единственно возможной является коман да передачи информации из устройства передатчика в предлагаемое устройство. При поступлении импульса записи на вход 11 осуществляется запоминание информации, присутствующей на входе 13 устройства, во входном регистре 2. С окончанием этого импульса на выходах первом (готовностей входного регистра на чтение) и третьем (готовности на запись) блока 8 анализа установятся соответственно логические 1 и О, При этом элемент 20 И-НЕ блока 2 выбора режима, предварительно подготовленный по своим первому и третьему входам, открывается, запирая Элемент 18 И-НЕ, в результате чего элемент 17 И-НЕ также открывается. На первом выходе блока 2 выбора режима устанавливается логический нуль, который по второму входу блока 3 памяти устанавливает в нем режим записи, а по третьему (адресному) входу коммутатора 6 подключает выходы счетчика к первому (адресному) входу блока 3 памяти. На втором выходе блока 2 выбора режима происходит перепад из логической 1 в О, который запускает формирователь 10, выходной импульс которого, поступая на третий синхронизирующий вход блока 3 памяти, осуществляет запись содержимого входного регистра 2,в блок 3 памяти по адресу, соответствующему содержимому счетчика 4. Одновременно этот импульс поступает на первый вход запрета блока 2 выбора режима, где через элемент 21 .НЕ запирает элемент 17 И-НЕ, устанавливая на втором выходе вновь состояние логической 1. По окончании выходного импульса формирователя 10 импульсов выбора содержимое сметчика увеличивается на единицу, первый выход (готовностей входного регистра на чтение) блока 8 и третий выход (готовности на запись) блока 8 анализа устанавливаются соответственно в состояние логического О и 1 и в соответствии с формулой (П, второй выход (готовности блока 3 памяти на чтение) блока 9 анализа перейдет в состояние логической единицы, а в блоке 2 выбора режима снимается запрет по первому входу, подготавливая через элемент 21 НЕ элемент 17 И-НЕ. Состояния.счетчика 5 и выходного регистра 1 не изменяются ввиду наличия логического нуля на прямых управляющих входах. С этого момента устройство-вновь готово к приему информации во входной регистр 2, но не готово к выдаче информации, так как выходной регистр 11 1 пуст. Совместная готовность выход ного регистра 1 на запись и блока 3 памяти на чтение анализируется блоком 3 выбора режима по состоянию ег третьего и пятого входов соответственно. Логические 1 на указанных входах устанавливают в нуль выход элемента 19 И-НЕ, запирая тем самым элементы 18 и 20 И-НЕ. Наличие логической 1 на выходах элементов 18 и 20 И-НЕ приводит к установлению в устройстве режима чтения из блока памяти (логическая 1 на пер вом выходе блока 2) и к запуску фор мирователя импульсов строба (перепад из логической 1 в О на втором выходе блока 10 выбора режима). Выходной импульс .формирователя 10 осуществляет в блоке 3 памяти считывание информации из ячейки, адрес которой задается содержимым счетчика 5. С окончанием этого импульса выходная информация блока 3 памяти запоминается в выходном регистре 1 , содержимое счетчика 5 увеличивается на единицу, а в блоке 8 анализа выходы четвертый (готовностей выходного регистра на чтение 29 ) и второй (на запись ) устанавливаются.соо ветственно в состояние логической 1 и О. С этого момента устройство готово также к выдаче информации, которая может быть принята устройством-приемником в любой момент по его готовности без потери времени на цикл считывания из блока памяти. При этом на вход 12 устройства поступает импульс чтения, который в блоке 8 анализа устанавливает второй и четвертый выходы соответственно в и 1, что при наличии информации в блоке 3 памяти вновь вызовет вышеописанный цикл считывания из следующей ячейки блока 3 в выходной регистр 1. В случае записи информации в последнюю свободную ячейку блока 3 памяти происходит переполнение счет чика . При этом содержимое счетчиков i и 5 становится одинаковым за исключением разрядов переполнения. Тогда в соответствии с формулой (1) на первом и втбррм выходах блока 9 анализа установятся соответственно О и 1, запрещая темсамым дальнейшую запись информации в-блок 3 до тех пор, пока из него не будет произведено хотя бы одно считывание Предлагаемое устройство по сравнению с известными осуществляет анализ состояния блока памяти, принудительное считывание информации из блока памяти по заранее известному адресу и регистровую развязку информационных шин устройства от информационных шин блока памяти, что совместно с анализом состояний регистров, повышает его надежность и быстродействие. Формула изобретения 1. Устройство для ввода-вывода информации, содержащее блок памяти, формирователь импульсов, первый и второй счетчики, выходы которых через коммутатор соединены с первым входом блока памяти, отличающееся тем, что, с целью повышения надежности и быстродействия, в него введены первый и второй регистры, первый и второй блоки анализа и блок выбора режима, первый выход которого соединен с первыми входами первого счетчика, второго счетчика, первого блока анализа, третьим входом коммутатора, вторым входом блока памяти и первым входом первого регистра, выход которого является первым выходом устройства, второй выход блока выбора режима соединен с входом формирователя импульсов, выход которого соединен с вторыми входами первого, второго счетчиков, первого блока анализа, третьим входом блока памяти, вторым входом первого регистра и первым входом блока выбора режима, второй и третий входы которого соеди нены с соответствующими выходами второго блока анализа, входы которого соединены с соответствующими выходами первого и второго счетчиков, четвертый и пятый входы блока выбора режима соединены соответственно с первым и вторым выходами первого блока анализа, третий и четве1этый выходы которого являются вторым и третьим выходами устройства соответственно, а третий и четвертый входы - соответственно первым и вторым входами устройства, первый вход второго регистра является третьим входом устройства, второй вход второго регистра соединен с третьим входом первого блока анализа, а выход соединен с четвертым входом блока памяти, выход которого соединен с третьим входом первого регистра. 13 2. Устройство по п. 1, отличающееся тем, что блок выбора режима содержит первый, второй, третий и четвертый элементы И-НЕ, первый элемент НЕ, вход которого является первым входом блока, а выход соединен с первым входом первого эле мента И-НЕ, выход которого является вторым выходом блока, а второй вход соединен с выходом второго элемента И-НЕ, первый вход которого соединен с выходом третьего элемента И-НЕ и первым входом четвертого элемента И-НЕ, второй и третий входы которого являются соответственно вторым и четвертым входами блока, а выход соединен с вторым входом второго эле мента И-НЕ и является первым выходом блока, входы третьего элемента И-НЕ являются соответственно третьим и пятым входами блока. 3. Устройство .по п. 1, отличающееся тем, что первый бло анализа содержит второй, третий и четвертый элементы НЕ, пятый и шестой элементы И-НЕ, первый, второй, третий- и четвертый триггеры, первые выходы первого и второго триггеров являются соответственно первым и вто рым выходом блока, а вторые выхрды соответственно третьим и четвертым выходами блока, первые входы первого и второго триггеров соединены с выходами третьего и четвертого триггеров соответственно, а вторые входы с соответствующими выходами второго и третьего элементов НЕ и первыми 81 входами третьего и четвертого тригггеров, вторые входы которых соединены с соответствующими выходами пятого и шестого элементов И-НЕ, первый вход пятого элемента И-НЕ соединен с выходом четвертого элемента НЕ, вход которого соединен с первым входом шестого элемента И-НЕ и является первым входом блока, второй вход шестого элемента И-НЕ соединен с вторым входом пятого элемента И-НЕ и является вторым входом блока, входы второго и третьего элементов НЕ яв-ляются соответственно третьим и четвертым входами блока, k. Устройство по п. 1, о т л и что второй чающееся тем, блок анализа содержит первую и рую схемы сравнения и первый и рой элементы ИЛИ, выходы которшх являются первым и вторым выходами блока соответственно, а первые входы соединены с выходом первой схемы сравнения, вторые входы первого и второго элементов ИЛИ соединены с соответствующими выходами второй схемы сравнения, входы первой и второй схемы сравнения являются соответствующими входами блока. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № , кл. G Об F 13/06, 1979. 2.Авторское свидетельство СССР №624231, кл. G Об F 13/02, 1978 (прототип),

-И АЛ

ca

«Vl

CSJ

&

5

о /и

СЭ

fo

J5

см

Csj

WiFa|4 «iC t/VPa «i::

/Ч о о 7SV

I

§s

Авторы

Даты

1982-08-30—Публикация

1980-11-14—Подача