Изобретение относится к запомина ющим устройствам.

Известно запоминающее устройство с самоконтролем, содержащее матрицу элементов памяти,-схемы логики обрамления, позволяющие производить обращение при записи и считывании информации тольк.о к одному элементу памяти матрицы 1 .

Недостатком этого устройства является низкая надежность.

Из известных устройств наиболее близким техническим решением к предлагаемому является запоминающее устройство с самоконтролем, содержащее накопитель, числовые шины которого соединены с выходами дешифратора строк , основные выходные шины - с входами блока считывания, выход которого подключен к первому входу первогосумматора по модулю два и первому входу первого блока, исправления ошибок, второй вход первого блока исправления ошибок соединен с вторым входом первого сумматора по модулю два и выходом второго блока исправления ошибок, первые и вторые входы второго блока исправления ошибок соединены соответственно с выходами блока кодирования и дополнительными выходНЕЛми шинами накопителя, первые и вторые входы блока кодирования соединены соответственно с входами и выс ходами дешифратора адреса столбца, управляющими входами блока считывания и с входами основных элементов И, подключенных к шинам записи, разрешения записи, управления и основным

Q разрядным шинам накопителя, а третий и четвертый входы первого блока исправления ошибок соединены соответственно с шинами ЗЙ.ПИСИ и разрешения записи, первый и второй выходы его с первыми и вторыми входами дополни15тельных элементов И, третьи входы которых соединены с шиной управления и первым входом выходного блока, а выходы - с дополнительными разрядными шинами накопителя, второй вход

20 выходного блока соединен с выходом первого сумматора по модулю два 2.

Недостатком этого устройства является невысокая надежность, обуслов25ленная повышенным потреблением мощности из-за одновременной записи проверочной информации во все дополнительные разряды опрашиваемого слова накопителя при обращении к дефектному

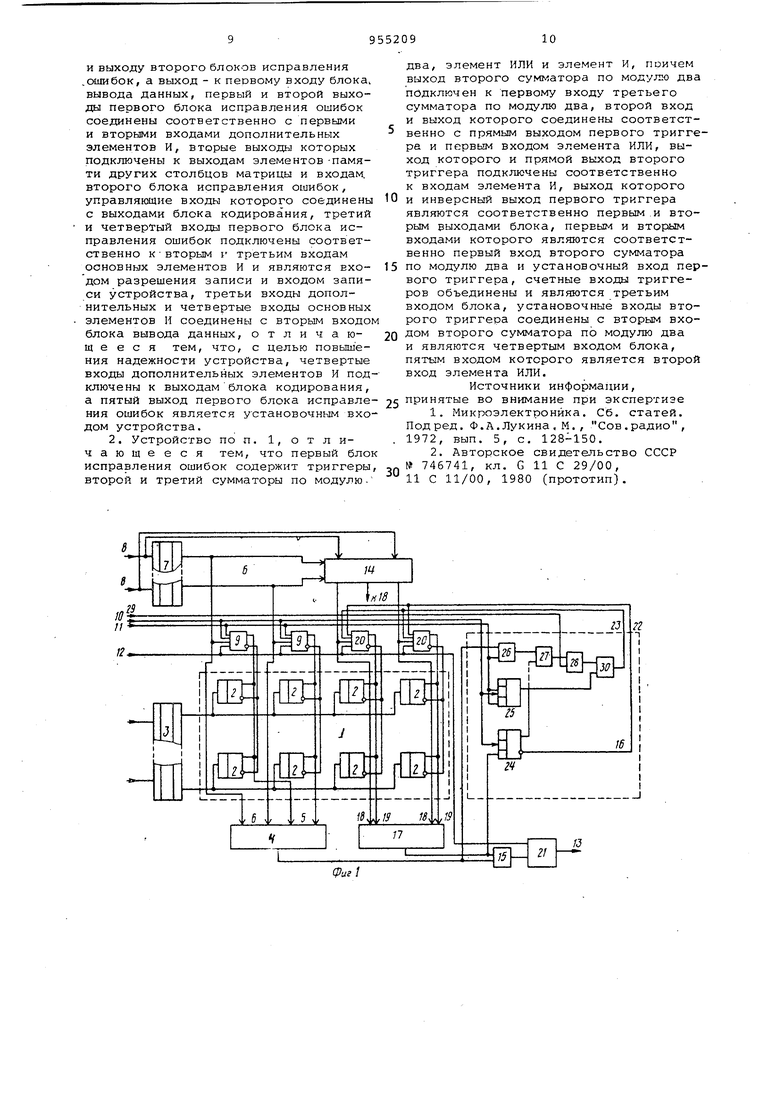

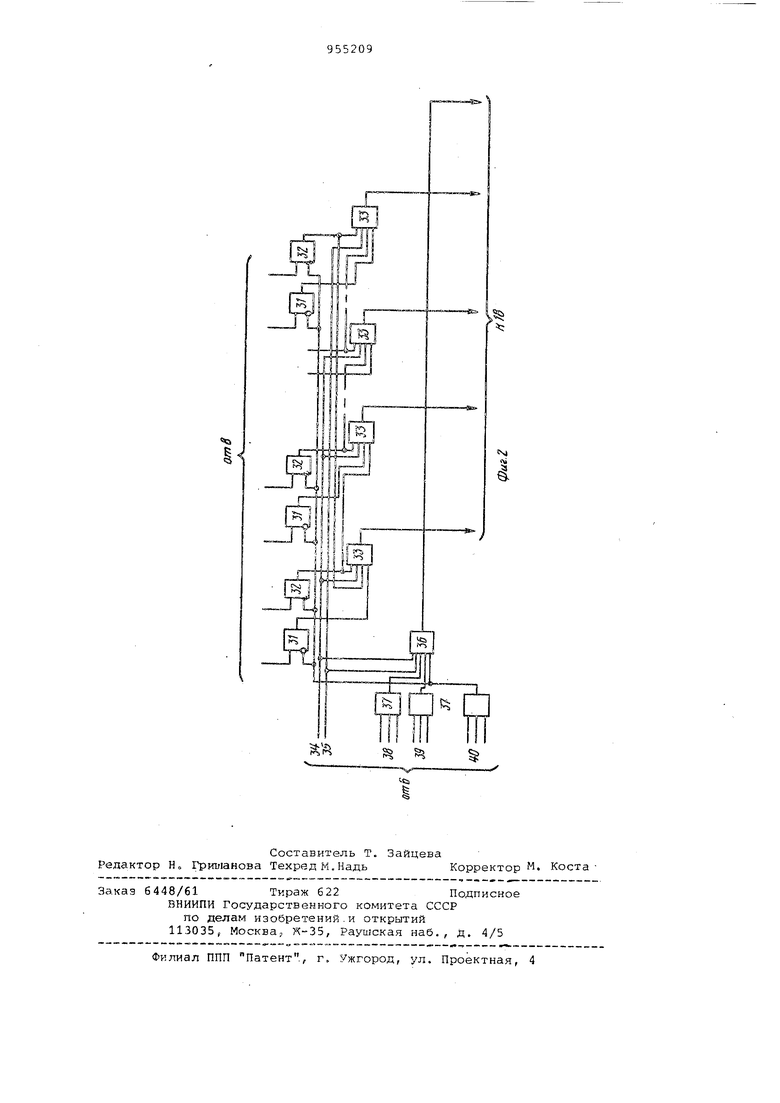

30 элементу памяти. Цель изобретения - повышение надежности устройства Поставленная цель достигается тем что в запоминающем устройстве, с само контролем, содержащем матрицу элемен тов памяти, первые входы которых соединены с выходами дешифратора адреса строк, вторые входы элементов одних из столбцов матрицы подкл чены к первым выходам основных элементов И, вторые выходы которых соединены с выходами элементов памяти одних из столбцов матрицы и входами блока считывания, вторые входы элементов памяти других столбцов матрицы подключены к первым входам дополнительных элементов И, блоки исправления ошибок, первый сумматор по модулю два, блок вывода .данных, блок кодирования и дешифратор . адреса столбцов, выходы которого подключены к первым входам основных элементов И, управляющим входам блока считывания и одним из входов блока кодирования, другие входы которого соединены с входами дешифратора адреса столбцов, первый вход первого сумматора по модулю два подключен к выходу блока считывания и первому входу первого блока исправления ошибок, вт рой вход - к второму входу первого и выходу второго блоков исправления ошибок, а выход - к первому входу блока вывода данных, первый и второй выходы первого блока исцравления ошибок соединены соответственно с первыг/1 и вторым .входами дополнительных элементов И,, вторые выходы которых подключены к выходам элементов памяти других столбцов матрицы и вхо дам второго блока исправления ошибок управляющие входы которого сое,дкнены с выходами блока кодирования, третий и четвертый входы первого блока исправления ошибок подключены соответств енно к вторыгу и к третьим входам основных элементов И и является входом разрешения записи и входом записи устройства, третьи входы дополнительных и четвертые входы основных элементов И соединены с в.торым входо блока вывода даннЕЛХ, четвертые входы дополнительных элементов И подключены к выходам блока кодирования, а пя тый выход первого блока исправления ошибок является установочным входом устройства. Первый блок исправления ошибок содержит триггеры, второй и третий сумматоры по модулю два, элемент ИЛИ и элемент И, причём выход второго сумматора по модулю два подключен к первому входу третьего сумматора по модулю два, второй вход и выход которого соединены соответственно с прямым выходом первого триггера и первым входом элемента ИЛИ, выход которого и прямой выход второго триггера подключенЕЛ соответственно к входам элемента И, выход которого и инверсный выход первого триггера являются соответственно первым и вторым выходами блока, первым и вторым входами которого являются соответственно первЕлй вход второго сумматора по модулю два и установочный вход первого триггера, счетные входы триггеров объединены и являются третьим входом блока, установочные входы второго триггера соединены с вторым входом второго сумматора по модулю два и являются четвертым входом блока, пятым входом которого является второй вход элемента ИЛИ. На фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 - функциональная схема блока кодирования, наиболее предпочтительный вариант выполнения. Устройство содержит (.фиг. 1) матрицу 1, элементы 2 памяти, дешифратор 3 адреса строк, блок 4 считывания с входами 5 и управляющими входами 6, дешифратор 7 адреса столбцов с входами 8, основные элементы И 9. На фиг. 1 обозначены вход 10 разрешения записи, вход 11 записи, управляющий вход 12 и выход 13 устройства. Устройство содержит также блок 14 кодирования, первый сумматор 15 по модулю два, первый 16 блок исправления ошибок, второй 17 блок исправления ошибок с управляющими входами 18 и 19, дополнительные элементы И 20 и блок 21 вывода данных. На фиг, 1 обозначены также первый 22 и второй 23 выходы первого блока исправления ошибок. При этом первый блок исправления ошибок содержит первый 24 и второй 25 триггеры, второй 26 и третий 27 сумматоры по модулю два, первый.элемент ИЛИ 28 с вторым входом 29 и первый элемен.т ИЗО. Блок кодирования содержит (фиг, 2) первую 31 и вторую 32 группы элементов И, первую группу элементов ИЛИ 33 с входами 34 и 35, второй элемент ИЛИ 36, вторую группу элементов ИЛИ 37 с входами 38-40, Устройство работает следующим обра 3 ом. При первоначальном включении питания (фиг. 1) элементы 2 памяти другиз4 столбцов матрицы 1 (проверочные разряды) устанавливаются в нулевое состояние единичным сигналом на входе 29 и последовательной подачей на входы 8 дешифратора 7 двух или более кодов, адреса, которые будучи преобразованными блоком 14, содержат 1 на разных позициях кода, причем за два илИ| более тактовработы хотя бы один раз

появится 1 на каждой позиции кода. После установки в исходное состояние на вход 29 подается О.

При записи информации на входы 10-12 устройства подаются сигналы разрешения записи, записи и управления. При этом происходит возбуждение шин дешифраторов 3 и 7 в соответстви с кодом адреса. Возбужденный выход дешифратора 3 подключает элементы 2 йамяти матрицы 1 к входам 5 блока 4

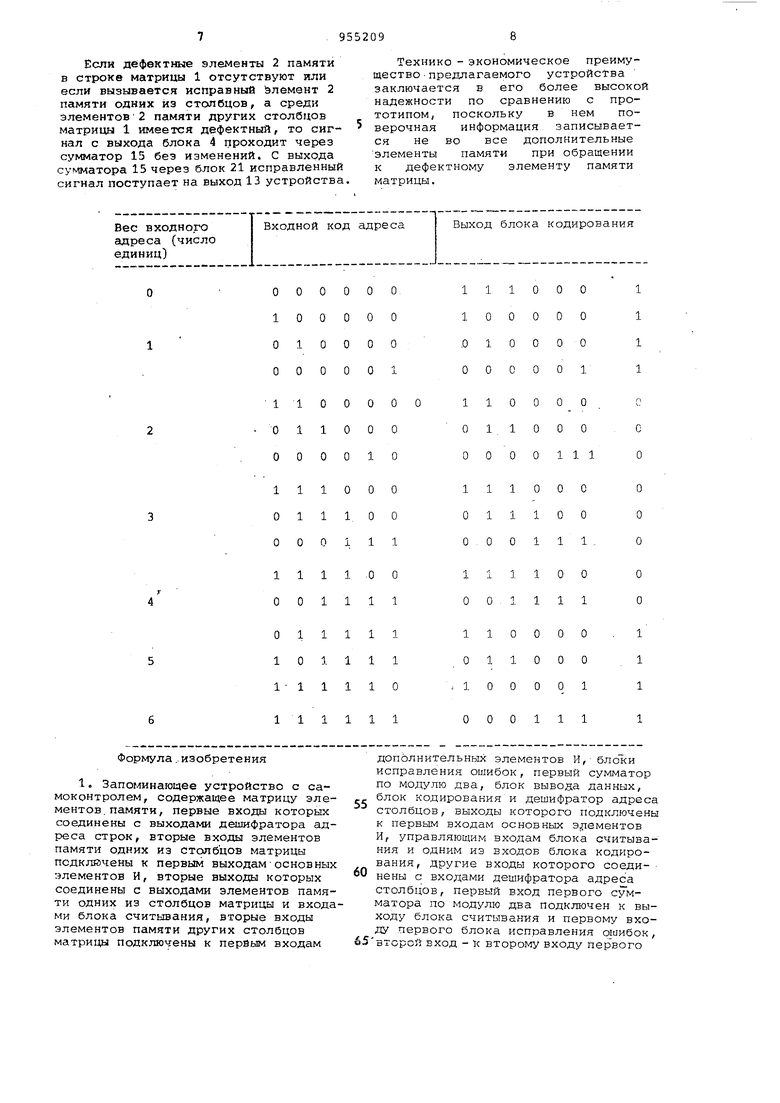

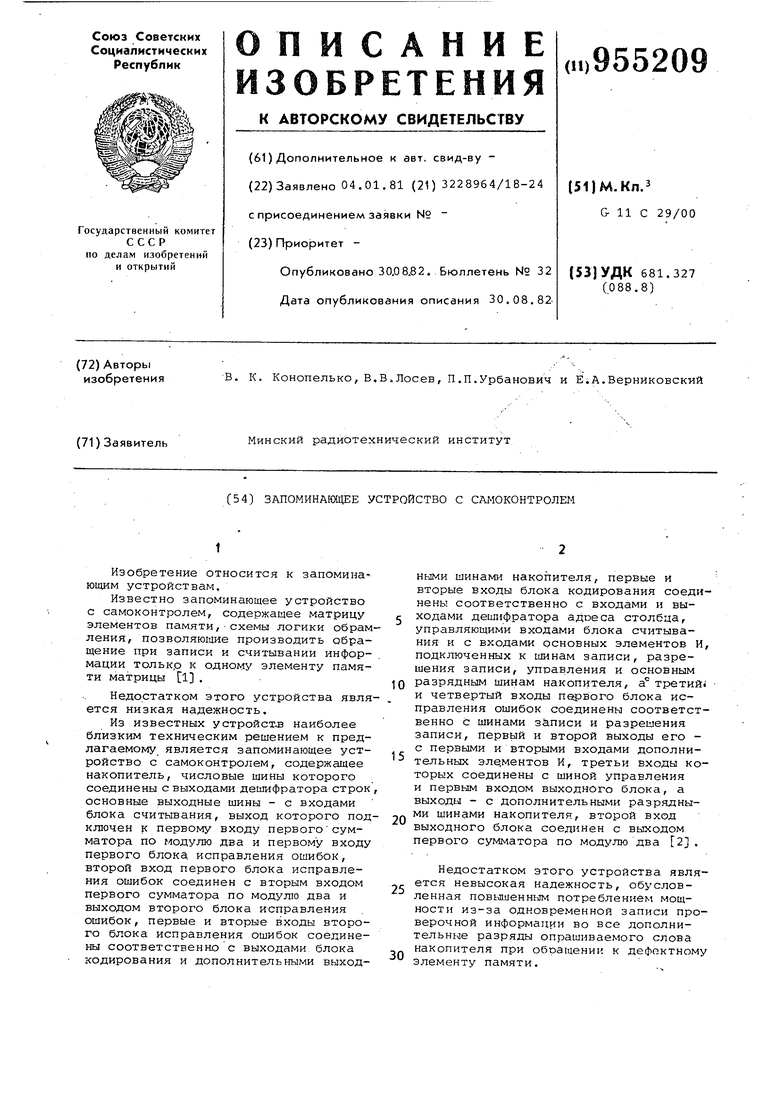

и входам 19 блока 17. При этом в элемент 2 памяти одних иэ столбцов матрицы 1, находящийся на пересечении выбранных строки к столбца, происходит запись входной информации с входа 11. Наряду с этим в блоке 14 формируются сигналы в соответствии с кодом на входах 8.дешифратора 7. Выходные сигналы блока 14 содержат не более и не менее двух единиц (.для примера в таблице показано соответствие выходных кодов блока 14 входным кодам дешифратора 7 при m 4).

Если входной код дешифратора 7 (фиг. 1) содержит одни нули - это проявляется наличием единичного сигнала на входе 34 (см. фиг. 2), если код на входах 8 содержит единицы единичный сигнал присутствует на входе 35, а если содержит одну либо более, m единиц - это фиксируется наличием единичного сигнала на выходе одного из элементов ИЛИ 37, то входной код преобразуется блоком 14 (фиг. 1 и в соответствующий из других столбцов матрицы 1 заносится единица с выхода элемента ИЛИ 36 (фиг.2 блока 14 через элемент И 20 (фиг. 1)

Сигналы с выхода блока 14 поступают на входы 18 блока 17 и сравниваются с сигналами на входах 19, считанными с элементов 2 памяти других столбцов матрицы 1 (с проверочных рарядов) , сравнения заносятся в триггер 24 (фиг. 1).

При снятии сигнала с входа 10 запись информации в опрашиваемый элемент 2 памяти одних из столбцов матрицы 1 прекращается, происходит контрольное считывание записанной информации с опрашиваемого элемента 2 памяти и сравнение ее на сумматоре 26 с инфор мацией, имеющейся на входе 11 (фиг. 1),. Одновременно с выхода триггера 25 подается сигнал разрешения записи в другие столбцы мятпипы 1 (проверочные разряды). При этом возможны следующие случаи. I

Сумматор 26 (фиг. 1) выдает единичный сигнал, а на прямом выходе триггера 24 - нулевой. Это свидетельствует о том, что опрашивается дефектный элемент 2 памяти, причем записанная для хранения информация не совпадает с состоянием элемента 2 памяти. Тогда cyMf/iaTop 27 выдает единичный сигнал, открывающий элемент И ЗОТ Тем самым на выходе элемента И 30 сформируется сигнал разрешения записи в проверочные разряды, т.е. другие столбцы матрицы 1, одновременно по адресу, cфop шpoвaннoмy блоком 14, происходит запись единичной информации с инверсного выхода триггера 24 в другие столбцы матрицы 1, заносится закодированный адрес дефектной ячейки матрицы 1.

На выходах сумматора 26 и триг-гера 24 - единичные сигналы. Это означает, что произошло повторное обращение к дефектному элементу 2 памяти для записи той же, не совпадающей с состоянием элемента 2 памяти, информации. При этомсумматор 27 выдает нулевой сигнал и элемент И 30 закрыт, причем информация, хранимая в элементах 2 памяти других столбцов матрицы 1,.остается неизменной.

На выходах сумматора 26 и триггера 24 - нулевые сигналы. Это говорит о том, что произошло обращение к исправному элементу 2 памяти одного из столбцов матрицы 1, а информация, хранимая в элементах 2 памяти других столбцов матрицы 1, не совпадает с признаком, сформированным блоком 14, соответствующим опрашиваемому столбцу матрицы 1, при этом, как и в предьщущем случае информация, хранимая в элементах 2 памяти других столбцов матрицы 1, остается неизменной. Сумматор 26 выдает нулевой сигнал, а на прямом выходе триггера 24 - единичный. Последнее-может быть при обращении к дефектному элементу 2 памяти, когда сигнал, записываемый в этот элемент 2, совпадает с символом, хранимым дефектным элементом 2, в этом случае сумматор 27 выдает единичный сигнал, открывающий элемент ИЛИ- 28 и с инверсивного выхода триггера 24 заносятся нулевые символы в т элементы 2 .памяти других столбцов опрашиваемой строки матрицы 1, которые храт.е. происходит стирание

нят

прежде записанной информации и запись нулевой информации кода, указывающей, что информация хранится правильно. В режиме считывания сигналы по входам 10 и 11 (фиг. 1) отсутствуют, при этом элементы И 9 и 20 заперты, а сигнал о состоянии опрашиваемого элемента 2 памяти матрицы 1 поступает с выхода блока 14 на первый вход сумматора 15. На второй вход сумматора 15 подается корректирующий сигнал с выхода блока 17. Если опрашивается дефектный элемент 2 памяти, то на выходе блока 17 будет единичный сигнал., который на сумматоре 15 произведет исправление сигнала, поступающего с выхода блока 4.

Если дефектные элементы 2 памяти в строке матрицы 1 отсутствуют или если вызывается исправный Элемент 2 памяти одних из столбцов, а среди элементов2 памяти других столбцов матрицы 1 имеется дефектный, то сигнал с выхода блока 4 проходит через сумматор 15 без изменений, С выхода сумматора 15 через блок 21 исправленный сигнал поступает на выход 13 устройства

Технике - экономическое преимущество предлагаемого устройства заключается в его более высоко надежности по сравнению с прототипом, поскольку в нем поверочная информация записывается не во все дополнительные элементы памяти при обращении к дефектному элементу памяти матрицы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1975 |

|

SU746741A1 |

| Запоминающее устройство матрич-НОгО ТипА C САМОКОНТРОлЕМ | 1979 |

|

SU841063A1 |

| Запоминающее устройство матричного типаС САМОКОНТРОлЕМ | 1979 |

|

SU849309A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1043743A1 |

| Запоминающее устройство | 1983 |

|

SU1107176A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU864339A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU959167A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1026165A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| Постоянное запоминающее устройство | 1975 |

|

SU733025A1 |

Формула ..изобретения

дополнительных элементов И, блоки исправления ошибок, первый сумматор по модулю два, блок вывода данных, блок кодирования и дешифратор адреса столбцов, выходы которого подключены к первым входам основных э.гтементов И, управляющим входам блока считывания и одним из входов блока кодирования, другие В.ХОДЫ которого соединены с входами дешифратора адреса столбцов, первый вход первого сч мматора по модулю два подключен к выходу блока считывания и первому входу первого блока исправления ошибок, 5Бторой вход - к второму входу первого и выходу второго блоков исправления .ошибок, а выход - к первому входу блока, вывода данных, первый и второй выходы первого блока исправления ошибок соединены соответственно с первыми и вторыми входами дополнительных элементов И, вторые выходы которых подключены к выходам элементов -памяти других столбцов матрицы и входам. второго блока исправления ошибок, управляющие входы которого соединены с выходами блока кодирования, третий и четвертый входы первого блока исправления ошибок подключены соответственно к вторым третьим входам основных элементов И и являются входом разрешения записи и входом записи устройства, третьи входы дополнительных и четвертые входы основных элементов И соединены с вторым входо блока вывода данных, отличающ е е с я тем, что, с целью повьпиения надежности устройства, четвертые входы дополнительных элементов И под ключены к выходам блока кодирования, а пятый выход первого блока исправле НИН ошибок является установочным вхо дом устройства. 2. Устройство по п, 1, о т л ичающееся тем, что первый блок исправления ошибок содержит триггеры второй и третий сумматоры по модулюдва, элемент ИЛИ и элемент И, поичем выход второго сумматора по модулю два подключен к первому входу третьего сумматора по модулю два, второй вход и выход которого соединены соответственно с прямым выходом первого триггера и первым входом элемента ИЛИ, выход которого и прямой выход второго триггера подключены соответственно к входам элемента И, выход которого и инверсный выход первого триггера являются соответственно первым и вторым выходами блока, первым и входами которого являются соответственно первый вход второго сумматора по модулю два и установочный вход первого триггера, счетные входы триггеров объединены и являются третьим входом блока, установочные входы второго триггера соединены с вторым входом второго сумматора по модулю два и являются четвертым входом блока, пятым входом которого является второй вход элемента ИЛИ. Источники информации, принятые во внимание при экспертизе 1.Микроэлектроника. Сб. статей. Под ред. Ф.А.Лукина. М. , Сов.радио, 1972, вып. 5, с. 128-150. 2.Авторское свидетельство СССР № 746741, кл. G 11 С 29/00, 11 С 11/00, 1980 (прототип).

Авторы

Даты

1982-08-30—Публикация

1981-01-04—Подача