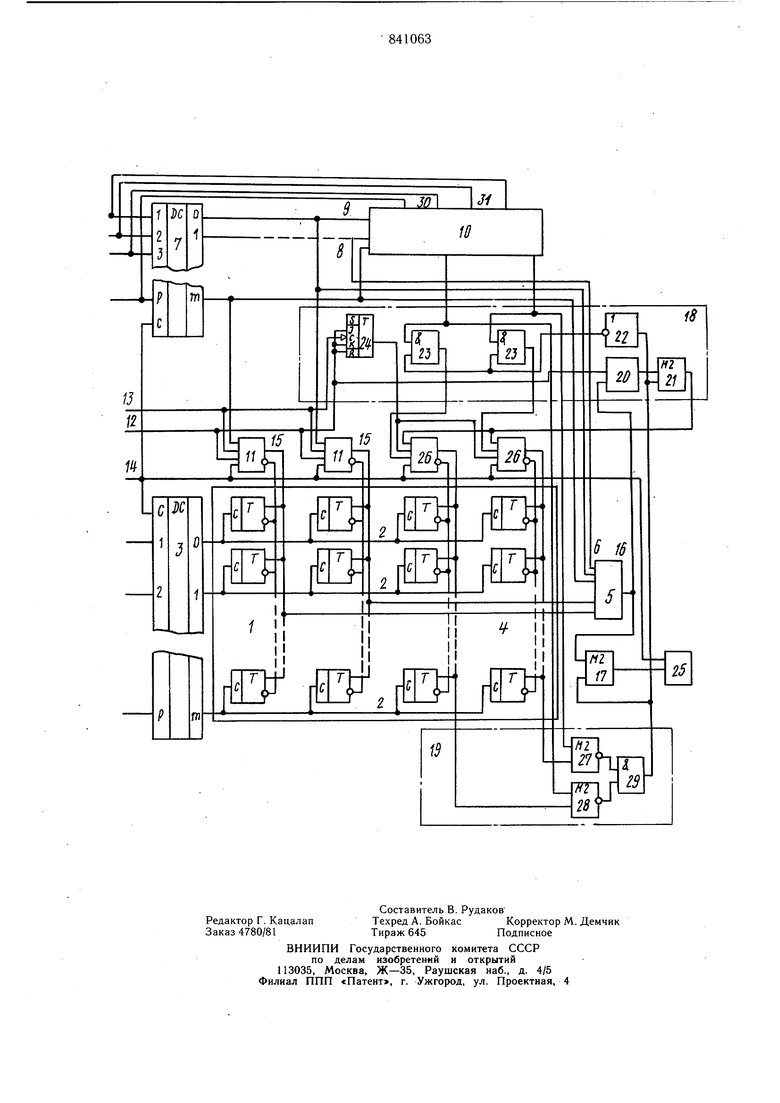

(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО МАТРИЧНОГО ТИПА С САМОКОНТРОЛЕМ Цель изобретения - повышение надеж ности устройства. Поставленная цель достигается тем, что в запоминающем устройстве матричного типа с самоконтролем, содержащем накопитель, дешифратор столбцов, дешифратор строк, блок кодирования, первый и второй блоки коррекции, сумматор по модулю два, блок считывания, блок информации, основные и дополнительные элементы И, причем числовые шины накопителя соединены с выходами дешифратора строк, выходные шины - соответственно с входами блока считывания и одними из входов второго блока коррекции, другие входы которого подключены к выходам блока кодирования, один из входов сумматора по модулю два подключен к выходу блока считывания, другой - к выходу вт(.)рого блока ко)рекц.ии, а выходк oAtiOMv из гзходов блока вывода информаЯ.ИИ, другой йход которого соединен с одной из 1ПИП управления, выходы дешифратора строк 1 о;1ключены к одним из входов б.юка кодырования, управляющим входал блока счг.тывания и одним из входов основных элердентов И, другие иходь которых соединены с тинами управления, соответстеенно, входы первого блока коррекции подключены к вь ходам блока код 1рования. одним из iiiHii управления и выходам блока считывания и второго блока коррек 1ии, а выходь: --- к о;и-1ИУ1 из входов дополнительных элементов И, дрлгие входы которых соеди1, с одной из шин у 1равления. вььчоды эле чмггов И соед.инены с разрядными шинами паконителя. другие входы блока коррекции -сое,,инеп с входами деишфратора столб1чр()ме того, целесообразно блок кодирования выполнять в виде блока, содержаще го элементы ИЛИ, одни из входов которых объединены и являются одним из входов блока кодирования, другие входы которого подключены к другим входам элементов ИЛИ, вь ходь; которых являются одними из выходов блока кодирования, другие В1)Гходы которого яв;1яются ОДНИМ -; из входов блока коднгювания. .е) блок 1чОррекции целесообразно вь,и1олнять в виде блока, содержащего триггер, элементы И, элемент НЕ и первый и второй сумматоры но моду.лю два, причем выход первого сумматора по модулю два соединен с нервым входом вто)ого сумматора по модулю два, первые входы элементов И подключены к выходу элемента НЕ, первый вход первого сумматора по модулю два объединен с одними из входов триггера, а второй вход BTOpoio сумматора по модулю двас входом элемента НЕ и являются одними из входов первого блока коррекции, другими входами которого являются вторые входы элементов И и первого сумматора цо-модулю два н другой вход триггера, выходы триггера, ЭоЧел егггов И и второго сумматора по 84 4 модулю два являются выходами первого блока коррекции. На чертеже изображена структурная схема запоминающего устройства матричного тина с самоконтролем. Устройство содержит накопитель 1, имеющий числовые щины 2, соединенные с выходами дешифратора 3, и -выходные шины 4, блок 5 считывания, имеющий управляющие входы 6, дешифратор 7 столбцов, выходы которого соединены с входами 8 и 9 блока 10 кодирования, основные элементы ПИ, щины 12-14 управления,слу-жащие, соответственно, для подачи сигналов записи, разрешения записи и обращения. Накопитель 1 содержит разрядные шины 15, блок 5 имеет выход 16. Кроме того, устройство содержит сумматор 17 по модулю два, первый 18 и второй 19блоки коррекции. Блок 18 содержит первый 20 и второй 21 сумматоры по модулю два, элемент 22 НЕ, элементы 23 И, триггер 24. Устройство также содержит блок 25 вывода информации, дополнительные элементы 26 И. Блок 19 содержит сумматоры 27 и 28 по модулю два и элемент 29 И. Блок 10 кодирования содержит элементы ИЛИ, одни из входов котор.ых обгединены и подключены ко входу 9. Входы 8 и 30 блока 10 подключены к другим входам элементов ИЛИ, выходы которых являются одними из выходов блока 10, другие выходы которого являются входами 31 блока 10. Входы 30 и 3 блока 10 подключены к входам дешифратора 7. В блоке 18 коррекции выход сумматора 20соединен с первым входом сумматора 21. Нервые входы элементов 23 И подключены к выходу элемента 22 НЕ. Первый вход сумматора 20 объединен с одним из входов триггера 24, а второй вход сумматора 21 - с входом элемента 22 НЕ и являются одними из вхо.аов блока 18, другими входами которого являются вторые входы элементов 23 ll и сумматора 20 и другой вход триггера 24. 13ыходы триггера 24, элементов 23 И и су.мматора 21 являются выходами блока 18. Устройство работает следуюп.1,им образом. При записи информации на соответствующие шины 12-14 нодаются сигналы заниси, разрешения записи и обращения. При этом Г1роисхо.дит возбуждёгше входов дешифраторов 3 и 7 в соответствии с кодом адреса. Возбужденный вы.ход дешифратора 3 строк подключает элементы памяти накопителя 1 выбранного слова к разрядным шинам 15. При этом в элемент памяти накопителя 1, находящийся на пересечении выбранной строки и столбца, нроисходит запись входной информации. При СНЯТИИ сигнала разрешения записи с н;ины 13 запись информации в опрашиваемый элемент памяти накопителя 1 прекращается и происходит контрольное считывание записанной информации с опрашиваемого элемента памяти накопителя 1 и сравнение ге на сумматоре 20 с информацией, имеющейся на шине 12. Наряду с этим двоичный сигнал адреса опрашиваемого разряда, имеющийся на входе дешифратора 7, поступает на входы 30 и 31 блока 10 кодирования. На входы 8 блока 10 кодирования поступают сигналы с выходов дешифратора 7, соответствующие входным адресам, содержащим одну единицу в адресе (10..0,01,.01..0,...,00..1). На вход 9 блока 10 кодирования поступает сигнал с выхода дешифратора 7, соответствующий нулевому входному адресу 00...0. Эти сигналы, поступая на элементы ИЛИ, а также непосредственно на выход блока. 10 формируют на выходах блока 10 сигналы, соответствующие синдромам кода Хемминга информационных разрядов, т. е. формируются все двоичные числа размерности г (о(ги+ 1), где п - общая длина слова, за исKv ючeниeм чисел, содержащих одну единицу, и нулевого числа. При этом возможны следующие случаи: 1.Опрашивается разряд накопителя 1, соответствующий входному адресу, содержащему любое из двоичных чисел длины ш г - I за исключением чисел, содержащих одну единицу в адресе, и нулевого числа. При этом на входы 8 и 9 блока 10 поступают нулевые сигналы, а следовательно, на выходах блока 10 кодирования повторяется число, имеющееся на входе дещифратора 7, дополненное нулевым сигналом с выхода элемента ИЛИ. 2.Опрашивается разряд накопителя, соответствующий входному адресу, содержащему одну единицу. При этом на один из входов 8 блока 10 поступает единичный сигнал, на вход 9 - нулевой сигнал. Тогда на выходах блока 10 кодирования повторяется число, имеющееся на входе дещифратора 7, дополненное единичным сигналом с выхода элемента ИЛИ. 3.Опрашивается разряд накопителя, соответствующий нулевому входному адресу. При этчэм на входы блока 10 поступают нулевые сигналы, а на вход9 - единичный сигнал, и следовательно, на выходы блока 10 поступает нулевое число, инвертированное в двух разрядах и дополненное единичным сигналом с выхода элемента ИЛИ. Таким образом, в блоке 10 кодирования формируются различные двоичные числа, за исключением чисел, содержащих одну единицу, и нулевого числа. Сформированные в блоке 10 сигналы поступают на входы элементов 23 И и входы первого блока 19 коррекции, где сравниваются с сигналами, поступаюцХими с выходных шин накопителя 1. При этом возможны следуюшие случаи: 1. Сумматор 20 выдает единичный сигнал, а на выходе блока 19 - нулевой сигнал. Т. е. опрашиваетсн дефектный эле.мент памяти матрицы, а информация, хранимая в дополнительных элементах памяти накопителя 1, не совпадает с синдромом, соответствующим опрашиваемому разряду, сформированным блоком 10 кодирования. При этом сумматор 21 выдает единичный сигнал, открывающий элементы 26 И. Элемещ-ы 23 И открыты единичным сигналом с элемента 22 НЕ, и сигналы, соответствующие синдрому опрашиваемого разряда, сформированные блоком 10 кодирования, заносятся для хранения в дополнительные элементы памяти накопителя 1. 2.На выходе сумматора 20 и блока 19 единичные сигналы. Это означает, что происходит повторное обращение к дефектному элементу памяти накопителя 1 для записи той же информации, что хранится в этом элементе. При этом сумматор 21 выдает нулевой сигнал, в результате элементы 26 И закрыты и информация, хранимая в дополнительных элементах памяти накопителя 1, остается неизменной. 3.На выходе сумматора 20 и блока 19 нулевые сигналы, т. е. обращение к исправному элементу памяти накопителя 1, а информация, хранимая в дополнительных элементах памяти накопителя 1, не совпадает с синдромом, соответствующим опрашиваемому разряду. При этом как и в предыдущем случае, информация, хранимая в дополнительных элементах памяти накопителя 1, остается неизменной. 4.Сумматор 20 выдает нулевой сигнал, а на выходе блока 19 - единичный. После.днее может быть при первом обращении к исправному элементу памяти накопителя 1 за счет того, что при включении напряжения питания дополнительные элементы памяти накопителя 1 устанавливаются в кодовую комбинацию, соответствующую опращиваемому исправному разряду, или при обращении к неисправному элементу памяти накопителя 1, когда символ, записываемый в этот элемент, совпадает с символом, хранимым неисправным элементом. В этом случае сумматор 21 выдает единичный сигнал, открывающий элементы 26 И, а с выхода элемента 22 НЕ через элементы 23 И заносятся нулевые символы во все дополнительные элементы па.мяти накопителя 1 опрашиваемого слова, т. е. происходит: стирание прежде записанной информации и запись нулевой комбинации кода, указывающей, что информация хранится правильно. Для исключения возможности неверной записи проверочной информации в дополнительные элементы памяти накопителя 1 во время переходных процессов на элементы 26 И подается сигнал с выхода триггера 24, появляющийся только после снятия сигнала на шине, когда переходные процессы в опрашиваемо.м элементе памяти накопителя 1 затухают.

В режиме считывания сигналы по шинам 12 и 13 отсутствуют. При этом элементы 11 и 26 И, заперты, а сигнал о состоянии опрашиваемого элемента памяти накопителя 1 поступает с выхода 16 блока 5 считывания на вход сумматора 17. На другой вход этого сумматора подается корректируюший сигнал с выхода блока 19.

При этом, если опрашивается дефектный элемент памяти накопителя 1, код, снимаемый с выходов блока 10 кодирования совпадает с информацией, хранимой в дополнительных элементах памяти накопителя 1 опрашиваемого слова, и на выходе блока 19 появляется единичный сигнал. Этот сигнал на сумматоре 17 производит исправление сигнала, поступаюш,его с выхода 16 блока 5 считывания.

Если вызывается исправный элемент памяти накопителя 1, а среди дополнительных элементов памяти накопителя 1 имеется дефектный, то информация, считываемая с дополнительных элементов памяти накопителя 1 содержит комбинации вида 00..О, О О, 01, 1 0..0, и. не совпадает с кодом, сформированным блоком 10 кодирования. В результате сигнал с выхода блока 5 считывания проходит через сумматор 17 на блок 25 без изменения.

То же происходит, если дефектные элементы памяти в слове накопителя 1 отсутствуют или состояние дефектного элемента памяти совпадает с хранимым состоянием.. Исправленный сигнал с выхода сумматора 17 через блок 25 поступает на выход устройства.

Таким образом, предлагаемое устройство требует для своей реализации меньшего числа элементов схем контроля, чем известное.

Формула изобретения

1. Запоминаюш,ее устройство матричного типа с самоконтролем, содержапдее накопитель, дешифратор столбцов, дешифратор строк, блок кодирования, первый и второй блоки коррекции, сумматор по модулю два, блок считывания, блок вывода информации, основные и дополнительные элементы И, причем числовые шины накопителя соединены с выходами дешифратора строк, выходные шины - соответственно с входами блока считывания и одними из входов второго блока коррекции, другие входы которого подключены к выходам блока кодирования, один из входов сумматора по модулю два подключен к выходу блока считывания, другой - к выходу второго блока коррекции, а выход - к одному из входов блока вывода информации, другой вход которого соединен с одной из шин управления, выходы дешифратора строк подключены к одним из входов блока кодирования, управляюш,им входам блока считывания и одним из входов основных элементов И, другие входы которых соединены с шинами управления, соответственно, входы первого блока коррекции подключены к выходам блока кодирования, одним из шин управления и выходам блока считывания и второго блока коррекции, а выходы - к одним из входов дополнительных элементов И, другие входы которых соединены с одной из шин управления, выходы элементов И соединены с разрядными шинами накопителя, отличающееся тем, что, с целью повышения надежности устройства, в нем другие входы блока коррекции соединены с входами дешифратора столбцов.

2.Устройство по п. 1, отличающееся тем, что блок кодирования содержит элементы ИЛИ, одни из входов которых объединены и являются одним из входов блока кодирования, другие входы которого подключены к другим входам элементов ИЛИ, выходы которых являются одними из выходов блока кодирования, другие выходы которого являются одними из входов блока кодирования.

3.Устройство по п. 1, отличающееся тем, что первый блок коррекции содержит триггер, элементы И, элемент НЕ и первый и второй сумматоры по модулю два, причем выход первого сумматора по модулю два соединен с первым входом второго сум.матора по модулю два, первые входы элементов И подключены к выходу элемента НЕ, первый вход первого сумматора по модулю два объединен с одними из входов триггера, а второй вход второго сумматора по модулю два - с входом элемента НЕ и являются одними из входов первого блока коррекции, другими входами которого являются вторые входы элементов И и первого сумматора по модулю два и другой вход триггера, выходы триггера, элементов И и второго сумматора по модулю два являются выхода.ми первого блока коррекции.

Источники информации, принятые во внимание при экспертизе

1.Микроэлектроника, Под ред. Ф. А. Лукина, М., «Советское радио, 1972, вып. 5, с. 128-150.

2.Авторское свидетельство СССР по заявке № 2180536/18-24, кл. G 11 С 11/00, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1981 |

|

SU1010654A1 |

| Запоминающее устройство матричного типаС САМОКОНТРОлЕМ | 1979 |

|

SU849309A1 |

| Запоминающее устройство | 1975 |

|

SU746741A1 |

| Запоминающее устройство | 1975 |

|

SU598118A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU955209A1 |

| Запоминающее устройство | 1975 |

|

SU602995A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU959167A1 |

| Запоминающее устройство | 1981 |

|

SU1014042A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU877614A1 |

| Запоминающее устройство | 1975 |

|

SU714496A1 |

Авторы

Даты

1981-06-23—Публикация

1979-09-10—Подача