1

Изобретение относится к электротехнике и предназначено для использования в быстродействующих цифровых микросхемах на переключателях тока, использующих пониженное напряжение питания, а также в схемах с токовым питанием, например, инжекционной логике.

Известны схемы стабилизаторов для транзисторно-резистивных источников постоянного тока, используемые в переключателях тока, состоящие из транзисторно-резисторного или диодно-резисторного делителя напряжения, осуществляемого температурную компенсацию тока и задающего через выходной эммитерный повторитель необходимое смещение на базу транзистора источника Cl, 23.

Существенным недостатком таких стабилизаторов является зависимость тока источника от напряжения питания и температуры, что приводит к разбросу параметров быстродействующих цифровых микросхем и сужению области из работоспособности.

Наиболее близким к изобретению техническим решением является стабилизатор постоянного тока, содержащий шесть транзисторов и шесть резисторов , причем база и коллектор первого транзистора соединены с первым выводом первого резистора,

JU эмиттер второго транзистора через второй резистор соединен с первой шиной питания, а коллектор - с базой третьего транзистора и через третий резистор - с эмиттером четвертого

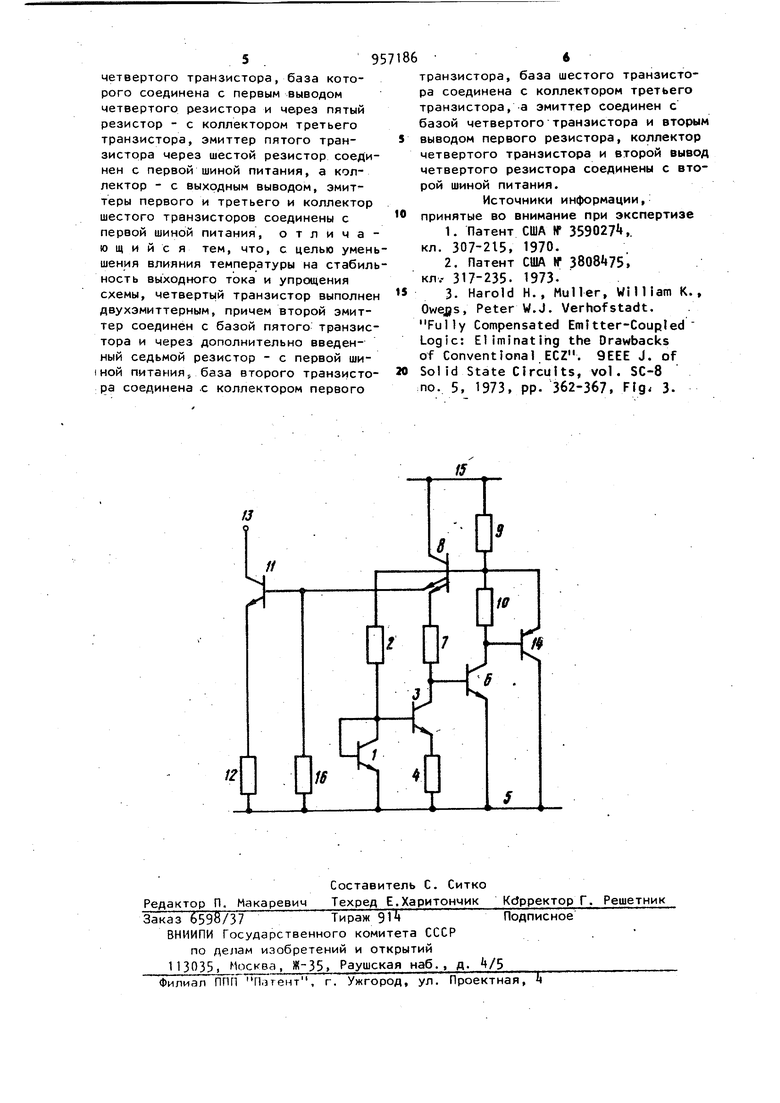

,5 транзистора, база которого соединена с первым выводом четвертого резистора и через пятый резистор - с коллектором третьего транзистора, эмиттер пятого транзистора через шестой резистор соединен с первой шиной питания, а коллектор - с выходным выводом, эмиттеры первого и третьего и коллектор шестого транзисторов соединены с первой шиной питания СЗ. Недостатком является сложность схемы, значительное влияние температуры на стабильность тока на выходе, что не позволяет использовать его в быстродействующих цифровых микросхемах на переключателях тока с пониженным напряжением питания и малым логическим перепадом, а также в схемах с токовым питанием. Цель изобретения - уменьшение вли иия температуры на стабильность выхо ного тока и упрощение схемы стабилизатора тока. . Указанная цель достигается тем, что четвертый транзистор выполнен двухэмиттерным, причем второй эмитте соединен с базой пятого транзистора и через дополнительно введенный седьмой резистор - с первой шиной пи тания, база второго транзистора соед нена с коллектором первого транзисто ра, база шестого транзистора соедине на с коллектором третьего транзистора, а эмиттер соединен с базой четвертого транзистора и вторым выводом первого резистора, коллектор четвертого- транзистора и второй вывод нетвертого резистора соединены с второй шиной питания. На Чертеже представлена принципиальная электрическая схема стабилиза тора постоянного тока. Стабилизатор содержит транзистор 1, база и коллектор которого соединены с резистором 2. Эмиттер транзис тора 3 через резистор 4 соединен с шиной 5 питания, а коллектор соединен с базой транзистора 6 и через ре зистор 7 - с первым эмиттером транзистора 8, База транзистора 8 соединена с резистором 9 и через резистор 10 - с коллектором транзистора 6. Эмиттер транзистора 11 через резистор 12 соединен с шиной 5 питания, а коллектор - с выходным выводом 13- Эмиттеры транзисторов 1 и 6 и коллектор транзистора k соединены с шиной 5 питания. База транзистора 1 соединена с коллектором транзистора 6, а эмиттер соединен с базой тран зистора 8 и резистором 2. База транзист .ра 3 соединена с коллектором транзис тора 1. Коллектор транзистора 8 и ре зистор 9 соединены с шиной 15 пита,ния, база транзистора 11 соединена с вторым эмиттером транзистора .8 и через резистор 16 - с шиной 5 питания. . Стабилизатор работает следующим образом. При подаче напряжения на шины и 15 питания через резисторы 2 и 7 протекают токи разной величины, причем ток через резистор 2 больше тока 1 через резистор 7. Величина этого тока, определяемая выражением 1 (0-053 (3)J/R, где ибэ - падение напряжения между базой и эмиттером транзисторов 1 и 3 . R - величина., сопротивления резистора k, очень,мало зависит от изменения напряжения гтитания. Поэтому потенциал базы транзистора 6 и потенциал первого эмиттера транзистора 8 отличаются на постоянную величину - падение напряжения на резисторе 7- Изменение напряжения питания приводит к изменению напряжения Ugg транзистора 6 и тока через транзисторы 6 и 1. При этом падение напряжения на резисторе 9 изменяется , почти на такую же величину, как и напряжение питания. Изменение падения напряжения на резисторе 9 через эмиттерный повторитель на транзисторе 8 передается на базу транзистора 11, в результате падение напряжения на резисторе 12 и, следовательно, величина тока на токовом выходе 13 оказывается неизменным. При изменении температуры ток через резистор 9 изменяется с постоянной .-гв результате падение напряжения на резисторе 12 не меняется, что и обеспечивает постоянство тока на токовом выходе 13. Предлагаемый стабилизатор позволяет по сравнению с известным значительно уменьшить влияние температуры на стабильность тока на-токовом выходе стабилизатора и упростить по числу компонентов схему, сохранив свойственную известному стабилизатору высокую стабильность тока при изменении напряжения питания в широких пределах. Формула изобретения Стабилизатор постоянного тока, содержащий шесть транзисторов и шесть резисторов, причем база и колг лектор первого транзистора соединены с первым выводом первого резистора, эмиттер второго транзистора через второй резистор соединен с первой шиной питания, а коллектор с базой третьего транзистора и через третий резистор - с эмиттером

четвертого транзистора, база которого соединена с первым выводом четвертого резистора и через пятый резистор - с коллектором третьего транзистора, эмиттер пятого транзистора через шестой резистор соединен с первой шиной питания, а коллектор - с выходным выводом, эмиттеры первого и третьего и коллектор шестого транзисторов соединены с первой шиной питания, отличающийся тем, что, с целью уменьшения влияния температуры на стабильность выходного тока и упрощения схемы, четверть1й транзистор выполнен двухэмиттерным, причем второй эмиттер соединен с базой пятого транзистора и через дополнительно введенный седьмой резистор - с первой шиI ной питания 5 база второго транзистора соединена .с коллектором первого

транзистора, база шестого транзистора соединена с коллектором третьего транзистора, а эмиттер соединен с базой четвертого транзистора и вторым выводом первого резистора, коллектор четвертого транзистора и второй вывод четвертого резистора соединены с второй шиной питания.

Источники информации, принятые во внимание при экспертизе

1.Патент США (f 35902, кл. 307-215, 1970.

2.Патент США № 3808475 кл.. 317-235. 1973.

3.Harold Н., Muller, William К., Owejjs, Peter W.J. Verhofstadt. Fully Compensated Emitter-Coupled Logic: Eliminating the Drawbacks

of Conventional ECZ. 9EEE J. of Solid State Circuits, vol. SC-8 no. 5, 1973, pp. 362-367. Fig. 3.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов управления | 1985 |

|

SU1290501A1 |

| Формирователь сигналов записи и считывания | 1983 |

|

SU1113852A1 |

| ТТЛ-инвертор | 1984 |

|

SU1269252A1 |

| Логический элемент | 1985 |

|

SU1262717A1 |

| Дифференциальный усилитель | 1983 |

|

SU1124427A1 |

| Транзисторный ключ | 1984 |

|

SU1164874A1 |

| Дифференциальный усилитель | 1982 |

|

SU1084962A1 |

| Усилитель мощности | 1980 |

|

SU936378A1 |

| Формирователь импульсов управления | 1987 |

|

SU1522387A2 |

| Транзисторный ключ с защитой от перегрузки по току | 1981 |

|

SU980285A1 |

Авторы

Даты

1982-09-07—Публикация

1978-04-14—Подача