1

Изобретение относится к области вычислительной техники и может быть использовано при построении вычислительных систем с разветвленной сетью периферийных устройств.5

Известна система 1 ввода-вывода информации, содержащая устройство управления, входные и выходные устройства, элементы И и ИЛИ.

Недостатком этого устройства является ю низкая пропускная способность, обусловленная невозможностью передачи информации от одного абонента другому без участия процессора.

Наиболее близким к изобретению по 5 сущности технического рещения является мультиплексный канал 2, содержащий устройство управления, узлы связи (стыковки) с ОЗУ и процессором, регистры управляющего слова, текущего адреса дан- 2о ных, текущий счетчик данных, память подканалов, регистр кода операций и указателей. Обмен информацией в этом устройстве между периферийными устройствами и памятью процессора производится путем его 25 настройки, т. е. выдачи начальных адресов, объема массива и режимов обмена.

Недостатком этого канала является низкая пропускная способность из-за невозможности совмещения им двух режимов ЗО

обмена с одним периферийным устройством: невозможность на фоне обмена массивом информации провести обмен одним информационным словом. Для того, чтобы это осуществить, необходимо по команде из процессора остановить групповой обмен (т. е. обмен массивом информации), запомнить в памяти процессора состояние канала на момент останова, задать групповой обмен с объемом массива в одно слово (одиночный обмен), а после его выполнения организовать по команде из процессора продолжение группового обмена. Для организации передачи массива информации из одного периферийного устройства (А) в другое (Б) при помощи одного такого канала необходимо организовать два режима обмена: периферийное устройство А - память процессора и память процессора - периферийное устройство Б.

Кроме того, использование этого канала в троированных стр ктурах с многоуровневым восстановлением информации не представляется возможным, так как наличие одного отказа в канале резервирования приводит к отказу всей системы.

Целью изобретения является повыщение пропускной способности мультиплексного канала и снижение аппаратурных затрат.

Поставленная цель достигается тем, что в мультиплексный канал, содержащий узел управления, регистр текущего адреса данных, текущий счетчик данных, регистр управляющего слова, формирователь синхросигналов, узел приема и узел передачи информации, элемент И-ИЛИ и узел связи с процессором, информационный выход которого соединен с информационными входами текущего счетчика данных, регистра текущего адреса данных, узла унравления и регистра управляющего слова, выход которого соединен с первым информационным входом узла передачи информации, причем информационные выходы текущего счетчика данных и регистра текущего адреса данных соединены соответственно с первым и вторым информационными входами узла связи с процессором, первый выход узла управления соединен с первыми управляющими входами узлов приема и передачи информации и управляющими входами формирователя синхросигналов и узла связи с процессором, второй выход - со счетными входами текущего счетчика данных и регистра текущего адреса данных, нервый и второй управляющие входы - соответственно с управляющим выходом узла связи с процессором и выходом переполнения текущего счетчика данных, а группа выходов является группой выходов управляющих сигналов устройства, введены коммутатор адреса, регистр номера периферийного устройства и два регистра сдвига. Информационные входы регистров сдвига и регистра номера периферийного устройства соединены с информационным выходом узла связи с процессором. Информационные выходы регистров сдвига соединены соответственно с третьим и четвертым информационным входами узла связи с процессором. Выходы регистра номера периферийного устройства соединены с соответствующими адресиыми входами коммутатора адреса, выходы которого соединены с соответствующими адресными входами формирователя синхросигналов, узла передачи информации и узла приема информации, первый информационный выход которого соединен со вторыми информационными входами первого регистра сдвига и узла передачи информации, а второй информационный выход - с третьим информационным входом узла передачи информации и первым входом элемента И-ИЛИ, второй и третий входы которого подключены к первому выходу узла управления, а четвертый вход - к выходу соответствующего разряда первого регистра сдвига. Выход элемента И-ИЛИ соединен со входом соответствующего разряда первого регистра сдвига. Выходы последнего разряда первого и второго регистров сдвига соединены соответственно с четвертым и пятым информационными входами

узла передачи информации, второй ynjjaBляющий вход которого соединен с первым управляющим выходом формирователя синхросигналов, второй управляющий выход которого соединен с управляющими входами регистра управляющего слова, первого и второго регистров сдвига, а третий управляющий выход - со вторым управляющим входом узла приема информацин. Управляющнй вход коммутатора адреса соединен с первым выходом узла управления. Группа входов узла приема информации является группой информационных входов мультиплексного канала. Группы

выходов узла передачи информации,-формирователя синхроимпульсов и вторая группа выходов узла управления являются соответственно группами информационных, синхронизирующих и управляющих выходов

мультиплексного канала. Вход-выход узла связи с процессором является входом-выходом мультиплексного канала.

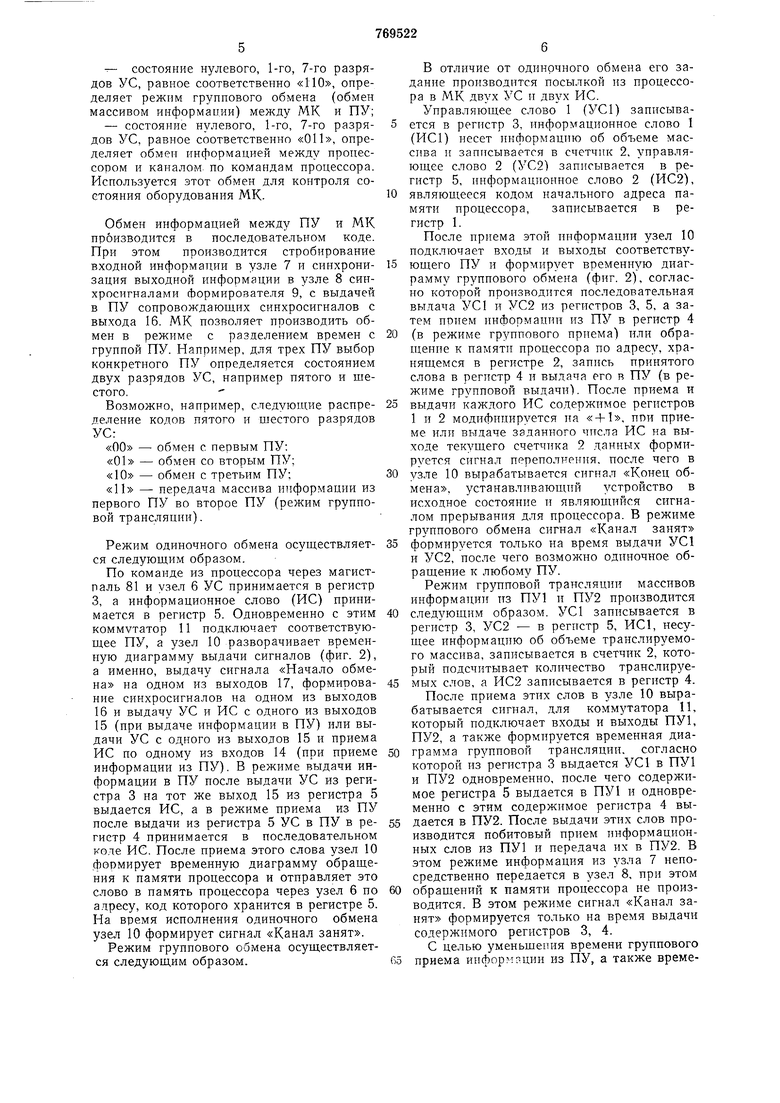

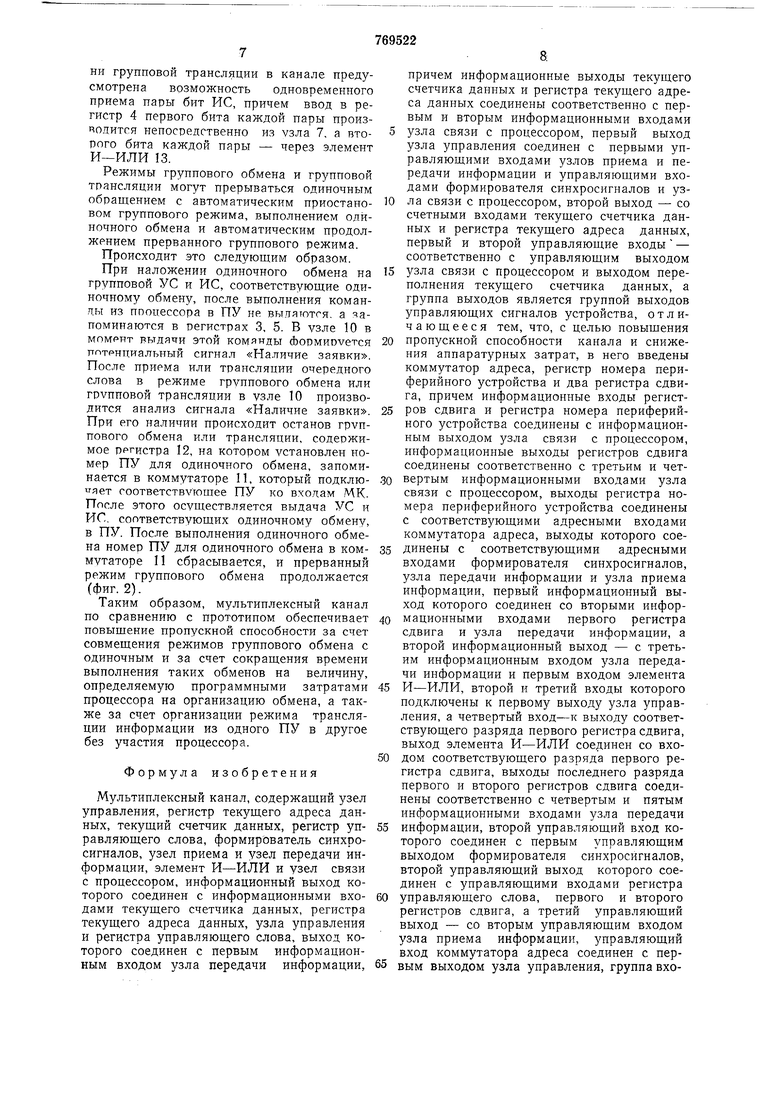

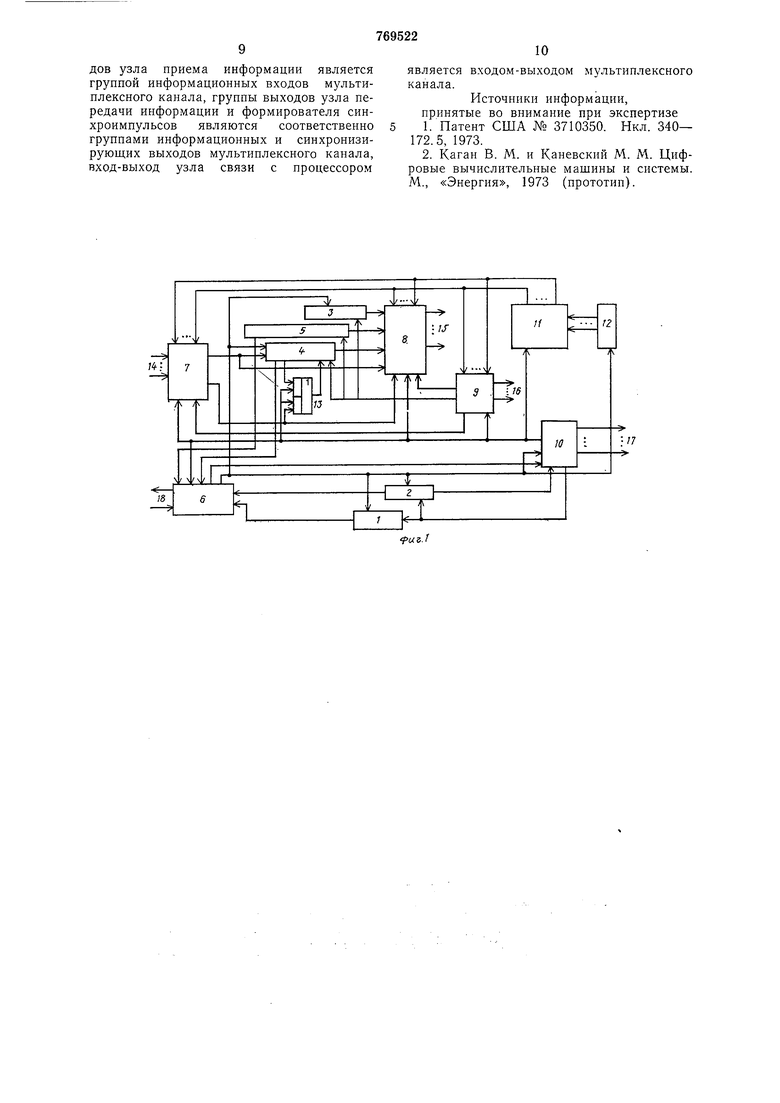

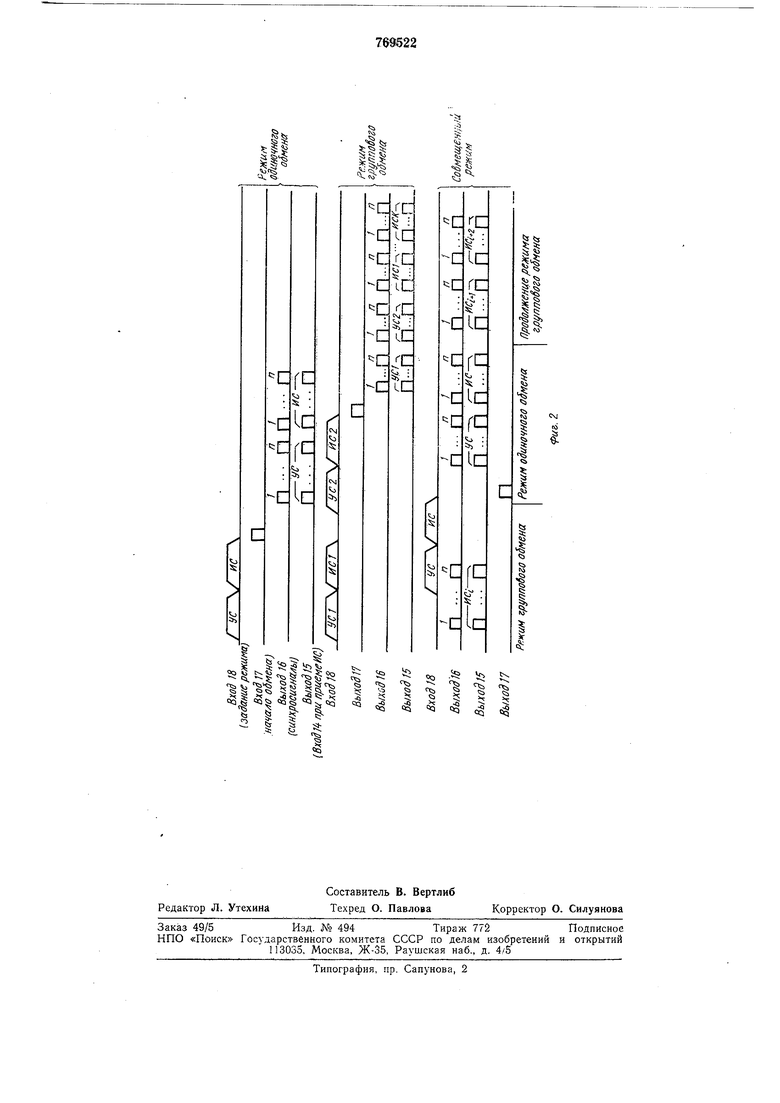

На фиг. 1 нредставлена структурная схема мультиплексного канала, на фиг. 2-

временная диаграмма его работы.

Устройство содержит регистр 1 текущего адреса данных, текущий счетчик 2 даннь1х, регистр 3 управляющего слова, регистры 4 и 5 сдвига, узел 6 связи с процессором,

узел 7 приема информации, узел 8 передачи информацни, формирователь 9 синхросигналов, узел 10 управлення, включающий например, регистры режима обмена и формирователи управляющих микрокоманд,

коммутатор 11 адреса, регистр 12 номера периферийного устройства, элемент И- ИЛИ 13, входы 14 иоследовательного кода, выходы 15 последовательного кода, выходы 16 синхросигналов, выходы 17 управляющих сигналов и вход - выход (магистраль) 18 обмена информацией с процессором.

Устройство работает следующим образом.

Обмен информацией между процессором (через мультиплексный канал) и периферийными устройствами (ПУ) разделяется на два вида:

-обмен между ПУ и мультиплексным каналом (МК) массивами информации (режим группового обмена) и одиночными словами (режим одиночного обмена);

-обмен между процессором и МК в режиме доступа к памяти процессора и по

командам из процессора.

Вид и режим задаются состоянием определенных разрядов управляющего слова (УС), например, 0-го, 1-го и 7-го, выдаваемого из процессора по магистрали 18. .Для

рассматриваемого случая принято следующее распределение кодов этих разрядов:

-состояние 0-го, 1-го, 7-го разрядов УС, равное соответственно «010, определяет режим одииочного обмена (обмен одним

словом) между МК и ПУ;

- состояние нулевого, 1-го, 7-го разрядов УС, равное соответстве шо «НО, определяет режим группового обмена (обмен массивом информации) между МК и ПУ;

- состояние нулевого, 1-го, 7-го разрядов УС, равное соответственно «011, определяет обмен информацией между процессором и каналом, по командам процессора. Используется этот обмен для контроля состояния оборудования МК.

Обмен информацией между ПУ и МК производится в последовательном коде. При этом производится стробирование входной информации в узле 7 и синхронизация выходной информации в узле 8 синхросигналами формирователя 9, с выдачей в ПУ сопровождающих синхросигналов с выхода 16. МК позволяет производить обмен в режиме с разделением времен с группой ПУ. Например, для трех ПУ выбор конкретного ПУ определяется состоянием двух разрядов УС, например пятого и шестого.

Возможно, например, следующие распределение кодов пятого и щестого разрядов УС:

«00 - обмен с первым ПУ;

«01 - обмен со вторым ПУ;

«10 - обмен с третьим ПУ;

«И - передача массива информации из первого ПУ во второе ПУ (режим групповой трансляции).

Режим одиночного обмена осуществляется следующим образом.

По команде из процессора через магистраль 81 и узел 6 УС принимается в регистр 3, а информационное слово (ИС) принимается в регистр 5. Одновременно с этим коммутатор 11 подключает соответствующее ПУ, а узел 10 разворачивает временную днаграмму выдачи сигналов (фиг. 2), а именно, выдачу сигнала «Начало обмена на одном из выходов 17, формирование синхросигналов на одном из выходов 16 и выдачу УС и ИС с одного из выходов 15 (при выдаче информации в ПУ) или выдачи УС с одного из выходов 15 и приема ИС но одному из входов 14 (при приеме информации из ПУ). В режиме выдачи информации в ПУ после выдачи УС из регистра 3 на тот же выход 15 из регистра 5 выдается ИС, а в режиме цриема из ПУ после выдачи из регистра 5 УС в ПУ в регистр 4 принимается в последовательном коле ИС. После приема этого слова узел 10 формирует временную диаграмму обращения к памяти процессора и отправляет это слово в намять процессора через узел 6 но адресу, код которого хранится в регистре 5. На время исполнения одиночного обмена узел 10 формирует сигнал «Канал занят.

Режим группового обмена осуществляется следующим образом.

В отличие от одиночного обмена его задание производится посылкой из процессора в МК двух УС и двух ИС.

Управляющее слово 1 (УС1) запнсыва5 ется в регистр 3, информационное слово 1 (ИС1) несет информацию об объеме массива и записывается в счетчик 2, управляющее слово 2 (УС2) записывается в регистр 5, информационное слово 2 (ИС2), являющееся кодом начального адреса памяти процессора, записывается в регистр 1.

После приема этой информации узел 10 подключает входы и выходы соответствующего ПУ и формирует временную диаграмму групнового обмена (фиг. 2), согласно которой производится последовательная выдача УС1 и УС2 из регистров 3, 5, а затем нонем информации из ПУ в регистр 4 (в режиме группового приема) или обращение к памяти процессора по адресу, хранящемся в регистре 2, запись принятого слова в регистр 4 и выдача его в ПУ (в режиме групповой выдачи). После приема и

5 выдачи каждого ИС содержимое регистров 1 и 2 модифицируется на « + 1, ПРИ приеме И.ЛИ выдаче заданного чттсла ИС на выходе текущего счетчнка 2 данных формируется сигнал переполнеггия. после чего в

0 узле 10 вырабатывается сигнал «Конец обмена, устанавливающий устройство в исходное состояние и являющийся сигналом прерывания для процессора. В режиме группового обмена сигнал «Канал занят

5 формируется только на время выдачи УС1 и УС2, после чего возможно одиночное обращение к любому ПУ.

Режим груцповой трансляции массивов информацнн из ПУ1 и ПУ2 производится

следующим образом. УС1 записывается в регистр 3, УС2 - в регистр 5, ИС1, несущее информацию об объеме транслируемого массива, записывается в счетчик 2, который подсчитывает количество транслируемых слов, а ИС2 записывается в регистр 4. После приема этих слов в узле 10 вырабатывается сигнал, для коммутатора 11, который цодключает входы и выходы ПУ1, ПУ2, а также формируется временная диаграмма групновой трансляции, согласно которой из регистра 3 выдается УС1 в ПУ1 и ПУ2 одновременно, после чего содержимое регистра 5 выдается в ПУ1 и одновременно с этим содержимое регистра 4 выдается в ПУ2. После выдачи этих слов производится побитовый прием информационных слов из ПУ1 и передача их в ПУ2. В этом режиме информация из узла 7 непосредственно передается в узел 8, при этом обращений к памяти процессора не производится. В этом режиме сигнал «Канал занят формируется только на время выдачи содержимого регистров 3, 4.

С целью уменьшения времени группового

5 приема информации из ПУ, а также времени групповой трансляции в канале предусмотрена возможность одновременного приема пары бит ИС, причем ввод в регистр 4 первого бита каждой пары производится непосредственно из узла 7, а второго бита каждой пары - через элемент И-ИЛИ 13.

Режимы группового обмена и групповой трансляции могут прерываться одиночным обращением с автоматическим нриостановом группового режима, выполнением одиночного обмена и автоматическим продолжением прерванного группового режима.

Происходит это следующим образом.

При наложении одиночного обмена на групповой УС и ИС, соответствующие одиночному обмену, после выполнения команды из пооцессора в ПУ не выдаются, а запоминаются в регистрах 3, 5. В узле 10 в момрнт выдачи этой команды сЬормиоуется пптрнниальный сигнал «На.яичие заявки. После приема или трансляции очередного слова в режиме группового обмена или ГРУППОВОЙ трансляции в узле 10 производится анализ сигнала «Наличие заявки. При его наличии происходит останов группового обмена или трансляции, содержимое регистра 12, на котором установлен номер ПУ для одиночного обмена, запоминается в коммутаторе И, который подклюиает соответствующее ПУ ко входам МК. После этого осуществляется выдача УС и ИС. соответствующих одиночному обмену, в ПУ. После выполнения одиночного обмена номер ПУ для одиночного обмена в коммутаторе И сбрасывается, и прерванный режим группового обмена продолжается (фиг. 2).

Таким образом, мультиплексный канал по сравнению с прототином обеспечивает повышение пропускной способности за счет совмещения режимов группового обмена с одиночным ц за счет сокращения времени выполнения таких обменов на величину, определяемую программными затратами процессора на организацию обмена, а также за счет организации режима трансляции информации из одного ПУ в другое без участия процессора. Формула изобретения

Мультиплексный канал, содержащий узел управления, регистр текущего адреса данных, текущий счетчик данных, регистр уцравляющего слова, формирователь синхросигналов, узел приема и узел передачи информации, элемент И-ИЛИ и узел связи с процессором, информационный выход которого соединен с информационными входами текущего счетчика данных, регистра текущего адреса данных, узла управления и регистра управляющего слова, выход которого соединен с первым информационным входом узла передачи информации,

причем информационные выходы текущего счетчика данных и регистра текущего адреса данных соединены соответственно с первым и вторым информационными входами узла связи с процессором, первый выход узла управления соединен с первыми управляющими входами узлов приема и передачи информации и управляющими входами формирователя синхросигналов и узла связи с процессором, второй выход - со счетными входами текущего счетчика данных и регистра текущего адреса данных, первый и второй управляющие входы - соответственно с управляющим выходом узла связи с процессором и выходом переполнения текущего счетчика данных, а группа выходов является группой выходов управляющих сигналов устройства, отличающееся тем, что, с целью повыщения пропускной способности канала и снижения аппаратурных затрат, в него введены коммутатор адреса, регистр номера периферийного устройства и два регистра сдвига, причем информационные входы регистров сдвига и регистра номера периферийного устройства соединены с информационным выходом узла связи с процессором, информационные выходы регистров сдвига соединены соответственно с третьим и четвертым информационными входами узла связи с процессором, выходы регистра номера периферийного устройства соединены с соответствующими адресными входами коммутатора адреса, выходы которого соединены с соответствующими адресными входами формирователя синхросигналов, узла передачи информации и узла приема информации, первый информационный выход которого соединен со вторыми информационными входами первого регистра сдвига и узла передачи информации, а второй информационный выход - с третьим информационным входом узла иередачи информации и первым входом элемента И-ИЛИ, второй и третий входы которого подключены к первому выходу узла управления, а четвертый вход-к выходу соответствующего разряда первого регистра сдвига, выход элемента И-ИЛИ соединен со входом соответствующего разряда первого регистра сдвига, выходы последнего разряда первого и второго регистров сдвига соединены соответственно с четвертым и пятым информационными входами узла передачи информации, второй управляющий вход которого соединен с первым управляющим выходом формирователя синхросигналов, второй управляющий выход которого соединен с управляющими входами регистра управляющего слова, первого и второго регистров сдвига, а третий управляющий выход - со вторым управляющим входом узла приема информации, управляющий вход коммутатора адреса соединен с первым выходом узла управления, группа входов узла приема информации является группой информационных входов мультиплексного канала, группы выходов узла передачи информации и формирователя синхроимпульсов являются соответственно группами информационных и синхронизирующих выходов мультиплексного канала, вход-выход узла связи с процессором

является входом-выходом мультиплексного канала.

Источники информации, принятые во внимание при экспертизе

1.Патент США № 3710350. Нкл. 340- 172.5, 1973.

2.Каган В. М. и Каневский М. М. Цифровые вычислительные машины и системы. М., «Энергия, 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Канал обмена многомашинного комплекса | 1984 |

|

SU1236492A1 |

| Мультиплексный канал | 1980 |

|

SU957199A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1305693A2 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1256036A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Устройство сопряжения двух ЭВМ | 1985 |

|

SU1334153A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Устройство для сопряжения | 1978 |

|

SU813400A2 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1987 |

|

SU1501077A1 |

Авторы

Даты

1980-10-07—Публикация

1978-10-04—Подача