(54) АНАЛОГО-ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СУММЫ ПАРНЫХ ПРОИЗВЕДЕНИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2002 |

|

RU2229157C2 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| Многоканальный аналого-цифровой процессор | 1983 |

|

SU1120375A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1317658A1 |

| Многоканальное устройство для ввода аналоговых данных | 1986 |

|

SU1335972A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| Устройство для вычисления полиномиальной функции от аналогового аргумента | 1990 |

|

SU1737444A1 |

| Функциональный преобразователь | 1977 |

|

SU744639A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1992 |

|

RU2042269C1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в различных специализированных устройствах моделирования систем уравнений, фильтрации сигналов, обработки информации и т. п. лця вычисления суммы парных произведений аналоговых величин Х , на коэффициенты aj с представлением результата в цифровом виде.

Известно устройство для вычисления суммы парных произведений, -содержащее регистры, блоки умножения, сумматоры и

блоки промежуточной памяти 1.

Недостатком этого устройства является невысокое бьгстродействие.

Известно также устройство для вычисления суммы парных произведений, содержащее коммутаторы, аналого-цифровой преобразователь, мультиплексор, компаратор, ключи, блок аналоговой памяти и блок управления 2./

Недостатками устройства яйляются пониженные точность и быстродействие.

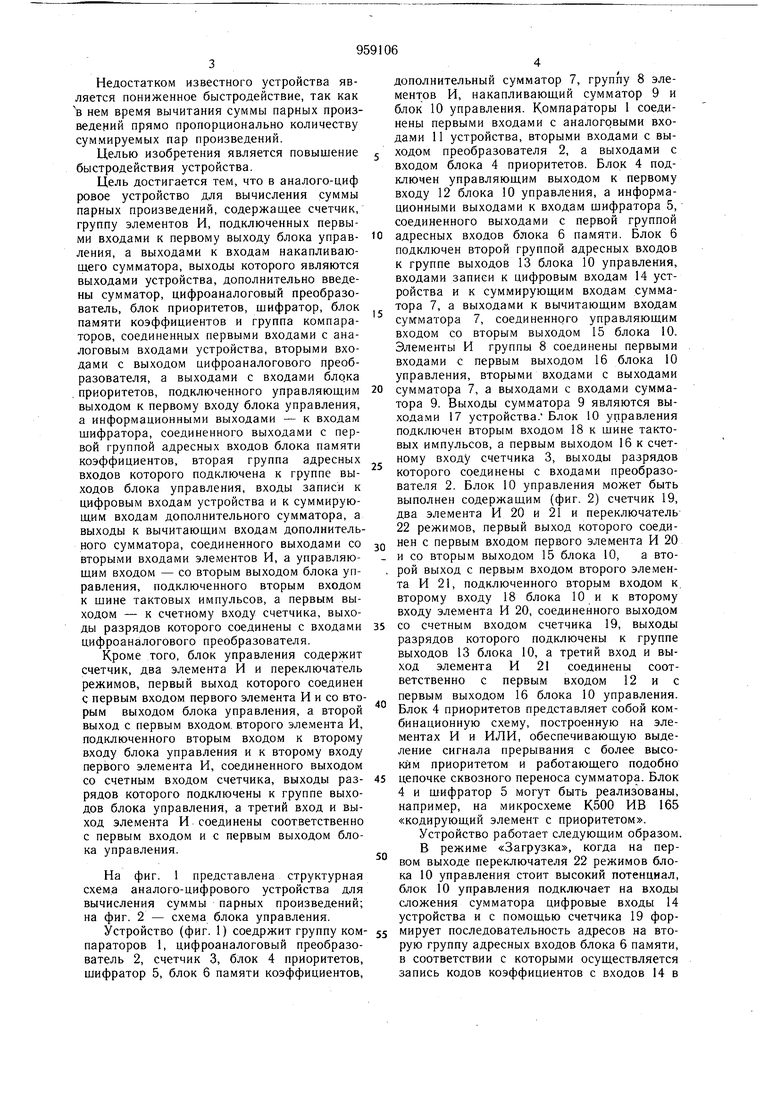

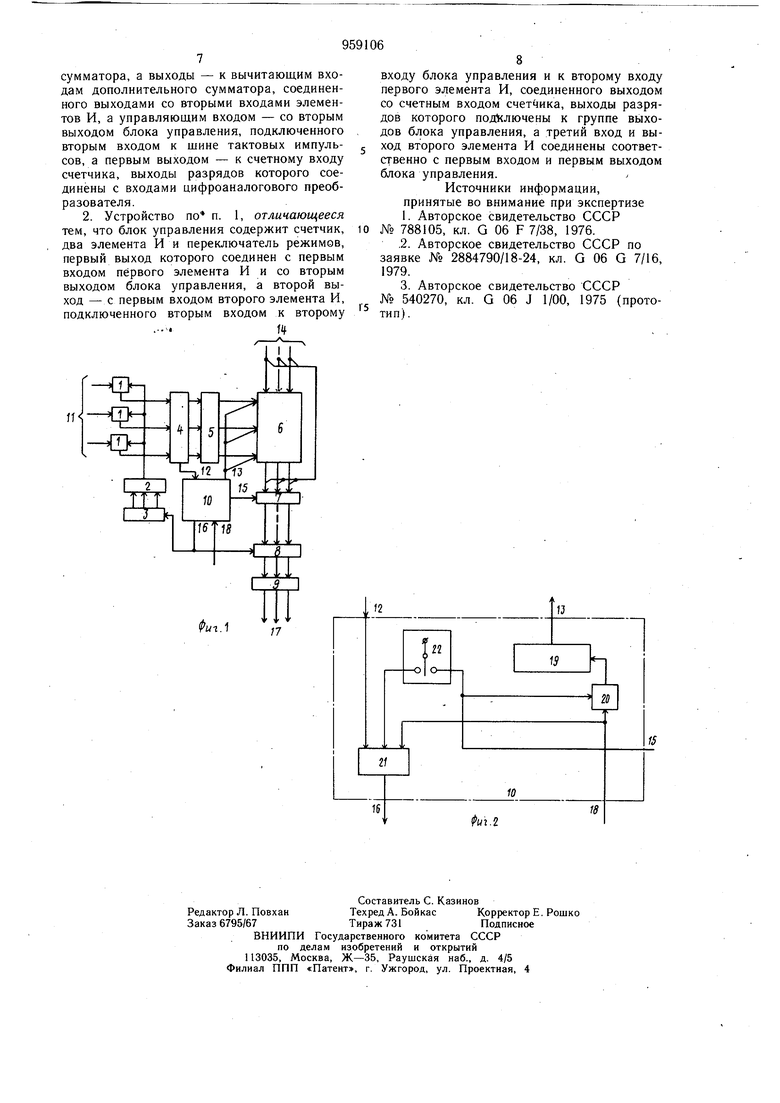

Наиболее близким к изобретению является аналого-цифровое устройство для вычисления суммы парных произведений, содержащее счетчик, группу элементов И, подключенных первыми входами к первому выходу блока управления, а выходами к входам накапливающего сумматора, выходы которого являются выходами устройства, а вторые входы элементов И группы соединены с выходами разрядов счетчика и с первыми входами элементов ИЛИ группы, подключенных вторыми входами к цифровым входам элементов И второй группы, соединенных выходами с установочными входами разрядов второго счетчика, подключенного выходом к первому входу триггера, а вычитающим входом - к выходу первого элемента И, соединенного первым входом с щиной тактовых импульсов, а вторым входом - с выходом триггера и с первым входом второго элемента И, подключенного выходом к счетному входу первого счетчика, а вторым входом - квыхюду преобразователя аналог-частота, соединенного входом через коммутатор с аналоговыми входами устройства, причем управляющий вход первого счетчика второй вход триггера и вторые входы элементов И второй группы подключены к соответствующим входам блока управления 3. Недостатком известного устройства является пониженное быстродействие, так как в нем время вычитания суммы парных произведений прямо пропорционально количеству суммируемых пар произведений. Целью изобретения является повышение быстродействия устройства. Цель достигается тем, что в аналого-циф ровое устройство для вычисления суммы парных произведений, содержащее счетчик, группу элементов И, подключенных первыми входами к первому выходу блока управления, а выходами к входам накапливающего сумматора, выходы которого являются выходами устройства, дополнительно введены сумматор, цифроаналоговый преобразователь, блок приоритетов, шифратор, блок памяти коэффициентов и группа компараторов, соединенных первыми входами с аналоговым входами устройства, вторыми входами с выходом цифроаналогового преобразователя, а выходами с входами блока . приоритетов, подключенного управляющим выходом к первому входу блока управления, а информационными выходами - к входам шифратора, соединенного выходами с первой группой адресных входов блока памяти коэффициентов, вторая группа адресных входов которого подключена к группе выходов блока управления, входы записи к цифровым входам устройства и к суммируюШ.ИМ входам дополнительного сумматора, а выходы к вычитающим входам дополнительного сумматора, соединенного выходами со вторыми входами элементов И, а управляющим входом - со вторым выходом блока управления, подключенного вторым входом к шине тактовых импульсов, а первым выходом - к счетному входу счетчика, выходы разрядов которого соединены с входами цифроаналогового преобразователя. Кроме того, блок управления содержит счетчик, два элемента И и переключатель режимов, первый выход которого соединен с первым входом первого элемента И и со вторым выходом блока управления, а второй выход с первым входом, второго элемента И, подключенного вторым входом к второму входу блока управления и к второму входу первого элемента И, соединенного выходом со счетным входом счетчика, выходы разрядов которого подключены к группе выходов блока управления, а третий вход и выход элемента И соединены соответственно с первым входом и с первым выходом блока управления. На фиг. 1 представлена структурная схема аналого-цифрового устройства для вычисления суммы парных произведений; на фиг. 2 - схема блока управления. Устройство (фиг. 1) соедржит группу компараторов 1, цифроаналоговый преобразователь 2, счетчик 3, блок 4 приоритетов, шифратор 5, блок 6 памяти коэффициентов. дополнительный сумматор 7, rpynfiy 8 элементов И, накапливающий сумматор 9 и блок 10 управления. Компараторы 1 соединены первыми входами с аналогрвыми входами 11 устройства, вторыми входами с выходом преобразователя 2, а выходами с входом блока 4 приоритетов. Блок 4 подключен управляющим выходом к первому входу 12 блока 10 управления, а информационными выходами к входам шифратора 5, соединенного выходами с первой группой адресных входов блока 6 памяти. Блок 6 подключен второй группой адресных входов к группе выходов 13 блока 10 управления, входами записи к цифровым входам 14 устройства и к суммирующим входам сумматора 7, а выходами к вычитающим входам сумматора 7, соединенного управляющим входом со вторым выходом 15 блока 10. Элементы И группы 8 соединены первыми входами с первым выходом 16 блока 10 управления, вторыми входами с выходами сумматора 7, а выходами с входами сумматора 9. Выходы сумматора 9 являются выходами 17 устройства. Блок 10 управления подключен вторым входом 18 к шине тактовых импульсов, а первым выходом 16 к счетному входу счетчика 3, выходы разрядов которого соединены с входами преобразователя 2. Блок 10 управления может быть выполнен содержащим (фиг. 2) счетчик 19, два элемента И 20 и 21 и переключатель 22 режимов, первый выход которого соединен с первым входом первого элемента И 20 и со вторым выходом 15 блока 10, а второй выход с первым входом второго элемента И 21, подключенного вторым входом к. второму входу 18 блока 10 и к второму входу элемента И 20, соединенного выходом со счетным входом счетчика 19, выходы разрядов которого подключены к группе выходов 13 блока 10, а третий вход и выход элемента И 21 соединены соответственно с первым входом 12 и с первым выходом 16 блока 10 управления. Блок 4 приоритетов представляет собой комбинационную схему, построенную на элементах И и ИЛИ, обеспечивающую выделение сигнала прерывания с более высоким приоритетом и работающего подобно цепочке сквозного переноса сумматора. Блок 4 и щифратор 5 могут быть реализованы, например, на микросхеме К500 ИВ 165 «кодирующий элемент с приоритетом. Устройство работает следующим образом. В режиме «Загрузка, когда на первом выходе переключателя 22 режимов блока 10 управления стоит высокий потенциал, блок 10 управления подключает на входы сложения сумматора цифровые входы 14 устройства и с помощью счетчика 19 формирует последовательность адресов на вторую группу адресных входов блока 6 памяти, в соответствии с которыми осуществляется запись кодов коэффициентов с входов 14 в блок 6 памяти. Сумматор 7 при этом производит суммирование кодов коэффицицентов. После передачи и записи всех коэффициентов, в сумматоре 7 будет накоплена сумма кодов всех коэффициентов. В режиме «Работа, когда на втором выходе переключателя 22 режимов стоит высокий потенциал, блок 10 управления по выходу 15 подключает на вычитающие входы сумматора 7 выходы блока 6 памяти и разрешает прохождение тактовых импульсов по выходу 16 на вход счетчика 3 и первые входы элементов И группы 8. Каждый тактовый импульс осуществляет передачу содержимого сумматора 7 через группу элементов И 8 в накапливающий сумматор 9. Счетчик 3 осуществляет подсчет количества тактовых импульсов с начала цикла, при этом содержимое его передается на вход цифроаналогового преобразователя . 2, на выходе которого получается ступенчатонарастающее напряжение. В момент сравнения ступенчато-нарастающего напряжения с аналоговыми величинами х-, , подключенными на первые входы компараторов 1, на выходах компараторов появляются сигналы, которые, пройдя, блок 4 приоритетов, шифруются шифратором 5 таким образом, что позиционный код на выходе блока 4приоритетов превращается в двоичный код номера компаратора. Двоичный код номера компаратора с выхода шифратора 5поступает на первую группу адресных входов блока 6 памяти, в соответствии с которым осуществляется считывание коэффициентов а, соответствующих номеру сработавшего компаратора. Считанные коэффициенты с выходов блока 6 памяти поступают на вычитающие входы сумматора 7, который осуществляет вычитание считанного коэффициента aj из общей суммы всех коэффициентов. Изменившееся в течение цикла содержимое сумматора 7 каждым тактовым импульсом передается в накапливающий сумматор 9. За период цикла развертки ступенчатонарастающего напряжения срабатывают все компараторы 1, каждый из которых осуществляет вычитание соответствующего ему коэффициента а из общей суммы коэффициентов. При этом получается, что каждый тактовый импульс, поступивщий на вход счетчика 3, умножается на код, равный сумме коэффициентов, соответствующих не сработавшим компараторам. В результате чего в накапливающем сумматоре 9 накапливается величина, равная сумме произведений... S. неодновременном срабатывании компараторов 1 блок 4 приоритетов практически не задерживает прохождение такто. вых импульсов на выход 16 блока 10 управления. Однако при одновременном срабатывании нескольких компараторов 1 блок 4 по управляющему выходу через блок 10 управления (элемент И 21 на фиг. 2) запрещает прохождение тактовых импульсов на вход счетчика 3 и первые входы элементов И группы 8. При этом блок 4 последовательно подключает сработавщие компараторы 1 на входы шифратора 5, который выдает на первую группу адресных входов блока 6 памяти номера сработавших компараторов, в соответствии с которыми считываются соответствующие им коэффициенты и вычитаются из общей суммы коэффициентов. После подключения к шифратору 5 всех одновременно сработавших компараторов 1 блок 4 приоритетов по управляемому выходу через блок 10 управления разрешает прохождение тактовых импульсов на вход счетчика 3 и элементы И группы 8 до следующего момента одновременного срабатывания компараторов 1 или до конца ступенчато-нарастающеи развертки. В отличие от прототипа, где для преобразования каждой аналоговой величины х; требуется один цикл развертки, в рассмотренном устройстве за один цикл развертки происходит срабатывание всех компараторов. При этом время вычисления iajXjHe зависит от количества пар сомножителей. Следовательно, выигрыш данного устройства по быстродействию по сравнению с прототипом составляет N паз и увеличивается с ростом числа пар сомножителей. Формула изобретения Аналого-цифровое устройство для вычисления суммы парных произведений, содержащее счетчик, группу элементов И, подключенных первыми входами к выходу блока управления, а выходами - к в.чодам накапливающего сумматора, выходы которого являются выходами устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него дополнительно введены сумматор, цифроаналоговый преобразователь, блок приоритетов, шифратор. блок памяти коэффициентов и группа компараторов, соединенных первыми входами с аналог;)Выми входами устройства, вторыми входами - с выходами цифроаналогового преобразователя, а выходами - с входами блока приоритетов, подключенного управляющими выходами к первому входу блока управления, а информаци онными выходами - к входам шифратора, соединенного выходами с первой группой адресных входов блока памяти коэффициентов, вторая группа адресных входов которого подключена к группе выходов блока управления, входы записи - к цифровым входам устройства и к суммирующим входам дополнительного

сумматора, а выходы - к вычитающим входам дополнительного сумматора, соединенного выходами со вторыми входами элементов И, а управляющим входом - со вторым выходом блока управления, подключенного вторым входом к щине тактовых импульсов, а первым выходом - к счетному входу счетчика, выходы разрядов которого соединены с входами цифроаналогового преобразователя.

fif

входу блока управления и к второму входу первого элемента И, соединенного выходом со счетным входом счетчика, выходы разрядов которого подключены к группе вь1ходов блока управления, а третий вход и выход второго элемента И соединены соответственно с первым входом и первым выходом блока управления.

Источники информации,

принятые во внимание при экспертизе

.2. Авторское свидетельство СССР по заявке № 2884790/18-24, кл. G 06 G 7/16, 1979.

Авторы

Даты

1982-09-15—Публикация

1980-11-28—Подача