(54) РЕГИСТР

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный регистр сдвига | 1990 |

|

SU1721632A1 |

| Устройство для вывода информации | 1990 |

|

SU1727127A1 |

| Ячейка памяти для сдвиговогоРЕгиСТРА | 1976 |

|

SU809382A1 |

| Устройство для разделения коррелограмм | 1987 |

|

SU1432558A1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1481859A1 |

| Устройство для вычисления матрицы направляющих косинусов | 1983 |

|

SU1233142A1 |

| Вычислительная ячейка | 1985 |

|

SU1287145A1 |

| Устройство для формирования гистограммы случайных чисел | 1986 |

|

SU1388901A1 |

| Устройство для динамического преобразования адресов | 1980 |

|

SU903878A1 |

| БОРТОВОЙ СПЕЦВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2522852C1 |

Изобретение относится к вычислительной технике и может быть использовано для согласования различных устройств ЭВМ и построения накопителей для промежуточного хранения информации.

Известен многофункциональный регистр с различным количеством разрядов j построенный на триггерах различных типов из интегральных элементов различной степени интеграции.

Однако количество выводов не соответствует стандарт;ным корпусам интегральных микросхем, что приводит к большому количеству, внешних соединений, снижающих помехоустойчивость при повышении скорости обработки информации t1.

Наиболее близким к предлагаемому по технической сущности является регистр на D-триггерах с параллель-но-последовательным приемом информации .2 . .

Однако при параллельном выводе информации из восьмиразрядного, регистра, построенного по этой схеме, требуется общее количество контактов, не соответствующее количеству контактов стандартных корпусов для интегральных микросхем, что препАтствует изготовлению его по интегральной технологии.

Целью изобретения является расширение области применения регистра за счет последовательного ввода и вывода информации и повыш.ение его надежности.

Поставленная цель достигается тем, что в регистр, содержащий ячейки па10мяти и шины управления, введены первая и вторая группы элементов НЕ, элемент И-НЕ и. элементы развязки, например диоды, анод каждого из которьрс является одним из входов - вы15ходов регистра и соединен с первым входом Каждой ячейки памяти, входы элементов НЕ первой группы соединены с шинами управления, выходы элементов НЕ первой группы соединены

20 с входами элементов НЕ второй группы, выходы первого и второго элементов НЕ первой группы элементов НЕ. соединены с входами элемента И-НЕ, выход которого соединен с вторым вхо25дом каждой ячейки памяти, выход каждого элемента НЕ, кроме,первого, предпоследнего и последнего, второй группы элементов НЕ соединен с третьим Входом каждой, кроме первой, ячейки

30 памяти, четвертый и пятый входы которой соединены соответственно с выходами и предпоследнего элементов НЕ второй группы элементов НЕ шестой вход каждой ячейки памяти соединен с выходом последнего элемента НЕ второй группы элементов НЕ, седь ой вход каждой ячейки памяти соединен с выходом предпоследнего элемента НЕ первой группы элементов НЕ., во съмой вход каждой ячейки.памяти соединен с первым выходом последующей ячейки памяти, первый выход каждой ячейки памяти соединен с одним из входов последующей ячейки памяти, второй выход каждой ячейки памяти соединен с анодом соответствующего диода, третий вход первой ячейки памяти соединен с выходом последнего элемента НЕ второй группы элементов НЕ.

Каждая ячейка памяти регистра, кроме первой и последней, содержит триггер, первый и второй элементы НЕ и восемь элементов И-НЕ, выход восьмого элемента И-НЕ является вторым выходом ячейки памяти, входы восьмого элемента И-НЕ соединены с выходами шестого и седьмого элементов И-НЕ первые .входы которых соединены с выходами триггера, вторые в ходаа шестого и седьмого элементов И-НЕ являются шестым входом ячейки памяти, третьи входы шестого и седьмого элементов И-НЕ являются соответственно пятым и шестым входами ячейки памяти, первый выход триггера является .первым.выходом ячейки памяти, первый вход триггера является вторым входом ячейки памяти, второй вход триггера соединен с выходом пятого элемента И-НЕ, входы которого соединены с выходами первого второго, третьего и четвертого элементов И-НЕ, первые входы первого и второго элементов И-НЕ являются третьим входом ячейки памяти, вторые входы первого и второго элементов И-НЕ соединены Соответственно с выходами первого и второго элементов НЕ, третий вход первого элемента И-НЕ и первый вход четвертого элемента И-НЕ являются .пятым входом .ячейки памяти, третий вход второго элемента И-НЕ и первый вход четвертого элемента И-НЕ являются седьмым входом ячейки памяти, вторые входы третьего и четвёртого элементов И-НЕ являются четвертым входом ячейки памяти, третий вход четвертого элемента И-НЕ является восьмым входом ячейки памяти, третий вход третьего элемента И-НЕ соединен с первьм выходом триггера, вход второго элемента НЕ соединен с выходом первого элемента НЕ, вход которого явля ется первым входом ячейки памяти.

Первая и последняя ячейки памяти содержат девятые элементы И-НЕ,выхо

ы которых соединены соответс венно с третьими входами восьмых элементов И-НЕ, первые входы девятых элементов И-НЕ соединены соответственно с первыми входа:ми триггеров, вторые и третьи входы девятых элементов И-НЕ являются седьмым и пятым входами первой и последней ячеек памяти, третьи входы девятых элементов И-НЕ первой и последней ячеек памяти являются первыми входами ука4 занных ячеек.

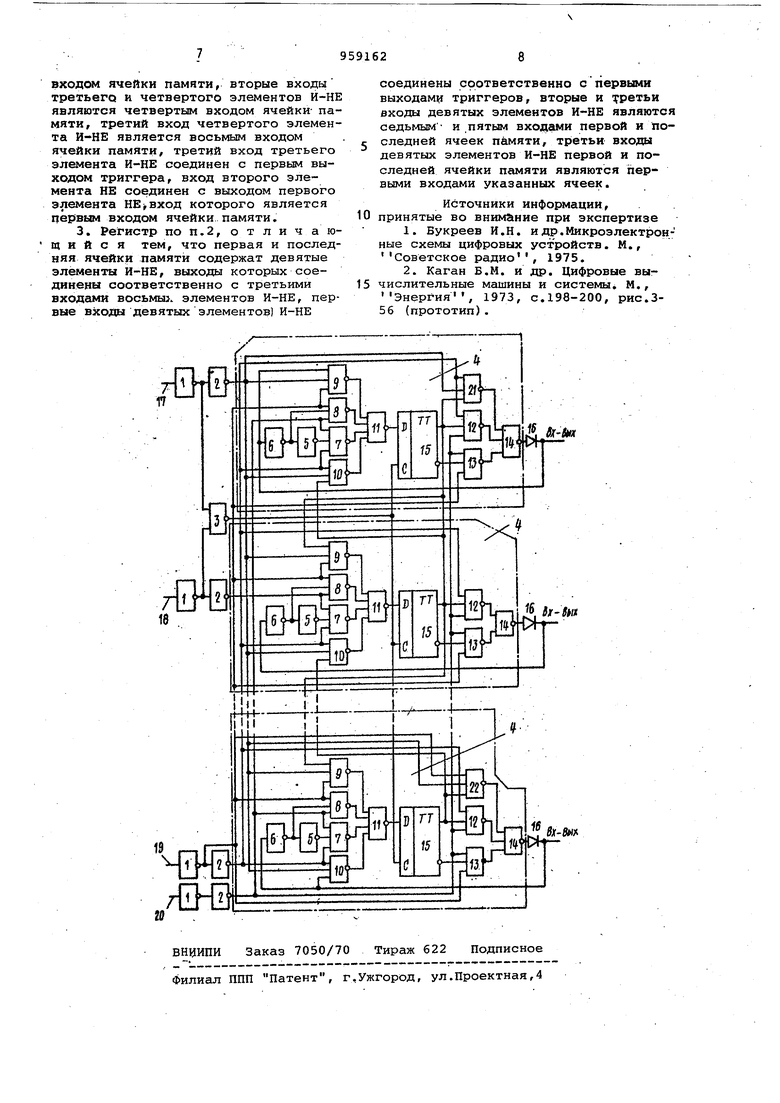

На чертеже изображена функциональная схема предложенного устройства..

Устройство содержит элементы НЕ 1 и 2 первой и второй групп, основной элемент И-НЕ 3, ячейки 4 памяти, каждая из которых состоит из элементов НЕ 5 и б, элементов И-НЕ 7-14, триггера 15. Кроме того, регистр содержит элементы 16 развязки, шины 17-20 управления, элементы И-НЕ 21 и 22 первой и цоследней ячеек 4 памяти.

Регистр функционирует следующим образом.

При приеме информации .параллельным кодом она поступает на входвыход регистра и через элементы 16 развязки или на элементы 5, 6 и 7 и Шину 17 управления или элементы 5, 8 и 11 в соответствии со значением сигнала Реверс и далее на D-входы триггеров 15. При выдаче информации параллельным кодом содержимое триггеров 15 поступает с прят мых выходов через элементы И-НЕ 12 и 14 или с инверсных выходов через элементы И-НЕ 13 и 14 в соответствии со значением сигнала Реверс через элементы разрядки на выходы регистра. При сдвиге вправо содержи} 1ое триггеров. 15 старших разрядов через элементы И-НЕ 10 и 11 при наличии сигнала Сдвиг в единичном значении сигнала Реверс передается на С-входы соседних триггеров 15 младших разрядов. При этом на . вход триггера 15 самого старшего разряда поступает информация с соответствующего входа - выхода, а с прямого выхода триггера 15 младшего разряда через элементы И-НЕ 21 и 14 и элемент развязки 16 сол ержимое поступает на выход младшего разряда. При внешнем соединении выходов младшего и ста ршего разрядов происходит кольцевой сдвиг содержимого регистра вправо. При изменении значения сигнала Реверс- на нулевой сдвиг происходит в обратном направлении через элементы И-НЕ 9 и 22, а элементы И-НЕ 10 и 21 закрыты. Прием и выдача информации последовательным кодом, йачиная со старших или начиная с младших разрядов, в соответствии со значением сигнала Реверс , без инверсии осуществляется по сигналам Сдвиг Количествр сигналов Сдвиг должно равняться количеству разрядов кода. Как при приеме информации, так и при сдвиге на входы с триггеров 15 поступает управляющий сигнал с элемента И-НЕ 3, передающего сигналы Прием или/Сдвиг.

Импульсные сигналы Прием, Сдвиг и Выдача должны поступать в различные моменты времени Одновременное поступление хотя бы двух из них в любой комбинации на один и тот же регистр недопустимо. Значение сигнала Реверс определяется направлением сдвига и необходимостью инверсии.

Применение предложенного устройства для согласования различных устройств ЭВМ и построения накопителей позволяет унифицировать связи устройства и управление ими. Универсальные регистры можно с успехом применять как в ЭВМ параллельнсзвб действия, так и в ЭВМ последовательного действи-я.

Обработка технологического процесса изготовления регистра с учетс применения его s качестве унифицированного узла позволяет не только повысить надежность ЭВМ, но и снизить стоимость изготовления и эксплуатации ЭВМ.

Выполняемые регистром функции, возможности закольцовки, последовательного соединения регистров, подключения нескольких регистров к- общим разрядным шинам, количество разрядов регистра и возможность изготовления его в стандартном четырнадцатиконтактном корпусе являются основанием для применения универсалного регистра в качестве унифицированного узла современных ЭВМ.

Формула изобретения

-1. Регистр, содержащий ячейки памяти и шины управления, отличающийся тем, что, с целью расширения области применения регистра за счет последовательного ввода и вывода информации и повышения его нёщежности, в него введены первая и вторая группы элементов НЕ, элемент И-НЕ и элементы развязки, например диоды, анод каждого из которйх является одним из входов выходов регистра и соединен с первым входом каждой ячейки памяти, входы элементов НЕ первой группы соединены с шинами управления, выходы элементов НЕ первой группы соединены с входами элементов НЕ второй группы, выходы первого и второго элементов НЕ первой группы элементов НЕ. соединены с входами элемента И-НЕ, выход которого соединен с вторым входом каждой ячейки памяти, выход

каждого элемента НЕ, кроме первого, предпоследнего и последнего, второй группы элементов НЕ соединен с третьим входом каждой, кроме первой, ячейки памяти, четвертый и

пятый входы которой соединены соот- ветственно с выходами первого и предпоследнего элементов НЕ второй группы элементов НЕ, шестой вход каждой ячейки памяти соединен с выходом последнего элемента НЕ второй группы элементов НЕ, седьмой вход каждой ячейки памяти соединен с выходом предпоследнего элемента НЕ первой группы элементов НЕ, восьмой

вход каждой ячейки соединен с первым выходом последующей ячейки памяти, первый выход каждой ячейки памяти соединен с одним из входов последующей ячейки памяти, второй

выход каждой ячейки памяти соединен с анодом соответствующего диода, третий вход первой ячейки памяти соединен с выходом последнего эле мента НЕ второй группы элементов НЕ.

.2. Регистр по п.1,отличающ и и с я Тем, что в нем каждая ячейка памяти, кроме первой и 0оследней, содержит триггер, первый и второй элементы НЕ, восемь элементов И-НЕ, выход восьмого элемента И-тНЕ является вторым выходом ячейки памяти, входы восьмого элемента И-НЕ соединены с выходами шестого и седьмого элементов И-НЕ, первые

входы которых соединены с выходами триггера, вторые входы шестого и седьмого элементов И-НЕ являются шестым входом ячейки памяти, третьи входы шестого и седьмого элементов И-НЕ являются соответственно пятым и шестым входами ячейки памяти, первый выход триггера является первым выходом ячейки памяти, первый вход триггера является вторым входом ячейки памяти, второй вход триггера соединен с .выходом пятого элемента И-НЕ, входы которого соединены с выходами .первого, второго, третьего и четвертого элементов И-НЕ, первые входы первого

и второго элементов И-НЕ являются третьим входом ячейки памяти, вторые входал первого и второго элементов И-НЕ соединены соответственно с выходами первого и второго злеменхов НЕ, третий вход первого элемента И-НЕ и первый вход четвертого элемента И-НЕ являются пятым входом ячейки памяти, третий вход второго , элемента И-НЕ и первый вход четверjEpro элемента И-НЕ являются седьмым

Авторы

Даты

1982-09-15—Публикация

1980-06-18—Подача