(54) ЯЧЕЙКА ПАМЯТИ ДЛЯ СДВИГОВОГО РЕГИСТРА

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти для регистра сдвига | 1979 |

|

SU858106A1 |

| Устройство для обнаружения отказов в шаговом электроприводе | 1989 |

|

SU1640811A1 |

| Реверсивный регистр сдвига | 1990 |

|

SU1721632A1 |

| Регистр | 1981 |

|

SU1024989A1 |

| Ячейка памяти для регистра сдвига | 1979 |

|

SU851495A1 |

| Устройство для сопряжения между абонентами | 1987 |

|

SU1411759A1 |

| Вычислительный узел цифровой сетки | 1983 |

|

SU1132295A2 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Коррелометр | 1980 |

|

SU1062717A1 |

| Трехканальное резервированное запоминающее устройство | 1984 |

|

SU1215133A1 |

Изобретение относится к построению структур вычислительной техники и дискретной автоматики на логических элементах, преимущественно в интеграль ном исполнении. Известен регистр сдвига, ячейка пам ти которого содержит два триггера, выполненные на элементах И-ИЛИ-НЕ, и элементы И 1. Однако наличие значительного колкчества элементов- усложняет структуру ячейки памяти, что в конечном счете, при проектировании регистров сдвига пр водит к увеличению мощности генерато ра тактовых импульсов. Наиболее близким к предлагаемому является регистр сдвига, ячейка памят которого содержит два RS -триггера, одни из которых триггер памяти, другой коммутационный триггер. В каждом три гере выход элемента И-ИЛИ-НЕ соединен с одним из входов всех элементов И 12 Разряд этого реверсивного регистра является самым эксмомичным с точки зрения количества элементов И-ИЛИ-НЕ при максимально достижимом быстродействии. Недостатком известного регистра является повышенная нагрузка на генератор тактовых импульсов, так как вход тактовых импульсов регистра в каждой ячейке нагружен на шесть входов логических элементов. Поэтому при проектировании многоразрядных реверсивных регистров сдвига приходится на 5О% увеличивать необходимую мощность генератора тактовых импульсов. Цель изобретения - повышение надежности ячейки памяти за счет снижения коэффициента разветвления тактов Л шины. Поставленная цель достигается тем, что в ячейку памяти для сдвигового регистра, содержащую триггер памяти, выполненный на первом, втором элементах И и первом и втором элементах ИЛИ-HEj

коммугацнонный триггер, выполненный на третьем, четвертом, пятом и шестом элементах И и третьем и четвертом элементах , причем первые входы первого и второго элементов И триггера памяти соединены с выходами элементов ИЛИНЕ и первыми входами элементов И коммутационного триггера соответственно,

вторые входы первого и второго элементов И триггера памяти и третьего и четвертого элементов И коммутационного триггера соединены с тактовой шиной, вторые входы пятого и шестого элементов И коммутационного триггера соединены со входами ячейки памяти, выходы элементов ИЛИ-НЕ триггера памяти соединены с первыми выходами ячейки памяти и шины сдвига, введены в коммутационный триггер седьмой и восьмой элементы И, первые входы которых подключены к первым входам пятого и шестого элементов И коммутационного триггера, вторые входы - к первой шине сдвига, третьи входы - ко вторым выходам;ячейки памяти, а третьи входы пятого и шестого элементов И коммутационного триггера соединены со второй шиной сдвига.

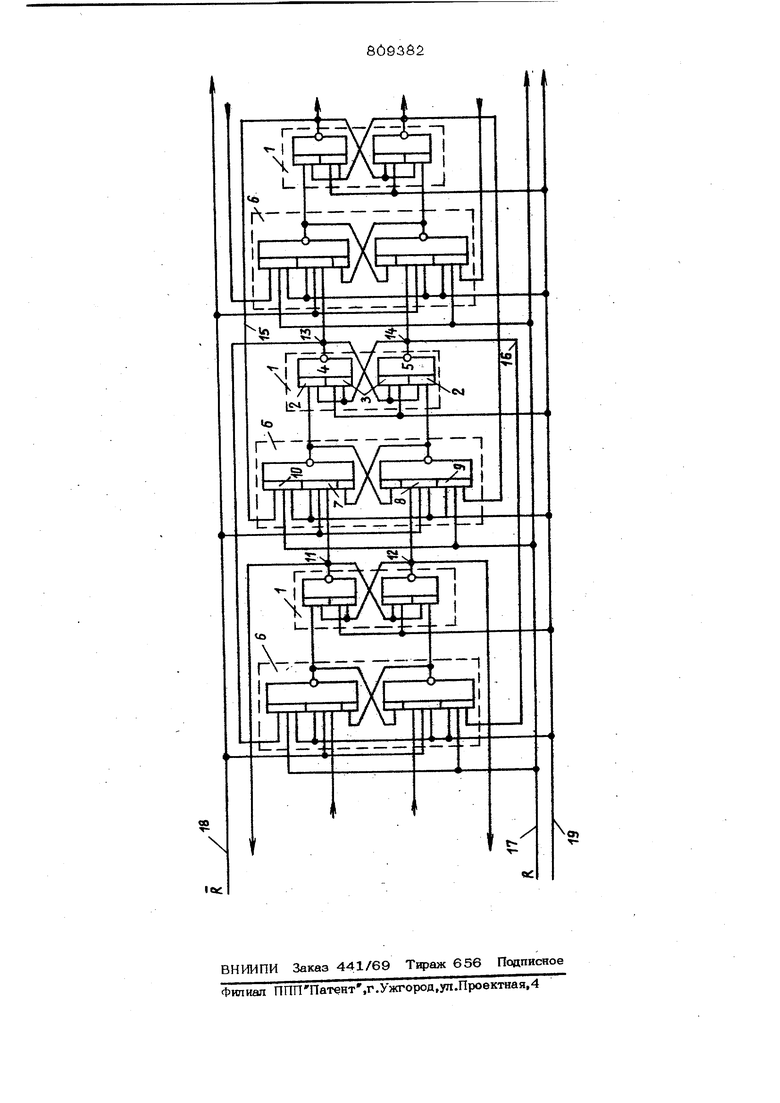

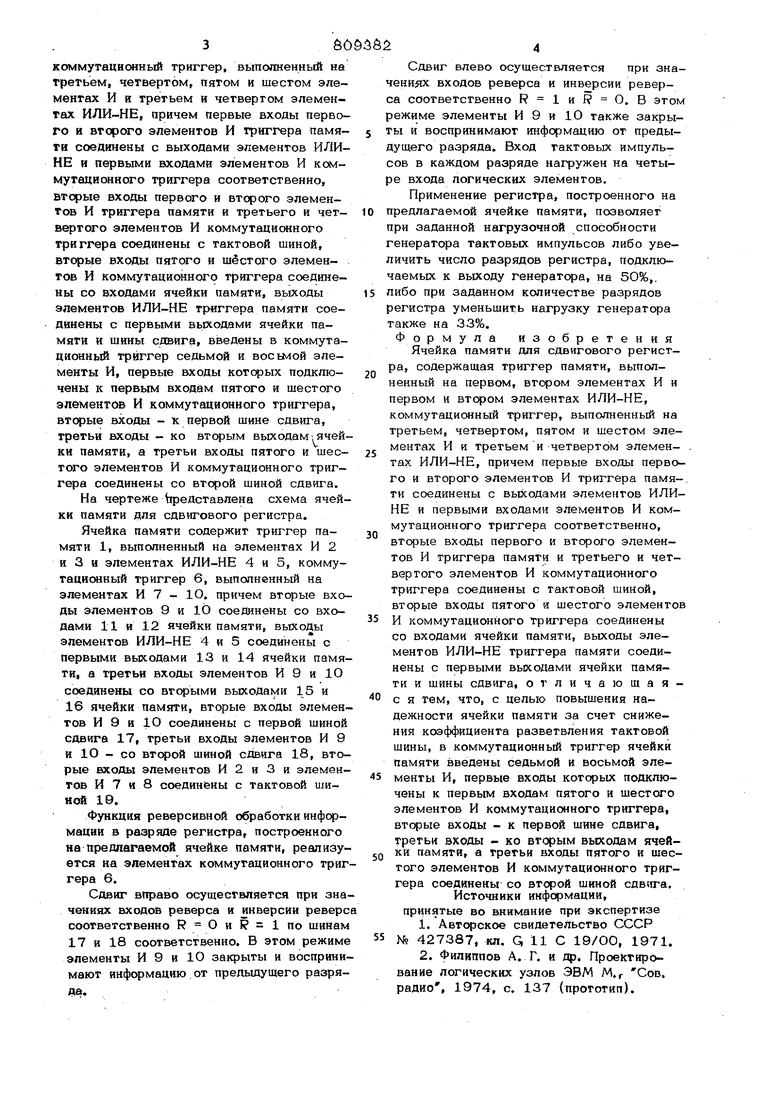

На чертеже представлена схема ячейки памяти для сдвигового регистра.

Ячейка памяти содержит триггер памяти 1, выполненный на элементах И 2 и 3 и элементах ИЛИ-НЕ 4 и 5, коммутационный триггер 6, выполненный на элементах И 7 - Ю. причем вторые входы элементов 9 и 1О соединены со входами 11 и 12 ячейки памяти, выходы элементов ИЛИ-НЕ 4 и 5 соединены с первыми выходами 13 и 14 ячейки памяти, а третьи входы элементов И 9 и 1О соединены со вторыми выходами 15 и

16ячейки памяти, вторые входы элементов И 9 и 1О соединены с первой шиной сдвига 17, третьи входы элементов И 9 и Ю - со второй шиной сдвига 18, вторые входы элементов И 2 и 3 и элементов И 7 и 8 соединены с тактовой шиной 19.

Функция реверсивной обработки инффмации в разряде регистра, построенного на предлагаемой ячейке памяти, реализуется на элементах коммутационного триггера 6.

Сдвиг BtipaBo осуществляется при значениях входов реверса и инверсии реверс соответственно Р шинам

17и 18 соответственно. В этом режиме элементы И 9 и Ю закрыты и воспринимают информацию от предьшущего разряда.

Сдвиг влево осушествляегся при значениях входов реверса и инверсии реверса соответственно К 1иК 0. В этом режиме элементы И 9 и 1О также закрыты и воспринимают информацию от предыдущего разряда. Вход тактовьк импульсов в каждом разряде нагружен на четыре входа логических элементов.

Применение регистра, построенного на предлагаемой ячейке памяти, позволяет при заданной нагрузочной способности генератора тактовых импульсов либо увеличить число разрядов регистра, подключаемых к выходу генератсра, на 5О%,. либо при заданном количестве разрядов регистра уменьшить нагрузку генератора также на 33%. Формула изобретения

Ячейка памяти для сдвигового регистра, содержащая триггер памяти, выполненный на первом, втором элементах И и первом и втором элементах ИЛИ-НЕ, коммутационный триггер, выполненный на третьем, четвертом, пятом и шестом элементах И и третьем и четвертом элемен- , тах ИЛИ-НЕ, причем первые входы первого и второго элементов И триггера памя-, ти соединены с выходами элементов ИЛИНЕ и первыми входами элементов И коммутационного триггера соответственно, вторые входы первого и второго элементов И триггера памяти и третьего и четвертого элементов И коммутационного триггера соединены с тактовой шиной, вторые входы пятого и шестого элементов И коммутационного триггера соединены со входами ячейки памяти, выходы элементов ИЛИ-НЕ триггера памяти соединены с первыми выходами ячейки памяти и шины сдвига, отличаюшаяс я тем, что, с целью повышения надежности ячейки памяти за счет снижения коэффициента разветвления тактовой шины, в коммутационный триггер ячейки памяти введены седьмой и восьмой элементы И, первые входы которых подключены к первым входам пятого и шестого элементов И коммутационного триггера, вторые входы - к первой шине сдвига,

третьи входы - ко вторым выходам ячейки памяти, а третьи входы пятого и шестого элементов И коммутационного триггера соединены со второй шиной сдвига,

Источники информации, принятые во внимание при экспертизе

55 № 427387, кл. QUO 19/ОО, 1971.

let

Авторы

Даты

1981-02-28—Публикация

1976-03-26—Подача