(54) УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1980 |

|

SU896621A1 |

| Микропрограммное устройство управления | 1981 |

|

SU962943A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1092505A1 |

| Устройство микропрограммного управления | 1980 |

|

SU896622A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Устройство микропрограммного управления | 1982 |

|

SU1086431A1 |

| Микропрограммное устройствоупРАВлЕНия | 1979 |

|

SU830386A1 |

| Микропрограммное устройство управления | 1980 |

|

SU943728A1 |

| Микропрограммный процессор | 1980 |

|

SU980098A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

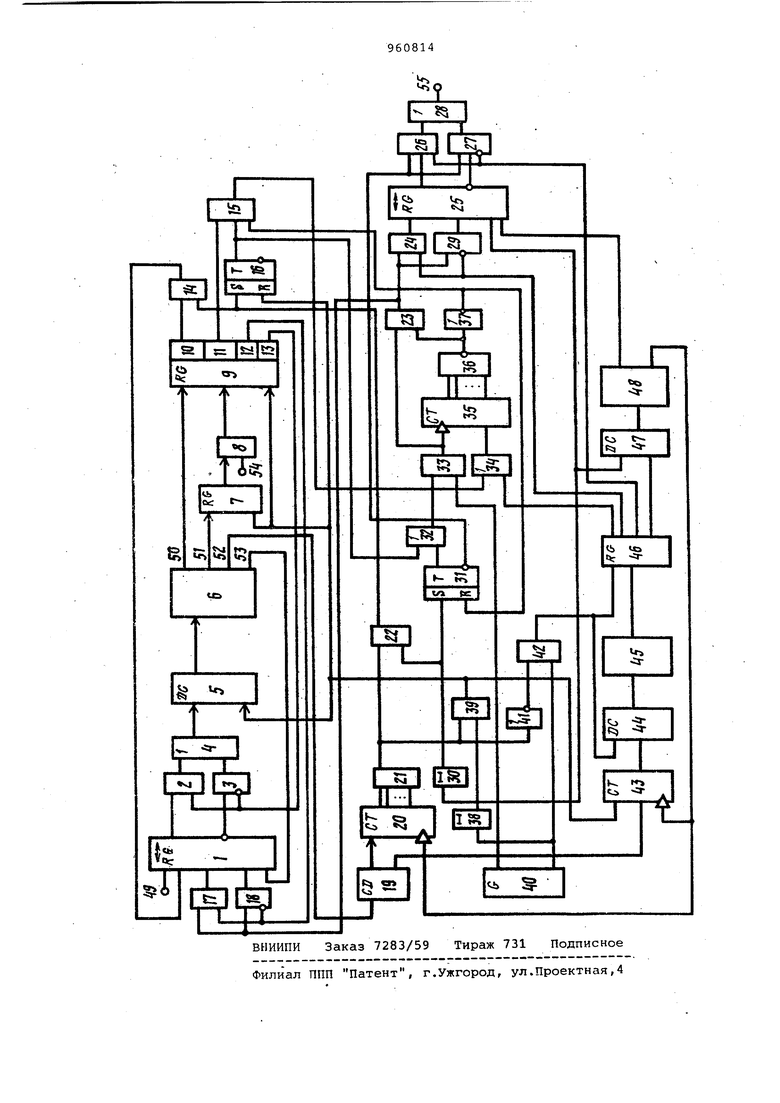

Изобретение относится к цифровой вычислительной технике и может йлть использовано в качестве устройства управления ЭВМ с мик13рпрограи«1мным принципом управления. Известно устройство микропрограммного управления, содержащее запоминающие блоки для хранения адресных и операционных микрокоманд, буферный регистр, регистр адреса и регистр логических условий, счетчики количес тва микрокоманд и адресов микрокоманд, шифратор, дешифраторы, триггер управления, лбгические элементы И, И-НЕ, НЕ, элементы задержки и генератор тактовых импульсов 1. Недостатком указанных устройств является низкая экономичность, обусловленная бо.г1ьшой избыточностью запоминающих блоков. Наиболее близким к изобретению по технической сущности является устрой ство микропрограммного управления, содержащее последовательно соединенные первый дешифратор, первый запоми нающий блок, буферный регистр, второ вход которого соединен с выходом пер вого блока элементов И, а первый выход через второй бУюк элементов И соединен с первым входом регистра сдвига базовой адресной микрокоманды, второй вход которого является входом кода операции устройства, вход логических условий которого соединен с первым входом первого блока элементов И, второй вход которого соединен с выходом регистра логических условий, первый вход которого соединен с вторым выходом первого запоминающего блока, третий выход KOTopoio через шифратор соединен с первым входом счетчика количества микрокоманд, второй выход шифратора соединен с первым входом счетчика адреса микрокоманд, выход которого через второй деишфратор, второй запоминающий блок, регистр адреса базовых операционных микрокоманд, третий дешифратор и третий запоминающий блок соединен со счетными входами счетчика адреса микрокоманд и счетчика количества микрокоманд, вцходы которого через первый элемент И соединены с первыми входами второго ,. третьего, а через первый элемент НЕ - четвертого элемента И, выход которого соединен с вторым входом дешифратора и входом установки в нуль регистра адреса.базовой операционной микрокоманды, а BTopok вход четвертого элемента И соединен с первым выходом генератора тактовых импульсов, а через первый элемент задержки - с входом установки в нул регистра сдвига базовых операционных микрокоманд, вторыми входами третьего дешифратора и. третьего эле мента И и входом второго элемента Эсщержки, выход которого соединен с единичным выходом первого триггера управления и вторым входом первого элемента И, выход которого соединен с вторым вХЬдом второго блока элементов И, выход третьего элемента Я соединен с входами установки в нуль буферного регистра, регистра логических условий, счетчика адреса микрокоманд и вторым входом первого дешифратора, нулевой выход первого триггера управления соединен с первым входом третьего блока элементов и, второй вход которого соединен с выходом регистра сдвига базовых опе рационных микрокоманд, первый вход которого соединен с вторым выходом третьего запоминающего блока, второй выход генератора тактовых импул сов соединен с вторым входом пятого элемента И, выход которого соединен с первым входом шестого .элемента И со счетным в ходом счетчика импульсов количества сдвига, выходы которого через элемент И-НЕсоединены с вторым входом шестого элемента И, а через второй элемент НЕ - с нулевым входом первого триггеру управления, четвертый выход первого запоминающего блока соединен с третьим входом регистра сдвига базовых адресных микрокоманд С 2. К недостатку устройства относитс большое время формирования операционных микрокоманд путем циклическог сдвига базовых операционных микрокоманд в одном направлении. Выполнение операции циклического сдвига базовой операционной микрокоманды в одном направлении приводит к увеличению времени формирования операционных микрокоманд, а сле довательно определяет повышенные требования к работе генератора тактовых импульсов. Целью изобретения является повышениё быстродействия. Поставленная цель достигается тем чтоВ устройство микропрограммн го : правления с базовыми множествами-микрокоманд, содержащее последовательно соединенные первый дешиф ратор, первый запоминающий блок, бу ферный регистр, второй вход которог соединен с выходом первого блока эл ментов И, а первый выход через второй блок элементов И соединен с пер вым входом регистра сдвига базовой адресной микрокоманды, второй вход кЬторого является входом кода опера ции устройства, вход логических усл ВИЙ которого соединен с первым входом первого блока элементов И, второй вход которого соединен с выходом регистра логических условий, первый вход которого соединен с вторым выходом первого запоминающего блока, третий выход которого через шифратор соединен с первым входом счетчика количества микрокоманд, второй выход шифратора соединен с первым входом счетчика адреса микрокоманд, выход которого через второй дешифратор, второй запоминающий регистр адреса базовых операционных микрокоманд, третий дешифратор и третий запоминающий блок соединен со счетными выходами счетчика адреса микрокоманд и счетчика количества тяикрокоманд, выходы которого через первый элемент И соединены с первыми входами второго, третьего, а через первый элемент НЕ - четвертого элемента И, выход которого соединен с вторым входом дешифратора и входом установки в нуль регистра адреса базовой операционной микрокоманды, а второй вход четвертого элемента И соединен с первым выходом генератора тактовых импульсов, а через первый элемент задержки - с входом установки в нуль регистра сдвига базовых операционных микрокоманд,вторыми входами третьего дешифратора и третьего элемента И и входом второго элемента задержки выход которого соединен с единичным выходом первого триггера управления и вторым входом первого элемента И, выход которого соединен с вторым входом второго блока элементов И, выход третьего элемента И соединен с входами установки в нуль буферного регистра,регистра логических условий, счетчика адреса микрокоманд и вторым входом первого дешифратора, нулевой выход первого триггера управления соединен с первым входом третьего блока элементов И, второй вход которого соеднинен с выходом регистра сдвига базовых операционных микрокоманд, первый вход которого соединен с вторым выходом третьего запоминающего блока, второй выход генератора тактовых импульсов соединен с вторым входом пятого элемента И, выход которого соедийен с первым входом шестого элемента И и со счетным входом счетчика импульсов количества сдвига, выходы которого через элемент И-НЕ соединены с вторым входом шестого элемента И, а через второй элемент НЕ - с нулевым входом перв.ого триггера управления, четвертый выход первого запоминающего блока соединен с третьимвыходом регистра сдвига базовых адресных микрокоманд, дополнительно введены три блока элементов ИЛИ, четыре блока элементов И, четыре элемента И, элемент ИЛИ и второй- триггер управле ния, причем первый вход первого блока элементов ИЛИ соединен с выходом третьего блока элементов И, выход первого элемента ИЛИ является выходом микроопераций устройства, а второй вход соединен с выходом четвертого блока элементов И, первый вход которого соединен с первым входом т| етьего блока элементов И, второй вход - с вторым выходом регистра сдвига базовых операционных микро команд/ а третий вход - с третьим, входом третьего блока элементов И и с вторым выходом регистра адреса базовых операционных микрокоманд, третий выход которого соединен с инвер ным входом седьмого и первым входом восьмого элементов И, выходы которы соеданены соответственно с вторым и третьим входами регистра сдвига базовых операционных микрокоманд, а вторые входы соединены с выходом шестого, элемента И и с первыми входами девятого и десятого элементов И, выходы которых соединены соответ ственно с четвертым и пятым входами регистра сдвига базовых адресных иикрокоманд,а вторые входы соединены с вторым выходом буферного регистра .третий выход которого соединен с первыгии входами пятого и шестого . блоков элементов И, вторые входы которых соединены с первым и вторым выходом регистра сдвига базовых адресных микрокоманд соответственно, а выходы - с первым и вторым входами второго блока элементов ИЛИ, вы ход которого соединен с вторым входом первого дешифратора, четвертый выход буферного регистра соединен с первым входом седьмого блока элементов И, второй вход которого соедине с выходом второго элемента НЕ,третий вход - с единичным выходом второго триггера управления и первым входом элемента ИЛИ второй вход которого соединен с единичным выходом первого триг гера управления,а выход -с первым входом пятого элемента И,единичный вход второго триггера управления соединен с выходом четвертого элемента И, выход седьмого блока элементов И соединен с первы м входом третьего блока элементов ИЛИ, второй вход которого соединен с четвертым выходом регистра адреса базовых операционных микрокоманд, а выход - с первым вх дом счетчика количества импульсов сд Сущность изобретения состоит в повышении быстродействия и экономичности устройства микропрограммного управления за счет формирования адресных и операционных микрокоманд, входящих в реализуелые микропрограм мы из множества базовых адресных и операционных микрокоманд, записанны в первый и третий запоминающие блоки, путем выполнения операций инвертирования и реверсивного сдвига. Оптимизация первого запоминающего блока состоит из двух этапов и заключается в TQM, что на первом этапе из всего множества адресщлх микрокоманд Qg (1Ь 1,R, где R - количество линейных последовательностей, входящих в реализуемые микропрограмма), формируется некоторое множество базовых адресных микрокоманд Q, ( Между мнорд- . жествами Рд и Q рд существует отношение GJ.QJ Ррд Рду которое следует из того, что функцией отображения Ч множества QgQ на множ.естве Qg является функция циклического сдвига каждого элемента множества OQ заданное число разрядов h. Из каждого элемента Q,,может быть получено по крайней мере MQ- элементов множества Q. Так, например, дпя того чтобы задать множество адресных микрокоманд Q )0000, 0001, 0010, ООН, 0100, 0110 достаточно задать множество базовых адресных микрокоманд Q. I 0000, 0001,0011}. При этом коды из множества отображаются на множестве Q следующим образом Следовательно, для множеств Q справедливо Второй этап оптимизации первого запоминающего блока аналогичен оптимизации третьего запоминающего блока и состоит в том, что из множества базовых адресных (операционных) микрокоманд (Qpo) формируется укороченное множество базовых адресных (операционных) микрокоманд Qg (Q ) . QwH Между множествами Q ) существует зависимость G aaQeA(,6ACQo6). поскольку функцией ото5рах ения множества Q (QoB s множество ( является операция инвертирования. На чертеже представлена функциональная блок-схема устройства микропрограммного управления .с базовыми множествами микрокоманд. Устройство содержит регистр 1 сдвига базовых адерсныз микрокоманд пятый и шестой блоки 2 и 3 элементов И, второй блок 4 элементов ИЛИ, первый дешифратор 5, первый блок б памяти-, регистр 7 логических условий, первый блок 8 элементов И, буферный регистр 9, имеющий четы1ре поля: поле 10 задания базового адреса, поле 11 задания числа сдвигов, поле 12 признака направления сдвига, поле 13 признака инвертирования адресной микрокоманды, второй блок 14 элементов И, седьмой блок 15 элементов И, второй триггер 16 управления, десятый и девятый элементы И 17 и 18 соответственно,шифратор 19, счетчик 20 количества микрокоманд, первый элемент И 21, второй элемент И 22, шестой элемент И 23, восьмой элемент И 24, регистр 25 сдвига базовых опер ционшлх микрокоманд, третий, четвертый блоки элементов ТЛ 26 и 27 соответственно, первый блок 28 элементов ИЛИ, седьмой элемент И 29, второй элемент 30 задержки, первый триггер 31 управления, элемент ИЛИ 32, пятый элемент И 33, третий блок 34 элементов ИЛИ, счетчик 35 количества импульсов сдвига, элемент И-НЕ 36, второй элементНЕ 37, первый элемент 38 задержки, третий элемент И 39, генератор 40 тактовых импульсов, пер вый элемент НЕ 41 и четвертый эле.мент И 42, счетчик 43 адреса микрокоманды второй дешифратор 44, второй блок памяти 45, регистр 46 адреса базовых операционных микрокоманд третий де 1Ифратор 47, tf етий блок 48 памяти, вход 49 кода операций регистра (глвига базовых адресных микро команд, первый, третий, второй и четверть й выхода 50-53 первого запоминающего блока, вход 54 значений логич:еских условий, выход 55 микроопераций устройства,. В первом запоминающем блоке 6 памяти хранятся базовые адресные NOiKpOKOMaHflB , Первый выход -50 первого запоминаю щего блока 6 предназначен для записи б&зовых адресных микрокоманд в буферный регистр 9. Первое поле 10 буферного регистра 9 предназначено для хранения базовой адресной микрокоманды, второе оле 12 представляет собой поле метки, в котором.записывается единичное значение сигнала, еЪли адрес микрокоманды, считываемой из пер вого запо линакйцего блока 6, записанный в регистр 1 сдвига базовых адресных микрокоманд 1, используется в прямом виде, и значение нуля - если в инверсном виде. Третье поле 13 представляет собой поле метки, значе ние которой равно единице, если сдви базовой -операционной микрокоманды необходимо осуществлять в сторону старших разрядов, и нулю, когда сдвиг необходимо осуществлять в сторону младших разрядов. Регистр 1 сдвига базовых адресных микрокоманд предназначен для осуществления операции циклического сдвига и является реверсивным. Регистр 7 логических условий осуществляет хранение кода - логических условий в течение времени выполнения текущей линейной последовательности с целью модификации адреса первой микрокоманды очередной линейной последовательности по результатам проверки значений соответствующих логических условий.. Шифратор 19 предназначен для формирования кода адреса первой микрокоманды и кода микрокоманд в последовательности. Счетчик 20 микрокоманд предназначен для счета числа выполненных микрокоманд по сигналам считывания микрокоманд из третьего запоминающего блока 48 памяти. Первый и второй триггеры 31 и 16 управления, а а также счетчик 35 количества импульсов сдвига образуют-узел управления выполнением операций циклического сдвига. Регистр 25 сдвига базовых операционных микрокоманд является реверсивным и служит для формирования операционных микрокоманд. Генератор 40 тактовых импульсов и имеет два выхода, первый из которых предназначен для тактирования работы устройства микропрограммного управления импульсами с частотой следования , а второй выход - для осуществления операций, сдвигов импульсами с частотой следования / , причем i Во втором запоминающем блоке 45 памяти;, хранятся адреса базовых операционных микрокоманд. : Регистр 46 адйэеса базовых операционных микрокоманд имеет четыре выхода: по первому выходу считывается адрес базовой операционной микрокоманды, по второму - сигнал управления инвертированием базовой операционной /микрокоманды, по третьему - сигнал управления направлением сдвига базовой операционной микрокоманды, по четвертому - код числа импyльqpв сдвига. В третьем запоминающем блоке 48 памяти хранятся базовые операционные микрокоманды, составляющиенепапное множество базовых операционных микрокоманд. В счетчик 35 количества импульсов сдвига записывается информация о количестве импульсов сдвига, необходикых для формирования операционных микрокоманд, а также информация о количестве импульсов сдвига, необходи1«1Х для формирования адресных микрокоманд. В связи с записью в счетчик 35 количества импульсов сдвига информации двух видов в течение време выполнения микропрограммы различают два режима работы счетчика 35. В пер вом режиме работы счетчик 35 участвует в формировании операционных микрокоманд, во втором -в формировании адресных микрокоманд. В течение времени выполнения линейной последовательности микрокоманд в счетчик 35 из регистра 46 адресов базовых операционных микрокоманд записывается код числа импульсов сдвига. После того, как про исходит считывание базовой операционной микрокоманды в регистр 25 сдвигов, начинается операция формирования операционной микрокоманды. Операция сдвига базовой операционной микрокоманды с целью уменьшения времени формирования может выполнят ся в двух направлениях. Направление сдвига задается сигналом с третьего выхода регистра 46 адреса базовых операционных микрокоманд. Сигналом с второго выхода регистра 46 задается признак инвертирования операционной микрокоманды. В процессе функционирования микропрограммного устройства управлени формирование адресов микрокоманд происходит в счетчике 43 адресов микрокоманд. После выполнения опера ционной микрокоманды сигналом с второго выхода третьего запоминаюlaero блока 48 памяти происходит уве личение содержимого счетчика 43 на единицу и уменьшение на единицу содержимого счетчика 20. После того , как сформируется и считается последняя операционная микрокоманда линейной последователь ности, признаком чего является нулевое состояние счетчика 20 микрокоманд, счетчик 35 количества импульсов сдвига работает в режиме фо мирования адреса первой микрокоманды следующей линейной последователь кости. Код числа импульсов сдвига -записывается в счетчик 35 с четвертого выхода буферного регистра 9. С второго выхода поступает сигнал у:1равления направлением сдвига, ас третьего - признак инвертирования ащзесной микрокомандгл. После того, как сформируется адо первой микрокоманды линейной последовательности, счетчик 35 возвращается в исходное положение. Операция циклического сдвига базовых операционных и адресных микро команд осуществляется импульсами вы сокой частоты, поступающими с второ го выхода генератора 40 тактовых им пульсов . Устройство микропрограммного управления работает следующим образом Б исходном положении все элементы памяти находятся в нулевом состоянии. В третьем поле 13 буферного регистра 9 написана единицапpиз aк прямого значения кода операции. По первому тактовому импульсу с первого выхода генератора 40 тактовых импульсов через время срабатывания одного элемента задержки С,, при соответствующем разрешающем сигнале с выхода элемента И 21 (счетчик 20 микрокоманд обнулен), происходит запуск первого дешифратора 5, регистра 7 логических условия и подтверждение нулевого состояния -второго триггера 16 управления. Сигналом с выхода второго элемента 30 задержки первый триггер) 31 управления устанавливается в единицу. Из первого запоминающего блока 6 по коду операции считываются адрес первой микрокоманды линейной последовательности с третьего выхода 52, адрес базовой операционной микрокоманды с первого выхода 50, ход логических условий с третьего выхода 52. Сигналом с четвертого выхода 53 происходит обнуление адресного регистра 1. Адрес базовой адресной микрокоманды поступает в буферный регистр 9. Код логических условий поступает в регистр логических условий) Адрес первой микрокоманды линейной последовательности поступает в шифратор 19, откуда с первого выхода записывается код количества микрокоманд счетчика 20 микрокоманд, а с второго выхода в счетчик 43 адресов микрокоманд записывается адрес первой ьдакрокоманды текущей линейной последовательности. Сигнал на выходе элемента И. 21, причем нулевое значение, через первый элемент НЕ 41 открывает элемент И 42. Следующим тактовым импульсом через открытый элемент И 42 происходит обнуление регистра 46 базовых операционных микрокоманд и запуск второго дешифратора 44. Из второго запоминающего блока считывается адрес базовой операционной микрокоманды, код числа импульсов сдвига,признаки управления направлением сдвига и инвертированием. Вся информация записывается в регистр 46 адреса базовых операционных микрокоманд, откуда код числа импульсов сдвига с четвертого выхода поступает на второй вход третьего блока 34 элементов ИЛИ и далее на второй вход счетчика 35 количества импульсов сдвига. Сигнсш на выходе элемента И-НЕ 36 принимает единичное значение и открывает элемент и 29. Через время tx сигналом с выхода первого элемента 38 згщержки происходит запуск третьего дешифратора 47 и третьего запоминающего блока 48 памяти. С первого выхода сосчитывается код базовой операционной микрокоманды и записывается в регистр 25 сдвига. Сигналом с второго выхода происходит формирование адреса очередной микрокоманды линейной последовательности . путем увеличения на единицу содержимого счетчика 43 адреса. Содержимое сче.тчика 20 микрокоманд уменьшается на единицу тем же сигналом . После того, как запишется код базо вой операционной микрокоманды в регистр 25, тактовые импульсы высокой частоты с второго выхода генератора 40 тактовых импульсов через открытый пятый элемент И 33 поступают на счетный вход счетчика 35 и на второй вход шестого элемента И 23, с выхода которого они посту-пак т на вторые входы седьмого и восьмого элементов И 29 и 24 соответственно. На первые входы этих элементов поступает сигнал управления с четвертого выхода регистра 46 адреса базовых операционных микрокоманд. В момент обнуления счетчика 35 сигнал На выходе элемента И-НЕ 36 равен нулю, он закрывает шестой элемент И 23, а также через второй элемент НЕ 37 производит установку в нуль первого триггера 31 управления .Нулевой сигнал с выхода триггера 31 поступает на первые входы третьего и четвертого блоков элементуэв ТЛ 26- 27 соответственно. На второй вход третьего блока элементов И 26 поступают прямые значения разрядов кода операционной микрокоманды, а на второй .вход четвертого блока элементов VI 21 - обратные их значения. В зависимости от значения управляющего сигнала с второго выходарегистра 46 адреса базовых операционных микрокоманд происходит считывание прямого или инверсного кода операционной микрокоманды из регистра 25. Код операционной микрокоманды по ступает на один из входов первого блока 28 элементов ИЛИ, выход которо го является выходом устройства. Через время Т сигналом с выхода второго элемента 30 задержки происхо дит установка в единицу первого триг гера 31 управления. Единичный сигнал с единичного выхода триггера 31 поCTyniieT через элемент ИЛИ 32 и открывает пятый элемент И 33.. Очередны тактовым импульсом с первого выхода генератора 40 тактовых импульсов через открытый элемент И 42 происходит обнуление регистра 46 адреса базовых операционных микрокоманд и запуск второго дааифратора 44. В дальнейшем работа устройства микропрограммного управления аналогична описанной. После того, как сосчитается последняя операционная микрокоманда линейной последовательности тактовым импульсом с выхода элемента И 22 происходит передача кода базовой адресной микрокоманды с первого выхода регистра 9 через второй блок 14 элементов И в регистр 1 сдвига базовых адресных микрокоманд. Этим же сигнатом второй триггер 16 управления устанавливается в единичное состояние. Сигналом с единичного выхода триггера 16 элемент И 33 открывается, и происходит запись кода числа сдвигов базовой адресной микрокоманды через седьмой блок 15 элементов И и третий блок 34 элементов ИЛИ в счетчик 35 количества импульсов сдвига.. В результате на выходе элемента И-НЕ 36 появляется единичный сигнал, который поступает на второй вход шестого элемента И 23 и открывает его. Импульсы высокой частоты с второго выхода генератора 40 тактовых имимпульсов поступают на счетный вход счетчика 35 количества импульсов сдвига, а также через шестой элемент И 23 - на первые входы девятого и десятого элементов И 18 и 17 соответСтвенно. Кроме того, импульсы высо.кой частоты с выхода шестого элемента И 23 поступают на вторые входы элементов И 24 и 29, в результате чего производится циклический сдвиг нулевого кода регистра 25. На вторые входы девятого и десятого элементов И 18 и 17 поступает сигнал управления направлением сдвига с второго выхода регистра 9. После того, как заканчивается операция сдвига базовой адресной микрокоманды в регистре 1, состояние счетчика 35 количества импульсов сдвига становится нулевым, происходит обнуление первого триггера 31 управления и единичный сигнал с его нулевого выхода поступает на первые входы третьего 26 и четвертого 27 блоков элементов И, а также на третьи.входы пятого 2 и шестого 3 блоков элементов . И.Поскольку в регистре 25 записан нулевой код, то считывание информации из иего не происходит. В зависимости от значения сигнала, поступающего с третьего выхода регистра 9, по коду (прямому или инверсному) адреса первой микрокоманды линейной последовательности через первый или второй входы второго блока элементов ИЛИ по сигналу с выхода элемента И 39 происходит считывание адреса первой микрокоманды линейной последовательности из первого запоминающего блока 6. В дальнейшем работа схема повторяется. Объем запоминающих блоков предла гаемого устройства микропрограммног управления оценивается выражением v,,„ м в «o«гNБo +еооГа Бо)бо%о где Мдр, MgQ- разрядности базовых ад ресных и операционных микрокоманд; N - число базовых операционных микрокоманд. Из сравнения величин W и W,, сле дует , что . AW W , - Wn7 О , так как . . MR, MO Ав А Следовательно, предлагаемое устройство превосходит известное по быстродействию и экономичности зволяет строить устройства с меныйц объемом запоминающих блоков. Формула изобретения Устройство микропрограммного управления, содержащее первый дешифратор, выход которого подключен к входу первого блока памяти, выход адреса базовой операционной микрокр манды которого подключен к входу ба зового адреса буферного регистра, вход логических условий которого по ключен к выходу первого блока элеме тов И, выход поля задания базового адреса буферного регистра соединен первым входом второго блока элементов И, выход которого подключен к первому входу регистра сдвига базовой адресной микрокоманды, второй вход которого подключен к входу код операции устройства, первый вход пе вого блока элементов И соединен с входом логических условий устройства, а второй вход подключен к выход регистра логических условий, первый вход которого соединен с выходом кода логических условий первого бло ка памяти, выход адреса первой микр команды которого подключен к входу шифратора, первый выход которого с единен с информационным входом счет чика количества микрокоманд, а второй выход - с информационным входом счетчика адреса микрокоманд, выход которого подключен к первому входу второго доиифратора, выход которого соединен со вторым блоком памяти, в ход которого подключен к информационному входу регистра адцреса базовых операционных микрокоманд, первы выход которого подключен к первому входу третьего дешифратора, выход которого соединен со входом третьег блока памяти, первый выход которого соединен со счетным входом счетчика адреса микрокоманд и счетчика количества микрокоманд, выхода которого подключены ко .входам первого элемента И, выход которого соединен с первым входом второго элемента И, третьего элемента И и через первый элемент НЕ с первым входом четвертого элемента И, выход которого подключен ко вто рому входу второго дешифратора и входу установки в нуль регистра адреса базовой операционной микрокоманды, второй вход четвертого элемента И соедине с первым выходом генератора тактовых импульсов и через первый элемент задержки - со входом установки в нуль регистра сдвига базовых операционных микрокоманд, со вторым входом третьего дешифратора, со вторым входом третьего элемента И и .входом второго элемента задержки, выход которого соединен с единичным выходом первого триггера управления и вторым входом первого элемента И, выход которого соединен со вторым входом второго блока элементов И, выход третьего элемента И соединен со входом установки в нуль буферного регистра, регистра логических условий, счетчи, ка адреса микрокоманд и вторым входом первого дешифратора, нулевой вы-, ход первого триггера управления соединен с первым входом третьего блока элементов И, второй вход которо.го соединен с выходом регистра сдвига базовых операционных микрокоманд, первый вход которого соединен со вторым выходом третьего блока памяти, второй выход генератора тактовых импульсов соединен со вторым входом пятого элемента и, выход которого соединен с первым входом шестого элемента И и со счетным входом счетчика импульсов количества сдвига, выходы которого через элементы И-НЕ соединены со вторым входом шестого элемента И, а через второй элемент НЕ со входом нуля первого триггера управления, выход обнуления первого блока пги«1яти подключен к третьему входу регистра сдвига базовых адресных микрокоманд, отличающееся тем, что, с целью повышения быстродействия, в него дополнительно введены три блока элементов ИЛИ, четыре блока элементов И, четыре элемента И элемент ИЛИ и второй триггер управления, причем первый вход первого блока элементов ИЛИ соединен с выходом третьего блока элементов И, выход первого элемента ИЛИ является выходом микроопераций устройства, а второй вход соединен с выходом четвертого блока элементов И, первый вход КОТОРОГО подключен к первому входу третьего блока элементов И, второй вход - к второму выходу регистра

. сдвига базовых операционных микрокоманд, а третий вход - к третьему входу третьего блока элементов И и к второму выходу регистра адреса разовых операционных микрокоманд, третий выход которого соединен с инверсным 5 входом седьмого и первым входом восьмого элементов И, выходы которых соединены соответственно с вторым и третьим входами регистра сдвига базовых операционных микрокоманд, а вторые 10 входы соединены с выходом шестого элемента И и с первыми входами девятого и десятого элементов И, выходы которых соединены соответственно с четвертым и пятым входами регистра сдви- 5 га базовых адресных микрокоманд, а вторые входы соединены с вторым выходом буферного регистра, третий выход которого соединен с первыми входами пятого и шестого блоков элемен- тов И, вторые входы которых соединены с первым и вторым выходом регистра сдвига базовых адресных микрокоманд соответственно, а выходы - с первым и вторым входами второго блока элементов ИЛИ, выход которого соединен с вторым входом первого дешифратора, четвертый выход буферного-регистра соединен с первым входом седьмого блока элементов И, второй вход которого соединен с выходом второго элмента НЕ, третий вход - с единичным выходом второго триггера управления и первым входом элемента ИЛИ, второй вход которого соединен с единичным выходом первого триггера управления, а выход - с первым входом пятого элемента И, единичный вход второго триггера управления соединен с выходом четвертого элемента И, выход седьмого блока элементов И соединен с первым входом третьегчэ блока элементов ИЛИ, второй вход которого соединен с четвертым выходом регистра адреса базовых операционных микроком нд, а выход - с первым входом счетчика количества импульсов сдвига.

Источники информации, принятые во внимание при экспертизе

3г.- Авторское свидетельство СССР 763898, кл.С 06 F 9/22, 1978.

Авторы

Даты

1982-09-23—Публикация

1980-12-08—Подача