(5) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1980 |

|

SU935960A1 |

| Микропрограммное устройство управления | 1980 |

|

SU959080A1 |

| Микропрограммное вычислительное устройство | 1981 |

|

SU1008741A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

| Микропрограммное устройство управления | 1981 |

|

SU962943A1 |

| Устройство для микропрограммногоупРАВлЕНия C КОНТРОлЕМ | 1979 |

|

SU809183A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1016782A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1091158A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано при разработке микропрограммных устройств управления высоконадежных выми9лительных и управляющих систем.

Известно микропрограммно.е устройство управления l Недостатком этого устройства является низкая функциональная надеж- j ность, вызванная невозможностью реализации устройствами микрокоманд, при выполнении которых обнаружен устойчивый отказ. При обнаружении сбоев в этом устройстве осуществляется по- 5 вторение соответствующих микрокоманд и если после определенного числа повторений сбой не устраняется, производится блокировка работы и переход в режим диагностирования. 20

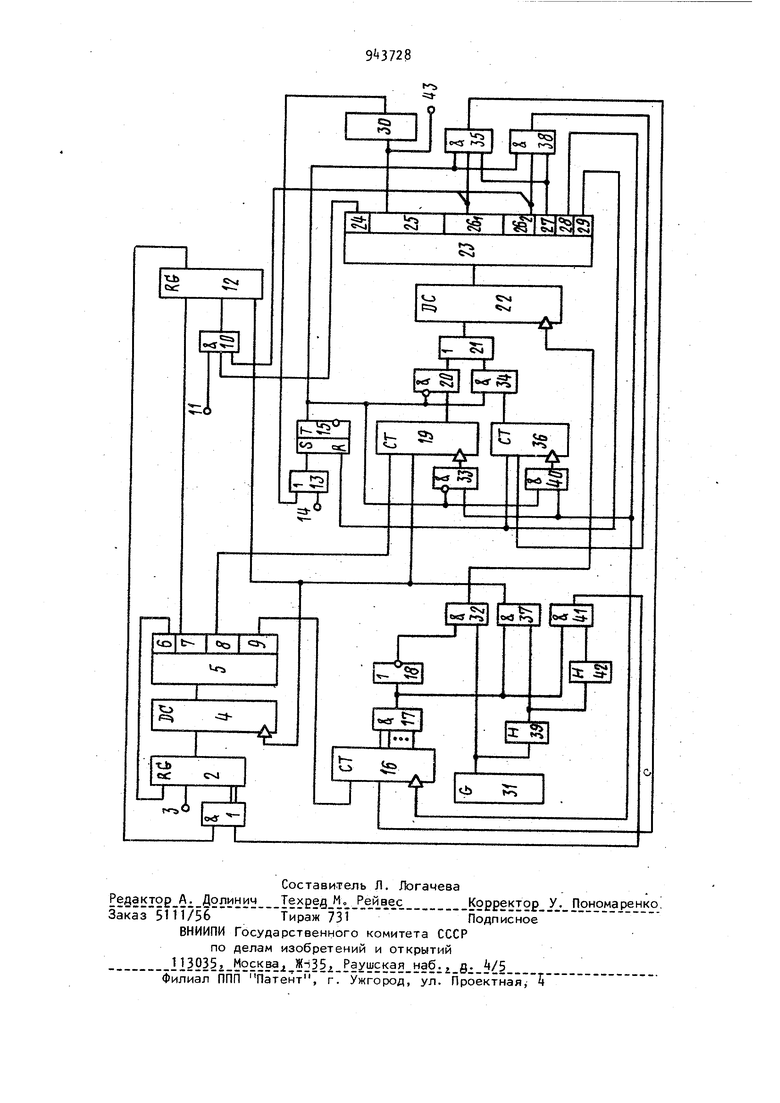

Наиболее близким по технической сущности и достигаемому положительному эффекту к предлагаемому является микропрограммное устройство управления, содержащее последовательно соединенные адресный регистр, первый дешифратор, первый запоминающий блок, буферный регистр, первый блок элементов И, выход которого соединен с первым входом адресного регистра, второй вход которого является входом кода операции устройства, а установочный вход соединен со вторым выходом первого запоминающего блока, третий и четвертый выходы которого соединены соответственно с первыми информационньми входами счетчика микрокоманд и счетчика адреса, установочный вход которого соединен с управляющим входом первого дешифратора, выходом первого элемента И и установочным входом буферного регистра, второй вход которого соединен с выходом второго блока элементов И, первый вход которого является входом логических условий устройства, второй вход соедиг нен с первым выходом второго запоми-ч нающего блока, а третий - с его вто39рым и третьим выходами, четвертый выход второго запоминающего блока является выходом микроопераций устро ства, а пятый, выход соединен со счет ным входом счетчика микрокоманд, выходы которого через второй элемент И соединены с первыми входами первого и третьего элементов И, а через элемент НЕ - с первым входом четвертого элемента И, выход которого соединен с упрзавляющим входом второго дешифратора, выход которого соединен со входом второго запоминающего блока; второй вход четвертого элемента И соединен с выходом генератора импуль сов, а через первый элемент задержки - со вторьм входом первого элемен та И и входом второго элемента задержки, выход которого соединен со вторым входом третьего элемента И, выход которого соединен со вторым входом первого блока элементов И 2 Недостатком указанного устройства является низкая функциональная надежность, обусловленная отсутствием возможности самовосстановления работы при устойчивом отказе одной из микрокоманд , отказе соответствующих цепей управления операционного блока или разрядов микроопераций запоминающего блока . Целью изобретения является повышение функциональной надежности устройства. Поставленная цель достигается тем что микропрограммное устройство упра ления, содерждщее регистр адреса, дв дешифратора, два блока памяти, буфер ный регистр, счетчик микрокоманд, счетчик адреса/ четыре элемента И, два элемента задержки, генератор так товых импульсов,два блока элементов И, элемент НЕ, причем выход первого блока элементов И подключен к первому входу регистра адреса, второй вход которого соединен с входом кода операции устройства, а установочный вход - с первый выходом первого блог ка ПШ4ЯТИ, второй и третий выходы которого подклочены соответственно к информационным входам счетчика микрокоманд и счетчика адреса, установочный вход которого соединен с управляющим рходом первого дешифрато ра, выходом первого элемента И и установочным входом буферного регистра первый вход которого подключен к выходу второго блок,а элементов И, второй вход соединен с четвертым выходом первого блока памяти, адресный вход которого подключен к выходу первого дешифратора, .вход которого соединен с выходом регистра адреса, выход буферного регистра соединен с первым входом первого блока элементов И, второй вход которого подключен к выходу второго элемента И, первый вход которого соединен с первым входом первого элемента И, а через элемент НЕ с первым входом третьего элемента И и с выходом четвертого элемента И, входы которого подклочены к выходам счетчика микрокоманд, сметный вход которого соедиг нен с первым выходом второго блока памяти, второй выход которого подключен к первому входу второго блока элементов И, второй вход которого подключен к входу логических условий устройства, а третий вход второго блока элементов И соединен с третьим и четвертьм выходами второго блока памяти, пять1Й выход которого соединен с выходом микроопераций устройства, вход второго блока памяти соединен с выходом второго дешифратора, управляющий вход которого подключен к выходу третьего элемента И, второй вход которого соединен с выходам генератора тактовых импульсов и через первый элемент задержки - с вторым входом первого элемента И, а выход первого элемента задержки соединен через второй элемент задержки с вторым входом второго элемента И, дополнительно содержит счетчик эквивалентной последовательности, узел контроля четности, третий, четвертый, пятый и шестой блоки элементов И, блок элементов ИЛИ, пятый и шестой элементы И, элемент ИЛИ и триггер, причем пятый выход второго блока памяти соединен с входом узла контроля, выхой которого подключен к первому входу элемента ИЛИ, второй вход которого соединен с входом отказа операционного блока устройства, а выход - с единичным входом триггера, нулевой вход которого подключен к установочному входу счетчика эквивалентной последовательности и к шестому выходу второго блока памяти, третий и четвертый выходы которого соединены соответственно с первыми входами третьего и четвертого блоков элементов И, к вторым входам которых подключен седьмой выход второго блока памяти, а третьи входы соединены с единичным выходом триггера, с инверсный входом пятого элемента И, с первым входом шестого элемента И, а также инверсиым входом пятого блока элементов И и с первым входом шестого блока элементов И, второй вход которого подкл чен к выходу счетчика эквивалентной последовательности, а выход - к первому входу блока элементов ИЛИ, втот рой вход которого соединен с выходом пятого блока элементов И, вход которого подключен к выходу счетчика адреса , выход блока элементов ИЛИ соединен с входом второго дешифратора, второй вход шестого элемента И соединен с входом пятого элемента И и с первым выходом второго блока памят ти, выходы пятого и шестого элементов И соединены с счетными входами счетчиков адреса и эквивалентной последовательности соответственно, выходы третьего и четвертого блоков элементов И подключены к информацион иым входам вчетчика микрокоманд и счетчика эквивалентной последователь ности соответственно. Сущность изобретения состоит в повышении функциональной надежности за счет использования естественной информационной избыточности и восста новления выполняемой микропрограммы путем: реализации микрокоманд, при выполнении которых обнаружен отказ, в виде эквивалентных линейных последовательностей операционных микрокоманд; задания в свободном поле (формата) логических условий формата микрокаманд специальных кодов, по которым осуществляется переход к реализации эквивалентных последовательностей. На чертеже представлена схема мик ропрограммного устройства управления. Устройство содержит блок 1 элемен тов И, регистр адреса 2, вход 3 кода операций, дешифратор k, блок 5 памяти (с полем 6 метки считывания ) с полем 7 косвенного адреса, полем 8 начального адреса, полем 9 длины линейной последовательности блока 10 элементов И, вход 11 логических усло вий, буферный регистр 12, элемент ИЛИ 13, вход 14 отказа операционного блока триггер 15, счетчик 1б микрокоманд, элемент И 17, элемент .НЕ 18, счетчик 19 адреса, блок 20 элементов И, блок 21 элементов ИЛИ, дешифратор 22, блок 23 памяти с полем 2 метки ветвления, полем 25 микроопераций, полем 26 логических условий, полем 27 метки микрокоманд, полем 28 метки считывания, полем 29 метки конца последовательности, узел 30 контроля на четность, генератор 31 тактовых импульсов, элемент И 32, элемент И 33, блок 3 элементов И, блок 35 элементов И, счетчик 36 эквивалентной последовательности, элемент И 37, блок 38 элементов И, элемент ЗЭ задержки, элементы И tQ, «I, элемент k2 задержки, выход микрокоопераций устройства. Устройство работает следующим образом. В исходном состоянии все элементы памяти обнулены, а в регистр 2 записан начальный адрес (код операции) . Тактовый импульс от генератора 31 проходит через открытый элемент И 37 на вход дешифратора k и из блока 5 считывается первая адресная микрокоманда. Регистр 2 обнуляется, в буферный регистр 12 записывается косвенный адрес очередной Микрокоманды, в счетчик адреса записывается начальный адрес первой линейной последовательности, а в счетчик t6 микрокоманд - код ее длины. В результате единичный сигнал на выходе элемента И 17 исчезает, а элемент И 32 открывается. Тактовые импульсы от генератора 31 через элемент И 32 поступают на дешифратор 22 и из блока 23 считываются операционные микрокоманды, которые поступают на выход 3. При этом сигналы с поля 28 уменьшают содержимое счетчика 16 и увеличивают содержимое счетчика 19. проходя через элемент И 33. Адрес очередной операционной микрокоманды поступает со счетчика 19 через блок элемента И 20. Элемент ты И АО, 3. 35 и 38 при этом остаются закрытыми. При считывании микрокоманд ветвле ) ния код логических условий из поля 2б передается на вход блока 10 элементов И и осуществляет модификацию адреса, хранимого регистром 12. После считывания последней микрокоманды происходит обнуление счетчика 16 и на выходе элемента И 17 появляется единичный сигнал. По импульсу, проходящему через элемент 42 задержки

и открытый элемент И 41, происходит передача кода из буферного регистра 12 в адресный регистр 2 через блок 1 элементов И. Следующий тактовый импульс от генератора 31 поступает через элемент 39 задержки на выход элемента И 37 и производит обнуление счетчика 19 адреса, буферного регистра 23) а также считывание очередной адресной синхрокоманды из блока 5После этого обнуляется регистр 2 сигналом с поля 6 и закрывается элемент И il вследствие записи информации в счетчик 16. В результате, импульс через элемент И Al не проходит и далее осуществляется считывание информации из блока 23 в соответстви с описанным выше алгоритмом.

Рассмотрим работу устройства при обнаружении отказа после считывания операционной микрокоманды. Сигнал отказа в этом случае формируется Элементом ИЛИ 13 либо вследствие появления сигнала на входе 1, который свидетельствует об отказе цепей операционного блока, задействованных при выполнении данной микрокоманды, либо в результате обнаружения отказа в разрядах микроопераций узлом 30 контроля на четность. По сигналу от элемента ИШ 13 триггер 15 ycтaнaвлV1вaется в единичное состояние, закрывая элементы И 33 и 20 и открывая, элеменI ты И 40, и 38.По метке,записанной в поле 27, информация из поля 26 через блоки элементов 35, 38 поступает в счетчики 1б, 19 соответст-i венно. При этом в счетчике 16 записывается код удлинения последовательности, а в счетчике 36 - начальный адрес эквивалентной последовательности.

По очередному тактовому импульсу из блока 23 считывается первая микрокоманда эквивалентной последовательности, операционная часть которой поступает на выход 43 устройства. Сигналом с выхода 28 осуществляется увеличение содержимого счетчика Зб эквивалентной последовательности и уменьшение содерйк ого счетчика 16 микрокомандь) на единицу. Последней микрокоманде соответствует единичный сигнал на выходе 29 блока 23, которым обнуляется счетчик 36 и триггер 15В результате в счетчике 19 Формируется адрес микрокоманды, следую. щей за микрокомандой, которая была

заменена эквивалентной последовательностью.

Таким образом, устройство отличается высокой функциональной надежностью, которая обеспечивается способностью устройства восстанавливать искажение микропрограммы, используя информационную избыточность.

Формула изобретения

Микропрограммное устройство управления, содержащее регистр адреса, два дешифратора, два блока памяти, буферный регистр, счетчик микрокоманд счетчик адреса, четыре элемента И, два элемента задержки, генератор тактовых импульсов, два блока элементов И, элемент НЕ, причем выход первого блока элементов И подключен к первому входу регистра адреса, второй вход которого соединен с входом кода операции устройства, а установочный вход с первым выходом первого блока памяти, второй и третий выходы которого подключены соответственно к информационным входам счетчика микрокоманд и счетчика адреса, установочный вход которого соединен с управляющим входом первого дешифратора, выходом первого элемента И и установочным входом буферного регистра, первый вход которого подключен к выходу второго блока элементов И, второй вход соединен с четвертым выходом первого блока памяти, адресный вход которого подключен к выходу первого дешифратора, вход которого соединен с выходом регистра адреса, выход буферного регистр а соединен с первым входом первого блока элементов И, второй вход которого подключен к выходу второго элемента И, первый вход которого соединен с первым входом первого элемента И, а через элемент НЕ с первым входом третьего элемента И и с выходом четвертого.элемента И, входы которого подключены к выходам счетчика микрокоманд, счетный вход которого соединен с первым выходом второго блока памяти, второй выход которого подключен к первому входу второго блока элементов И, второй вход которого подключен к входу логических условий устройства, а третий вход второго блока элементов И соединен с третьим и четвертым выходами второго блока памяти, пятый выход которого соединен с выходом микроопераций устройства, вход второго блока памяти соеди. нен с выходом второго дешифратора, управляющий вход которого подключен к выходу третьего элемента И, второй вход которого соединен с выходом генератора тактовых импульсов и через первый элемент.задержки - с вторым входом первого элемента И,, а выход первого элемента задержки соединен через второй элемент задержки с вторым входом второго элемента И, о т личающееся тем, что, с це- лью повышения надежности, дополнительно содержит счетчик эквивалентной последовательности, узел контроля четности, третий, четвертый, и шестой блоки элементов И, блок элементов ИЛИ, пятый и шестой элементы И, элемент ИЛИ и триггер, причем пятый выход второго блока паяяти соединен с входом узла контроля, выход которого подключен к первому входу элемента ИЛ1, второй вход которого соединен с входом отказа операционного блока устройства, а выход - с единичным входом триггера, нулевой вход которого подключен к установочному входу счетчика эквивалентной последовательности и к шестому выходу второго блока памяти, третий и четвертые выходы которого соединены соответственно с первьн и входами третьего и четвертого блоков элементов И, к вторым входам которых подключены седьмой выход второго блока памяти.

а третьи входы соединены с единичным выходом триггера, с инверсным входом пятого элемента И, с первым входом шестого элемента И, а также с инверсным входом пятого блока элементов И и с первым входом шестого блока элементов И, второй вход которого подключен к выхЬду счетчика зкаива-t; лентной последовательности, а выход к первому входу блока элементов ИЛИ, второй вход которого соединен с выходом пятого блока элементов И, вход которого подключен к вьйсоду счетчика, адреса,, выход блока элементов ИЛИ соединен с входом второго дешифратора второй вход шестого элемента И .соединен с входом пятого элемента И и с первым выходом второго блока памяти, выходы пятого и шестого элементов И соединены с счетными входами счетчиков адреса и эквивалентной последовательности соответственно, выходы третьего и четвертого блоков элементов И подклочены к информационным входам счетчика микрокоманд и счетчика эквивалентной последовательности соответственно.

Источники .информации, принятые во внимание при экспертизе

кл. G 06 F 9/22, 1979.

If ifSZ; , кл. G 06 F 9/22, 1972 (прототип) .

Авторы

Даты

1982-07-15—Публикация

1980-10-13—Подача