Изобретение относится к цифровой вычислительной технике и может быть использовано в блоках управления устройствами общего пользования, например в блоках управления оперативной памятью.

Известно приоритетное устройство, содержащее узел анализа запросов, две группы элементов И-НЕ, элемент И-НЕ и регистр 11 . .

Наиболее близким по технической сущности к изобретению является ; асинхронное приоритетное устройство, содержащее для и каналов и -разрядный регистр запросов и вспомогательн й п-разрядный регистр, группу элеме$1тов И-НЕ, элемент НЕ, элемент 2И, два элемента (й+1) И, а также И элементов 2И-НЕ 2.

Недостатком известных устройств является невысокое быстродействие.

Цель изобретения - повышение быстродействия и надежности устройства .

Поставленная цель достигается тем, что в асинхронное приоритетное устройство, содержащее группу из VI элементов И-НЕ, И-разрядный регистр запросов, первую группу

иэ и элементов и, элемент И и элемент НЕ, причем первые входы элементов И-НЕ группы соединены с сост.ветствующими входами запросов уст5ройства, выходы элементов И-НЕ группы соединены соответственно с соответствующими единичными входами регистра запросов, единичные выходы которых соединены с первыми

10 входами соответствующих элементов И первой группы, нулевой выход -1 -го разряда регистра запросов, кроме И-го, соединен с (ц+2)ми входами элементов И первой груп15пы, начиная со второго до и -го элемента И, входы элемента И соединены с соответствующими инверсн э1ми выходами регистра запросов, выход элемента И соединен с вторыми

20 зхбдгмк элементов И-НЕ группы и с входом элемента НЕ, введена вторая группа из и элементов и, причем первые входы элементов И второй группы соединены с первыми входами

25 соответствующих элементов И-НЕ группы, вторые входы элементов И второй группы соединены с третьими входами соответствующих элементов И-НЕ группы и с соответствующими

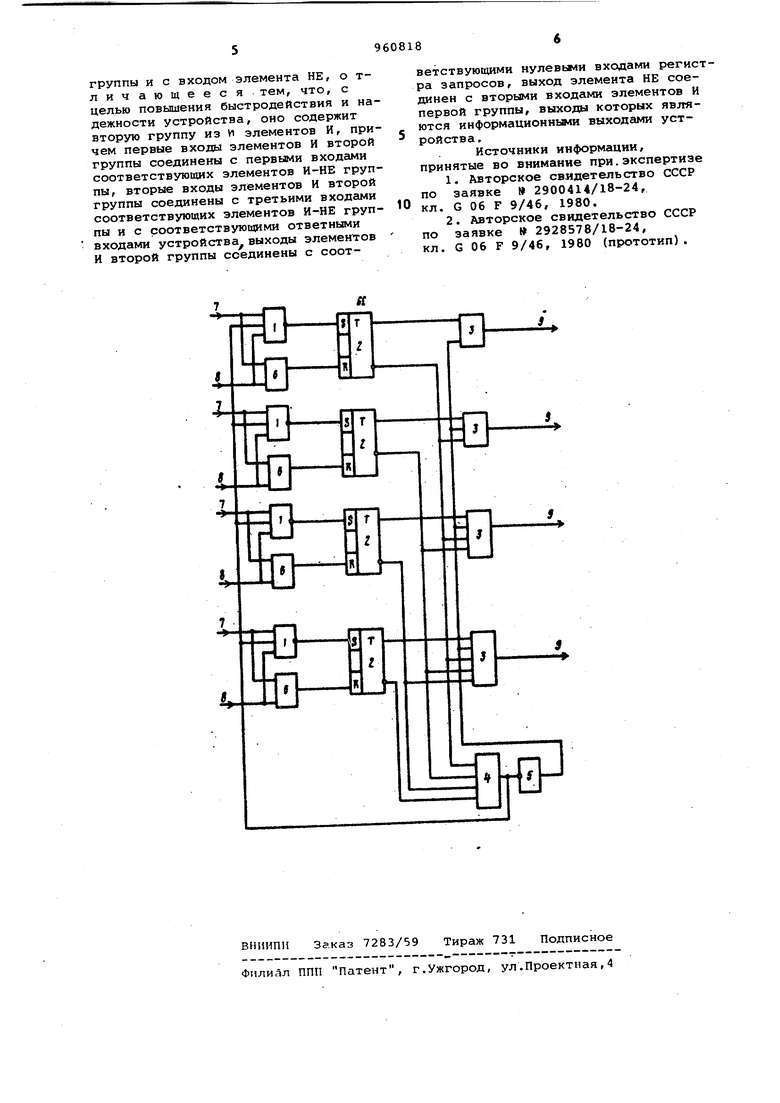

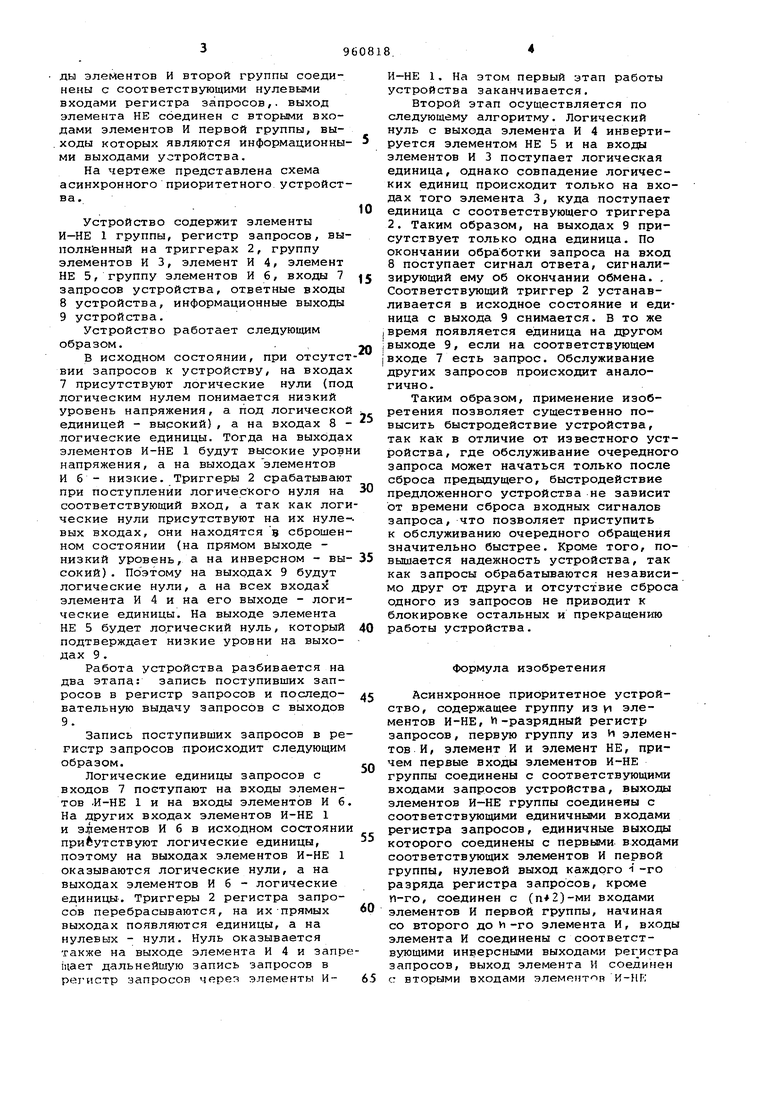

30 ответными входами устройства, выходы элементов И второй группы соединены с соответствующими нулевыми входами регистра запросов,, выход элемента НЕ соединен с вторыми входами элементов И первой группы, вы. ходы которых являются информационны ми выходами устройства. На чертеже представлена схема асинхронного приоритетного устройст ва . Устройство содержит элементы И-НЕ 1 группы, регистр запросов, выполненный на триггерах 2, группу элементов И 3, элемент И 4, элемент НЕ 5, группу элементов И 6, входы 7 запросов устройства, ответные входы 8устройства, информационные выходы 9устройства. Устройство работает следующим образом. В исходном состоянии, при отсутст ВИИ запросов к устройству, на входах 7 присутствуют логические нули (под логическим нулем понимается низкий уровень напряжения, а под логической единицей - высокий), а на входах 8 логические единицы. Тогда на выходах элементов И-НЕ 1 будут высокие уровн напряжения, а на выходах элементов И б - низкие. Триггеры 2 срабатывают при поступлении логического нуля на соответствующий вход, а так как логи ческие нули присутствуют на их нулевых входах, они находятся з сброшенном состоянии (на прямом выходе низкий уровень, а на инверсном - высокий). Поэтому на выходах 9 будут логические нули, а на всех входах элемента И 4 и на его выходе - логические единицы. На выходе элемента НЕ 5 будет логический нуль, который подтверждает низкие уровни на выходах 9 . Работа устройства разбивается на два этапа: запись поступивших запросов в регистр запросов и последонательную выдачу запросов с выходов 9. Запись поступивших запросов в регистр запросов происходит следующим образом. Логические единицы запросов с входов 7 поступают на входы элементов .И-НЕ 1 и на входы элементов И 6 На других входах элементов И-НЕ 1 и э.цементов И б в исходном состоянии присутствуют логические единицы, поэтому на выходах элементов И-НЕ 1 оказываются логические нули, а на выходах элементов И б - логические единицы. Триггеры 2 регистра запросов перебрасываются, на их-прямых выходах появляются единицы, а на нулевых - нули. Нуль оказывается также на выходе элемента И 4 и запре щает дальнейшую запись запросов в регистр запросой через элементы ИИ-НЕ 1. На этом первый этап работы устройства заканчивается. Второй этап осуществляется по следующему алгоритму. Логический нуль с выхода элемента И 4 инвертируется элементом НЕ 5 и на входы элементов И 3 поступает логическая единица, однако совпадение логических единиц происходит только на входах того элемента 3, куда поступает единица с соответствующего триггера 2. Таким образом, на выходах 9 присутствует только одна единица. По окончании обработки запроса на вход 8 поступает сигнал ответа, сигнализирующий ему об окончании обмена. , Соответствующий триггер 2 устанавливается в исходное состояние и единица с выхода 9 снимается. В то же время появляется единица на другом Выходе 9, если на соответствующем входе 7 есть запрос. Обслуживание других запросов происходит аналогично. Таким образом, применение изобретения позволяет существенно повысить быстродействие устройства, так как в отличие от известного устройства , где обслуживание очередного запроса может начаться только после сброса предьщущего, быстродействие предложенного устройства не зависит от времени сброса входных сигналов запроса, что позволяет приступить к обслуживанию очередного обращения значительно быстрее. Кроме того, повышается надежность устройства, так как запросы обрабатываются независимо друг от друга и отсутствие сброса одного из запросов не приводит к блокировке остальных и прекращению работы устройства. Формула изобретения Асинхронное приоритетное устройство, содержащее группу из и элементов И-НЕ, И-разрядный регистр запросов, первую группу из И элементов И, элемент И и элемент НЕ, причем первые входы элементов И-НЕ группы соединены с соответствующими входами запросов устройства, выходы элементов И-НЕ группы соединены с соответствующими единичными входами регистра запросов, единичные выходы которого соединены с первыми входами соответствующих элементов И первой группы, нулевой выход каждого i -го разряда регистра запросов, кроме п-го, соединен с ()-ми входами элементов И первой группы, начиная со второго до и-го элемента И, входы элемента И соединены с соответствующими инверсными выходами рег истра запросов, выход элемента И соединен с вторыми входами элементов и-НР;

группы и с входом элемента НЕ, о тличающееся тем, что, с целью повышения быстродействия и надежности устройства, оно содержит вторую группу из и элементов И, причем первые входы элементов И второй группы соединены с первыми входами соответствующих элементов И-НЕ группы, вторые входы элементов И второй группы соединены с третьими входами соответствующих элементов И-НЕ группы и с соответствующими ответными входами устройства выходы элементов И второй группы соединены с соответствующими нулевыми входами регистра запросов, выход элемента НЕ соединен с вторыми входами элементов И первой группы, выходы которых являются информационными выходами устройства.

Источники информации, принятые во внимание при.экспертизе

1.Авторское свидетельство СССР по заявке 2900414/18-24,

кл. G Об F 9/46, 1980.

2.Авторское свидетельство СССР по заявке 2928578/18-24,

кл. G 06 F 9/46, 1980 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Асинхронное приоритетное устройство | 1980 |

|

SU911529A1 |

| Асинхронное приоритетное устройство | 1983 |

|

SU1130867A1 |

| Многоканальное приоритетное устройство для динамической памяти | 1981 |

|

SU1003087A1 |

| Многоканальное устройство приоритета | 1979 |

|

SU822185A1 |

| Асинхронное приоритетное устройство | 1986 |

|

SU1336002A1 |

| Многоканальное приоритетное устройство | 1980 |

|

SU896624A1 |

| Асинхронное устройство переменного приоритета | 1986 |

|

SU1361553A1 |

| УСТРОЙСТВО ДЛЯ КОМПРЕССИИ ДАННЫХ | 2019 |

|

RU2710987C1 |

| Устройство приоритета | 1984 |

|

SU1254483A2 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 2015 |

|

RU2589317C1 |

Авторы

Даты

1982-09-23—Публикация

1980-12-30—Подача