Изобретение относится к цифровой вычислительной технике и может быть использовано в блоках управления устройствами общего пользования, например в арбитрах ЭВМ.

Целью изобретения является расширение области применения за счет возможности понижения приоритета по любому разряду с последующей обработ- кой запроса по данному разряду без смены маски.

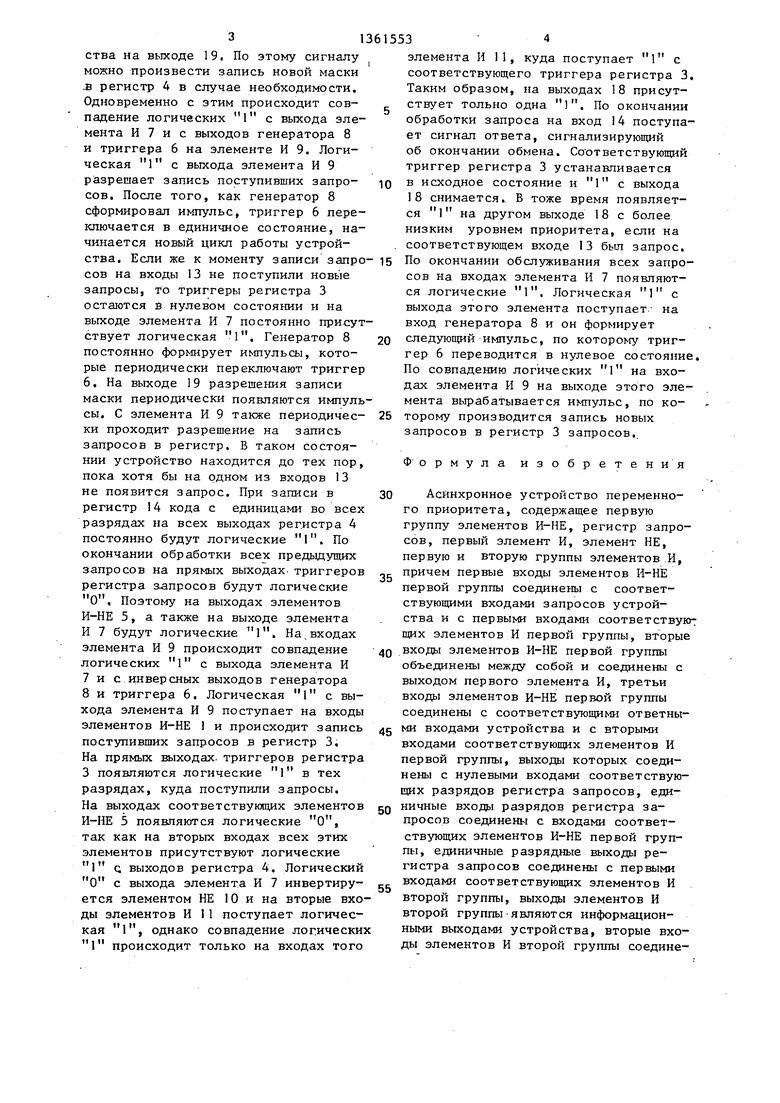

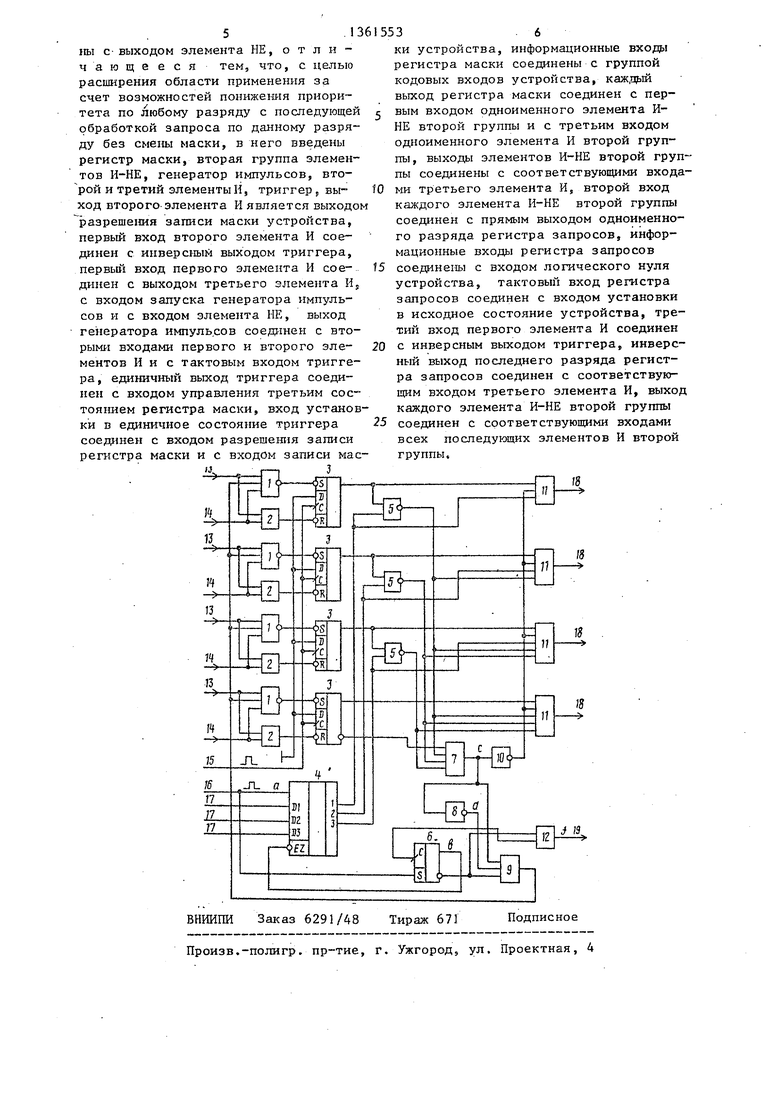

На .чертеже приведена схема предлагаемого устройства.

Устройство содержит группы злемен .тов И-НЕ I, И 2, регистр 3 запросов регистр 4 маски, группу элементов И-ПЕ 5, триггер 6, элемент И 7, генератор 8 импульсов, элемент И 9, элемент НЕ 10, группу элементов И П, элемент И 12, входы 13 запросов устройства, ответные входы 14 устройства, вход 15 установки в исходное состояние устройства, вход 16 записи маски устройства, кодовые входы

17устройства, информационные выходы

18устройства и выход.19 разрешения записи маски устройства.

Приоритетное устройство работает следующим образом.

При включении питания на вход 15 подается импульс установки в исходное состояние, который обнуляет регистр 3 запросов. После этого на входы 17 устройства подается код приоритета, причем нулевые значения разрядов указывают замаскированные уровни приоритетов. На вход 16 уст- ройства подается импульс, по которому происходит запись маски в регистр 4, Так как регистр 3 запросов обну-f. леи, то на первых входах группы элементов И-НЕ 5 присутствуют О, На первых входах элементов И 11 также присутствуют О, поэтому на выходах 18 будут О. На входах элемента И 7 и на входе генератора 8 присутствуют логические единицы, поэтому на выходе последнего форми- |руется импульс, который переводит |триггер 6 в нулевое состояние. Регистр 4 маски переводится в состояние высокого импеданса. Так как на выходе элемента И 7 продолжает присутствовать логическая единица, то генератор 8 формирует следующий им- пуЛьс, который переводит триггер 6 в единихшое состояние. На выходе элемента И 9 формируется импульс, кото

д

g 0 5

0

Q 5

5

0

5

рый разрешает запись поступивших запросов в регистр 3 запросов.

Триггеры регистра запросов, кото- рым соответствуют поступившие запросы, устанавливаются в единичное состояние. На выходах элементов И-НЕ 5 в тех разрядах, которые не замаксиро- ваны, появляются логические О, Невыходе элемента И 7 также появляется низкий потенциал, В результате этого на выходе элемента И 9 появляется О, запрещающий дальнейшую запись запросов в регистр 3,

Логический О с выхода элемента И 7 инвертируется элементом НЕ 10 и на входы элементов НЕ 10 и И 1 по-, ступает логическая 1, однако совпадение логических 1 происходит только на входах того элемента И 11, куда поступает 1 с соответствующего триггера регистра 3, Таким обрат- зом, на выходах 18 присутствует только одна 1, По окончании обработки запроса на вход 14 поступает сигнал ответа, сигнализируюш 1й об окончании обмена. Соответствующий триггер регистра 3 устанавливается в исходное состояние и с выхода 18 снимается 1. В то же время появляется 1 на другом выходе 18, если была произведена запись запроса в соответ7 ствующем разряде регистра 3 и этот разряд не замаскирован. После того, как будут обработаны все незамаскированные запросЬ, на всех входах элемента И 7 появляются логические 1, С выхода этого элемента логическая 1 поступает на вход генератора 8 и он формирует следующий импульс, по которому триггер- 6 переводится в нулевое состояние, В результате этого регистр 4 переключается в состояние высокого импеданса, С входов элементов И-НЕ 5 снимается код маски и начинается обработка запросов, которые были замаскированы. По окончании обработки этих запросов на входах элемента И 7 появляются доги- ческие 1, Логическая 1 с выхода этого элемента поступает на вход генератора 8 и на вход элемента И 12, Так как триггер 6 в это время находится в нулевом состоянии, то логическая 1 с инверсного выхода триггера поступает на второй вход элемента И 12, Логическая 1 на выходе элемента И 12 является сигналом разрешения записи маски устройства на выходе 19. По этому сигналу можно произвести запись новой маски JB регистр 4 в случае необходимости. Одновременно с этим происходит совпадение логических 1 с выхода элемента И 7 и с выходов генератора 8 и триггера 6 на элементе И 9. Логическая 1 с выхода элемента И 9 разрешает запись поступивших запро- сов. После того, как генератор 8 сформировал импульс, триггер 6 переключается в единичное состояние, начинается новый цикл работы устройства. Если же к моменту записи запро сов на входы 13 не поступили новые запросы, то триггеры регистра 3 остаются в нулевом состоянии и на выходе элемента И 7 постоянно присутствует логическая 1. Генератор 8 постоянно формирует импульсы, которые периодически переключают триггер 6. На выходе 19 разрешения записи маски периодически появляются импульсы. С элемента И 9 также периоднчес- ки проходит разрешение на запись запросов в регистр. В таком состоянии устройство находится до тех пор, пока хотя бы на одном из входов 13 не появится запрос. При записи в регистр 14 кода с единицами во всех разрядах на всех выходах регистра 4 постоянно будут логические 1. По окончании обработки всех предыдущих запросов на прямых выходах, триггеров регистра з-апросов будут логические о. Поэтому на выходах элементов И-НЕ 5, а также на выходе элемента И 7 будут логические 1. На,входах элемента И 9 происходит совпадение логических 1 с выхода элемента И

7и с инверсных выходов генератора

8и триггера 6. Логическая 1 с выхода элемента И 9 поступает на входы элементов И-НЕ 1 и происходит запись поступивших запросов в регистр 3.

На прямых выходах, триггеров регистра 3 появляются логические 1 в тех разрядах, куда поступили запросы. На выходах соответствующих элементов И-НЕ 5 появляются логические О, так как на вторых входах всех этих элементов присутствуют логические 1 Q выходов регистра 4. Логический О с выхода элемента И 7 инвертиру- ется элементом НЕ 10 и на вторые входы элементов И 11 поступает логическая 1, однако совпадение логически 1 происходит только на входах того

0 0

5

g

5

элемента И 11, куда поступает 1 с соответствующего триггера регистра 3, Таким образом, на выходах 18 присутствует тольно одна 1. По окончании обработки запроса на вход 14 поступает сигнал ответа, сигнализирующий об окончании обмена. Со ответствующий триггер регистра 3 устанавливается в исходное состояние н 1 с выхода 18 снимается. В тоже время появляется 1 на другом выходе 18 с более низким уровнем приоритета, если на соответствующем входе 13 был запрос. По окончании обслуживания всех запросов на входах элемента И 7 появляются логические 1, Логическая 1 с выхода этого элемента поступает/ на вход генератора 8 и он формирует следующий импульс, по KOTOpohty триггер 6 переводится в нулевое состояние. По совпадению логических I на входах элемента И 9 на выходе этого элемента вырабатывается импульс, по которому производится запись новых запросов в регистр 3 запросов.

Формула изобретения

Асинхронное устройство переменного приоритета, содержащее первую группу элементов И-НЕ, регистр запросов, первый элемент И, элемент НЕ, первую и вторую группы элементов И, причем первые входы элементов И-НЕ первой группы соединены с соответствующими входами запросов устройства и с первыми входами соответствую-: щих элементов И первой группы, вторые входы элементов И-НЕ первой группы объединены между собой и соединены с выходом первого элемента И, третьи входы элементов И-НЕ первой группы соединены с соответствующими ответными входами устройства и с вторыми входами соответствуюших элементов И первой группы, выходы которых соединены с нулевыми входами соответствующих разрядов регистра запросов, единичные входы разрядов регистра запросов соединены с входами соответствующих элементов И-НЕ первой группы, единичные разрядные выходы регистра запросов соединены с первыми входами соответствующих элементов И второй группы, выходы элементов И второй группы являются информационными выходами устройства, вторые входы элементов И второй группы соединены с- выходом элемента НЕ, отличающееся тем, что, с целью расширения области применения за счет возможностей понижеюгя приоритета по любому разряду с последующей обработкой запроса по данному разряду без смены маски, в него введены регистр маски, вторая группа элементов И-НЕ, генератор импульсов, вто- рой и третий элементы li 5 триггер 5 вы- ход второго-элемента И является выходом разрешения записи маски устройства, первый вход второго элемента И соединен с Ш1верс1а й выходом триггера, первьш вход первого элемента И сое- динен с выходом третьего элемента И; с входом запуска генератора импульсов и с входом элемента НЕ, выход генератора импульсов соединен с вторыми входами первого и второго эле- ментов И и с тактовым входом триггера, единичный выход триггера соединен с входом управления третьим состоянием регистра маски, вход установки в единичное состояние триггера соединен с входом разрешения записи регистра маски и с входом записи масВНИИПИ Зшсаз 6291/48 Тираж 671

Произв.-полигр.пр-тие, г. Ужгород, ул. Проектная, 4

ки устройства, информационные входы регистра маски соединены с группой кодовых входов устройства, каж.цый выход регистра маски соединен с первым входом одноименного элемента И- НЕ второй группы и с третьим входом одноименного элемента И второй группы, выходы элементов И-НЕ второй группы соединены с соответствующими входами третьего элемента И, второй вход каждого элемента И-НЕ второй группы соединен с прямым выходом одноименного разряда регистра запросов, информационные входы регистра запросов соединены с входом логического нуля устройства, тактовый вход регистра запросов соединен с входом установки в исходное состояние устройства, третий вход первого элемента И соединен с инверсным выходом триггера, инверсный выход последнего разряда регистра запросов соединен с соответствующим входом третьего элемента И, выход каждого элемента И-НЕ второй группы соединен с соответствующими входами всех последукнцих элементов И второй группы.

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство приоритета | 1990 |

|

SU1741133A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1986 |

|

SU1403069A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1287155A1 |

| Устройство для формирования сигнала прерывания | 1987 |

|

SU1432522A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Устройство приоритета | 1986 |

|

SU1365084A1 |

| Устройство для сопряжения ЭВМ с магистралью внешних устройств | 1985 |

|

SU1408440A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2014 |

|

RU2553093C1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в блоках управления устройствами общего пользования. например в арбитрах ЭВМ. Цель изобретения - расширение области применения за счет возможности изменения приоритетов запросов. Устройство содержит п-разрядный регистр запросов, две группы элементов И-НЕ, регистр маски, две группы элементов И, генератор импульсов, три элемента И, Изобретение позволяет организовать новый режим работы асинхронного приоритетного устройства} 3аключаюпцШся в возможности изменять порядок обработки запросов путем маскирования запросов с последующей их обработкой без смены маски. 1 ил. Од 05 сл ел со

| Устройство для обработки прерываний | 1983 |

|

SU1104518A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Асинхронное приоритетное устройство | 1980 |

|

SU960818A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-23—Публикация

1986-05-20—Подача