(54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВОДЛЯ РЕШЕНИЯ

УРАВНЕНИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Число-импульсное арифметическое устройство | 1980 |

|

SU951303A1 |

| Устройство для дифференцирования частоты повторения импульсов | 1974 |

|

SU525117A1 |

| Устройство для умножения и деленияпОСлЕдОВАТЕльНО-пАРАллЕльНОгОдЕйСТВия | 1979 |

|

SU817703A1 |

| Арифметическое устройство | 1985 |

|

SU1550510A1 |

| Устройство для распознавания прямого края объекта | 1988 |

|

SU1587552A1 |

| Устройство для сбора и анализа данных о работе информационно-вычислительной системы | 1990 |

|

SU1795476A1 |

| Устройство для преобразования частоты следования импульсов | 1978 |

|

SU764114A1 |

| Устройство для определения локальных экстремумов функции | 1988 |

|

SU1508205A2 |

| Цифровое устройство управление весовым дозированием | 1980 |

|

SU866418A1 |

| Устройство для воспроизведения функций | 1984 |

|

SU1182539A1 |

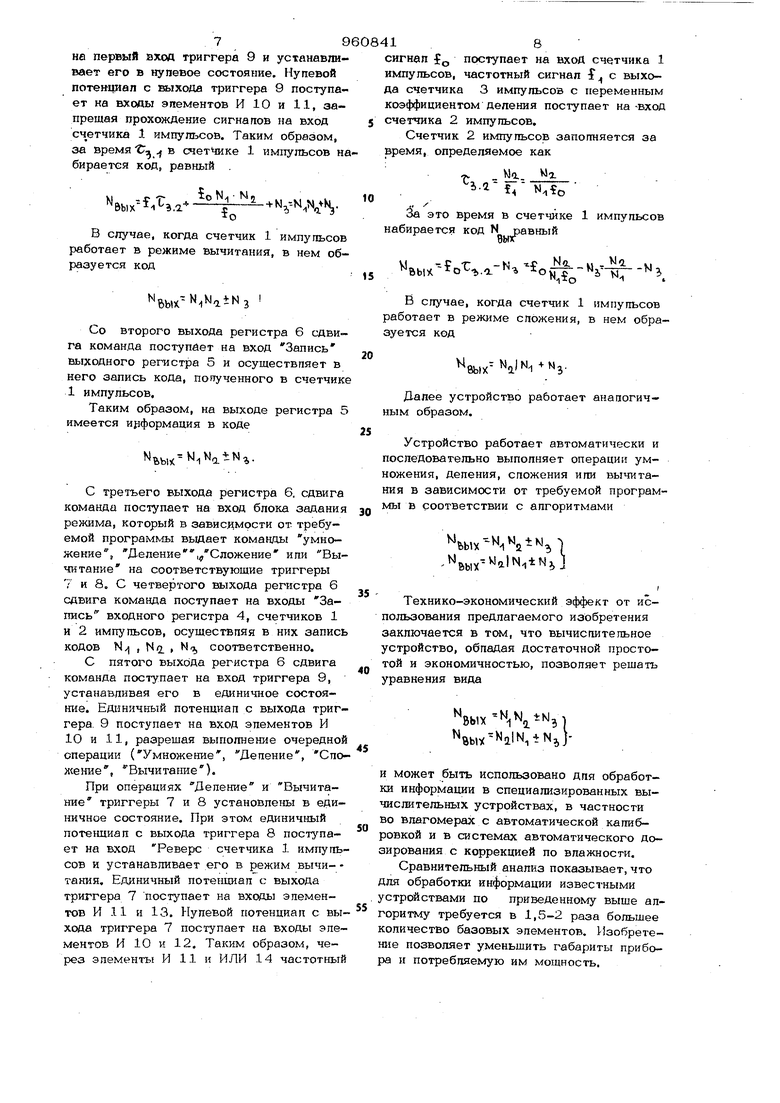

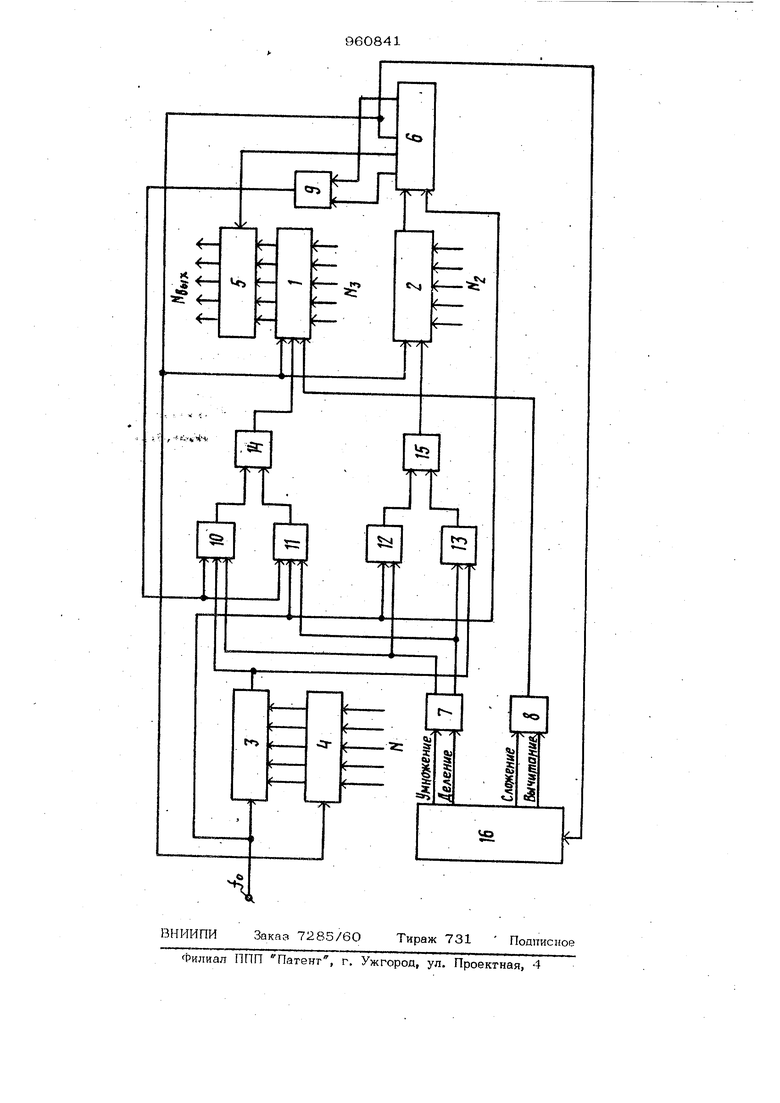

Изобретение относится к вычислитель ной технике, конкретнее к устройствам для обработки информации, в частности к устройствам для решения уравнений, и может быть использовано, например. Для обработки информации во влагомерах сыпучих материалов и в системах весового дозирования с коррекцией по влажности. Известно вычислительное устройство, предназначенное для обработки информации, пропорциональной отношению частот двух импульсных последовательностей, со держащее три счетчика, три триггера, два элемента И, элемент ИЛИ,две группы элементов И. Первые входы первого и второго триггеров соединены с первым входом элемента ИЛИ, с входами .установ ки rf О всех счетчиков и подключены к первому входу устройства. Второй вход первого триггера соединен с входами пер вой и второй групп элементов И и подключен к второму входу устройства. Один выход первого триггера подключен к первому входу первого элемента И, а один ВЫХОД второго триггера - к второму входу первого элемента И, на третий вход которого, являющийся третьим входом устройства, подается сигнал контролируемой частоты f . Выход первого элемента И подключен к, счетным входам первого и вторюго счетчиков. Выходы первой группы элементов И подключены к группе входов первого счетчика, а выходы второй группы элементов И - к группе входов второго счетчика, группы входов первой и второй групп элементов И являются группами входов устройства. Выход второго счетчика подключен к второму входу триггера и к второму входу элемента ИЛИ, выход которого подключен к первому входу третьего триггера. Выход первого счетчика подключен к второму входу третьего триггера, выход которого подключен к первому входу второго элемента И. На второй вход второго элемента И, являющийся четвертым входом устройства, подается сигнал эталонной частоты fо-Выход второго элемента Р подкпючен к счетному Bxcwy третьего счетчика Cl. В устройстве вычисляется уравнение вида ,)2..;,, где Г) - число разрядов счетчика. Однако это устройство не решает более сложную математическую зависимость с большим числом аргументов для обработ ки информации, например, в приборах для контроля параметров материалов металпур гического производства, таких, как влажность и масса сыпучего материала с коррекцией по влажности и массе пустой тары, в которых при решении таких задач необходимо использование двух известных устройств.в комплексе с другими устройствами, например сумматорами, что значительно усложняет общую схему. Наиболее близким к предлагаемому является число-импульсное решающее устройство, содержащее два счетчика три элемента И, три группы элементов И, два триггера, формироватепь импульсов, причем первые входы триггеров и счетчиков соединены с первым входом устройства, нупевой выход первого триггера .подключен к первым входам первого и второго элементов И, единичный выход второго триггера подключен к вторым входам первого и второго элементов И, выход первого элемента И подключен к второму входу первого счетчика, выход второго счетчика через формирователь - к второму входу второго триггера и является вы ходом устройства, третьи входы первого и второго элементов И являются соответственно вторым и третьим входами устройства, причем выходы элементов И пер вой группы подключены к группе входов первого счетчика, группа выходов которого через вторую группу элементов И подключена к первой группе входов второго счетчика, к Второй группе входов поспедне- го подключены выходы третьей группы элементов И, выход второго счетчика подключен к входу второй группы элементов И, входы первой и третьей групп элементов И и второй вход первого триггера подключены к четвертому входу устрой ства, нулевой выход второго триггера подключен к первому входу третьего элемента И, выходы второго и третьего элементов И подключены к входам элемента ИЛИ, выход которого подключен к второму входу второго счетчика, второй вход третьего элемента И является пятым входом устройства, группы входов первой и третьей группы элементов И являются группами входов устройс1-ва 23 В устройстве вычисляется уравнение вида N--2-it.HC,Bf.tK)--()l ,Однако, хотя это устройство решает более сложную задачу, чем предыдущее, при его использовании в системах и приборах для контроля физических параметров материалов, например в обогатительном, металлургическом и других производствах, ограниченные функциональные возможности не позволяют решать более сложную математическую зависимость с большим числом аргументов, в результате чего требуется несколько таких устройств в комплексе с устройствами получения произведения, деления и разности кодов, что значительно усложняет общую схему. Целью изобретения является увеличение напежности устройства. Эта цель достигается тем, что в вычислительное устройство для решения уравнений, содержащее два счетчика импульсов, триггер разрешения умноженияделения, триггер управления режимом, три элемента И и первый элемент ИЛИ, выход которого подключен к счетному входу первого счетчика импульсов, а первый и второй входы первого элемента ИЛИ соединены с выходами соответственно первого и второго элементов И, единичный выход триггера разрешения умножения-деления подключен к первым входам первого и третьего элемента И, а нулевой выход соединен с первым входом второго элемента И, синхронизирующий вход устройства подкпючен к вторым входам второго и третьего элементов И, а выход триггера управления режимом соединен с третьим входом третьего элемента И, введены третий счетчик импульсов триггер разрешения сложения-вычитания, четвертый элемент И, второй элемент ИЛИ, входной регистр, выходной регистр, регистр сдвига и блок задания режима, первый, второй, третий и четвертый выходы которого подключены соответственно к нулевому и единичному входам триггера разрещения умножения-деления и к нулевому и единичному входам триггера разрещения сложения-вычитания, выход триг596гера разрешения спожения-вычитавтя соединен С входом управления .спожением-вычитанием второго счетчика импуцьсов, синхронизирующий вход устройства подключен к синхронизирующему входу регистра сдвига и счетному входу третьего счетчика, выход которого соединен с вторым входом первого элемента И и пер вым входом четвертого элемента И, второй и третий входы четвертого элемента И подключены соответственно к нулевому выходу триггера разрешения умноженияделения и выходу триггера управления режимом, первый и. второй входы второго элемента ИЛИ соединены с выходами соответственно третьего и четвертого элементов И, а выход элемента ИЛИ подключен к счетному входу второго счетчика импульсов, вход первой константы устройства соединен с входом входного регистра, выход которого подключен к информационному входу третьего счетчика импуль -СОВ, вход второй константы устройства соединен с информационным входом перво го счетчика импупьсов, выход которого подключен к информационному входу регистра сдвига, первый, второй и третий выходы регистра сдвига соединены соответственно с нулевым входом триггера управления режимом, управляющим входом выходного регистра и счетным входом блока задания режима, четвертый выход регистра сдвига подключен к входам .управления записью первого и второго счетчиков импульсов и управляюшему входу входного регистра, пятый вы ход. регистра сдвига соединен с единичным входом триггера управления режимом, вход третьей константы устройства подключен к информационному входу второго счетчика импупьсов, выход которого соединен с входом.выходного регистра, а выход выходного регистра подключен к информационному выходу устройства. Кроме того, блок задания ре 1:има содержит счетчик адреса и модуль памяти, причем счетный вход блока соединен с входом счетчика адреса, выход которого подключен к входу модуля памяти, а первый, второй, третий и четвертый выходы модуля памяти соединены соответственно с первым, вторым, третьим и четвертым выходами блока. На чертеже показан один из оптимальных вариантов схемного решения предлагаемого изобретения. Вычислительное устройство содержит счетчики 1-3, импульсов, входной 4 выходной 5 регистры, регистр 6 сдвига. 416 триггер 7 разрешения умножения-деления, триггер 8 разрешения слржеиия-вычитания, триггер 9 управления режимом, элементы И 10-13, элементы ИЛИ 14 и 15, блок 16 задания режима, предназначенный для выдачи команд Умножение, Деление, Сложение, Вычитание в соответствии с заданной программой. Вычислительное устройство работает следующим образом, В исходном состоянии триггеры 7-9 установлены в нулевое состояние. При этом единичный потенциал с первого триггера 7 поступает на входы элементов И Ю и 12, нулевой потенциал с второго вхрда триггера 7 - на входы элементов И И и 13, нулевой потенииап с выхода триггера 8 - на вход Реверс счетчика 1 импульсов, устанавливая его в режим сложения последовательностей импульсов, Единичный потенциал с выхода триггеР 9 поступает на входы элементов И 10 Hi при этом частотный сигнал с счетчика импульсов через элемент И iO к элемент ИЛИ 14 поступает на счетный вход счетчика 1 импульсов. Частотный сигнал fp через элемент И 12 и элемент ИЛИ 15 поступает на счетный вход счетчика 2 импульсов. Необходимым условием работы устройства является Сз..-(, где С, . - время заполнения счетчика 1 импульсов; - время заполнения счетчика 2 импульсов. Частотный сигнал , поступает на вход счетчика 3 импульсов, который осуществ 1яет операцию умножёниявходно й частоты f Q на код N, поступающий с ВХОДНОГО регистра 4. Частота на входе счетчика 3 определяется по формуле Г- о -1Частотный сигнал fо поступает также на вход счетчика 2 импульсов, который заполняется за время Т , определяемое как Г - М. 3-а. Го После заполнения счетчика 2 на его выходе появляется импульс переноса, который поступает на вход регистра 6 сдвига и сдвигается тактовой частотой fg. При этом регистр 6 сдвига последовательно задает команды. С первого выхода регистра 6 сдвига импульс поступает на первый вход триггера 9 и устанавливает его в нулевое состояние. Нупевой потенциал с выхода триггера 9 поступает на входы элементов И Ю и 11, запрещая прохождение сигналов на вход счетчика 1 импульсов. Таким образом, за время tr в 1 импульсов на бирается код, равный Nftbix-f.Ч.а- -. о В случае, когда счетчик 1 импульсов работает в режиме вычитания, в нем образуется код Со второго выхода регистра 6 сдвига команда поступает на вход Запись выходного регистра 5 и осуществляет в него запись кода, полученного в счетчик 1 импульсов. Таким образом, на выходе регистра 5 имеется информация в коде NftbKVWi% N%С третьего выхода регистра 6. сдвига команда поступает на вход блока задания режима, который в зависимости от требуемой пpoгpaм lы выдает команды умножение, Деление .Сложение или Вычитание на соответствующие триггеры 7 и 8. С четвертого выхода регистра 6 сдвига команда поступает на входы Запись входного регистра 4, счетчиков 1 и 2 импупьсов, осуществляя в них запись кодов N , Na -я, соответственно. С пятого выхода регистра б сдвига команда поступает на вход триггера 9, устанавливая его в единичное состояние. Единичный потенциал с выхода триггера. 9 поступает на вход элементов И 10 и 11, разрещая выполнение очередной операции (Умножение, Деление, Сло жение, Вычитание). При операциях Деление и Вычитание триггеры 7 и 8 установлены в единичное состояние. При этом единичный потешхиал с выхода триггера 8 пост - пает на вход Реверс счетчика 1 импуль сов и устанавливает его в режим вычи- тания. Единичный потенциал с выхода триггера 7 поступает на вхсйы элементов И 11 и 13. Нулевой потенциал с вы хода триггера 7 поступает на входы элементов И 10 и 12. Таким образом, через элементы И 11 и ИЛИ 14 частотный сигнал fо поступает на вход счетчика 1 импульсов, частотный сигнал с выхода счетчика 3 импульсов с переменным коэффициентом деления поступает на-вход счетчика 2 импульсов. Счетчик 2 импульсов заполняется за время, определяемое как T. Ng. УДг это время в счетчике 1 импульсов набирается код N равный No. . м, .а °N,fo 1 В случае, когда счетчик 1 импупьсов работает в режиме сложения, в нем образуется код eblX)N, +N3. Далее устройство работает аналогичным образом. Устройство работает автоматически и последовательно выполняет операция умножения. Деления, сложения или вычитания в зависимости от требуемой программы в соответствии с алгоритмами ьых,м,±м .tN,, Технико-экономический эффект от использования предлагаемого изобретения заключается в тс«м, что вычисгштепьное устройство, обладая достаточной простотой и экономичностью, позволяет рещать уравнения вида ,| -N,i|N,N,,и может быть использовано для обработки информации в специализированных вычислительных устройствах, в частности во влагомерах с автоматической калибровкой и в системах автоматического дозирования с коррекцией по влажности. Сравнительный анализ показывает, что для обработки информации известными устройствами по приведенному выше алгоритму требуется в 1,5-2 раза большее количество базовых элементов. Изобретение позволяет уменьшить габариты прибора и потребляемую им мощность. Формула изобретения 1. Вычислительное устройство для решения уравнений, содержащее два счетчика импульсов, триггер разрешения умножения-Деления, триггер управления режимом, три элемента И и первый элемент ИЛИ, выход которого подключен к счетному входу первого счетчика импульсов, а первый и второй входы первого элемента ИЛИ соединены с выходами соответственно первого и второго элементов И, единичный выход триггера разрешения умножения-деления подкщочен к .первым входам первого и третьего элементов И, а нулевой выход соединен с первым входом второго элемента И, синхронизирующий вход устройства подключен к вторым входам второго и третьего элементов И, а выход триггера управления режимом соединен с третьим входом третьего элемента И, отличающееся тем, что, с целью увеличения надежности устройства, оно содержит третий счетчик импульсов, триггер разрешения сложениявычитания, четвертый элемент И, второй элемент ИЛИ, входной регистр, выходной регистр, регистр сдвига и блок задания режима, первый, второй, третий и четвертый выходы которого подключены соответственно к нупевому и единичному входам триггера разрешения умножения-деления и к нулевому и единичному входам триггера разрешения сложения-вычитания, выход триггера разрешения сложения-вычитания соединен с входом управления еложением-вычитанием второго счетчика импульсов, синхронизирующий вход устройства подкшочен к синхронизируюшему входу регистра сдвига и счетному входу тре- тьего счетчика, выход которого соединен с вторым входом первого элемента И и первым входом четвертого элемента И, второй и третий входы четвертого элемен. та И подключень: соответственно к нулево му выходу триггера разрешения умножения-деления и выходу триггера управления режимом, первьй и второй входы второго элемента ИЛИ соединены с выходами соответственно третьего и четвертого элементов И, а выход элемента ИЛИ подключен к счетному входу второго счетчика импульсов, вход первой константы устройства соединен с входом входного регистра, выход которого подключен к ни -формационному входу третьего счетчика импульсов, вход второй константы уст ройства соединен, с информационным входом первого счетчика импульсов, выход которого подключен к информационному входу регистра сдвига, первый, второй и третий выходы регистра сдвига Соединены соответственно с. нулевым входом триггера управления режимом, управляющим входом выходного регистра и счетным входом блока задания- режима, четвертый выход регистра сдвига подключен к входам управления записью первого и второго счетчиков импульсов и управляющему входу входного регистра, пятый выход регистра сдвига соединен с единичным входом триггера управления режимом, вход третьей константы устройства подключен к информационному входу второго счетчика импульсов, выход которого соединен с входом выходного регистра, а выход выходного регистра подключен к иифор - мационному выходу устройства. 2. Устройство по п. 1,отличаю щ е е с я тем, что блок задания ре жима содержит счетчик адреса и модуль памяти, причем счетный вход блока соединен с входом счетчика адреса, выход которого подключен к входу модуля памяти, а первый, второй, третий и четвертый выходы модуля памяти соединены соответственно с первым вторым, третьим и четвертым выходами блока, : Источникиинформации, принятые во внимание при экспертизе 1. Патент Японии № 47-30864, кл. G 06 F 15/32, опублик, 1972. 2. Авторское свидетельство СССР N 532097, кп. Q Об F 15/32, 1976 (прототип)

tiTi

о

-

«

f-J

7

jy

ч|

w f V:-i4-i

JT

«o

H

vo

Авторы

Даты

1982-09-23—Публикация

1980-06-26—Подача