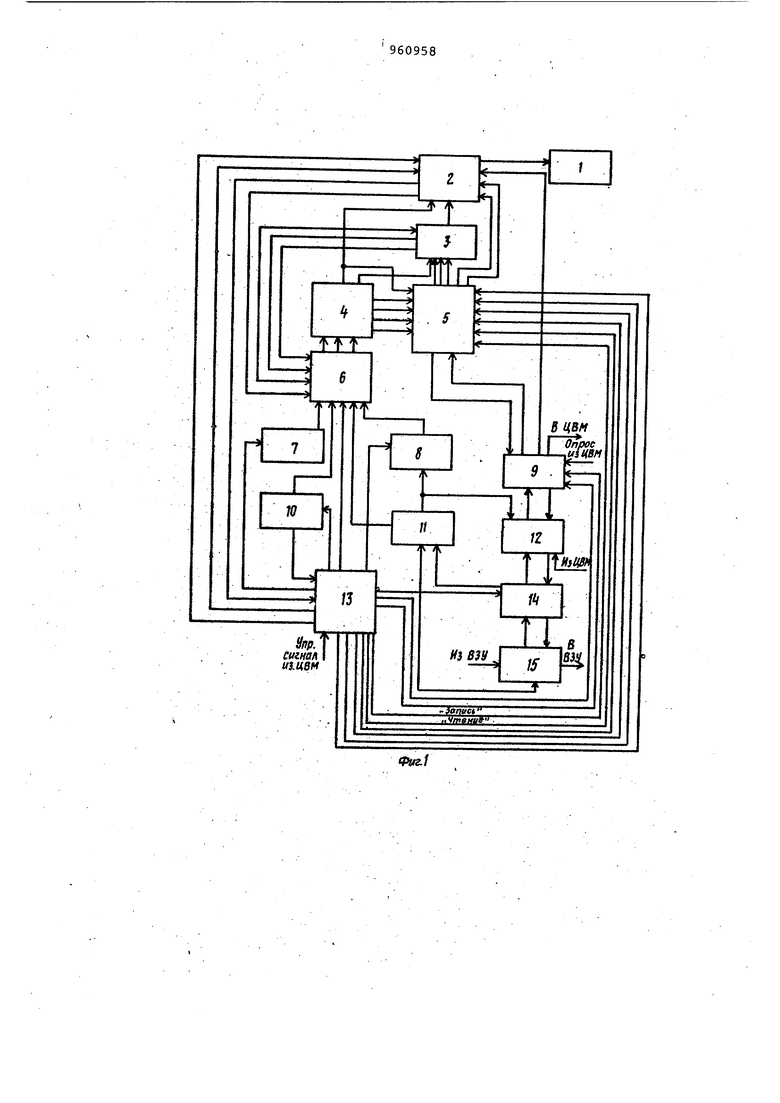

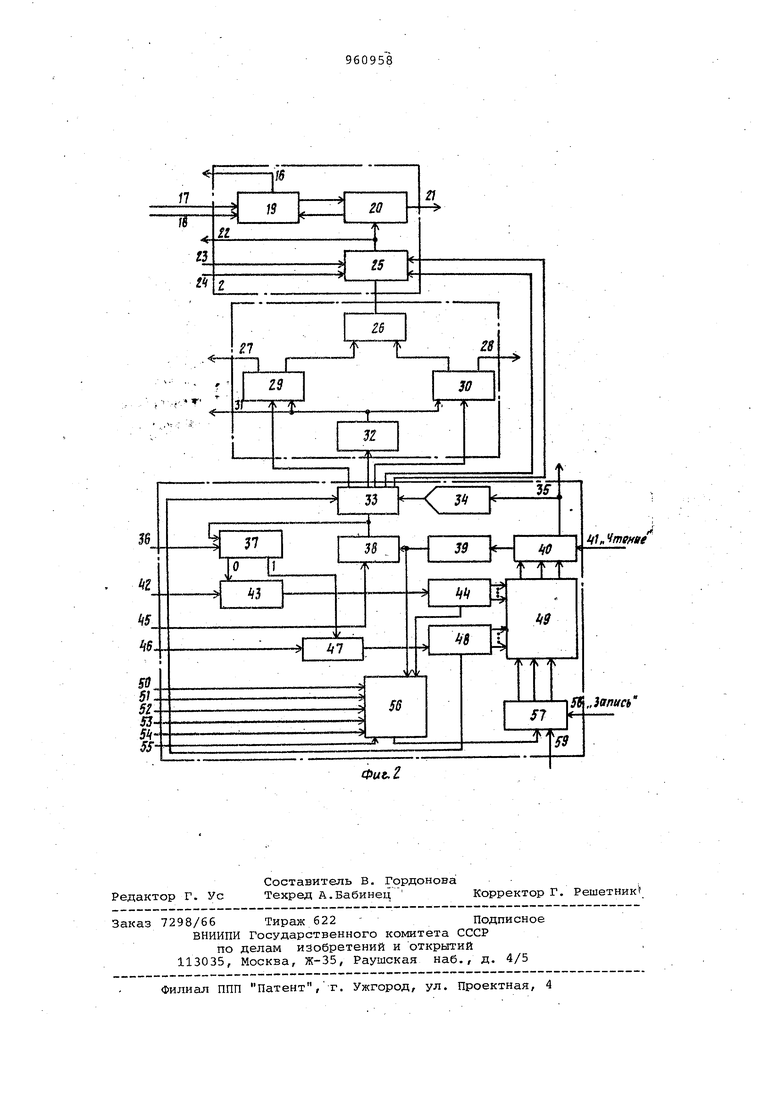

Изобретение относится к запоминаю щим устройствам и может быть использовано во внешних запоминающих устройствах (ЗУ) вычислительных машин и управляющих систем. Известно устройство для контроля запоминающих устройств, содержащее узел определения прогнозируемого параметра отказа, соединенный с блоком управления первым элементом задержки, распределителем сигналов и допол нительным блоком индикации, блок местного управления, связанный с блоком управления, вторым и третьим элементами задержки и узлом определе ния текущих значений прогнозируемого параметра отказа, соединенным с третьим элементом задержки, узлом определения кратности сбоев и распре делителем сигналов, подключенным к второму элементу задержки . Недостатком известного устройства является низкая точность контроля. Наиболее близким к изобретению по технической сущности является уст ройство для контроля ЗУ, содержащее входной регистр, подсоединенный к блоку ключевых схем, к узлу коррекции и к узлу кодирования-декодирования, связанному с узлом растяжения.сжатия кодированных слов, блок индикации, блок управления, узел определения кратности сбоев, подключенный к узлу коррекции и блоку управления, и узел регистрации распределений кратности сбоев, подсоединенный к узлу определения кратности, сбоев, блоку управления, блоку индикации и блоку ключевых схем f2J. Однако известное устройство не обеспечивает прогнозирования отказов каждого отдельного сбойного участка носителя. Это не обеспечивает достаточной точности и оперативности контроля. Целью изобретения является повышение точности контроля. Поставленная цель достигается тем, что в устройство для контроля блока памяти, содержащее информационный регистр, первые вход и выход которого подключены соответственно к первому выходу и к первому входу коммутатора , вторые вход и выход - соответственно к первому выходу и первому входу блока кодирования-декодирования, а третий вход информационного регистра подключен к первому выходу блока коррекции и к входу блока определения кратности сбоя, блок экстраполяции, первый вход которого подключен ко второму выходу коммутатора, второй вход - к первому выходу вычислителя, а первый выход - к вход блока индикации, преобразователь , информации, вход и выход которого подключены соответственно к второму выходу и к второму входу блока кодирования-декодирования,, третий выход блока кодирования-декодирования подключен к входу блока коррекции, блок управления, дополнительно введены накопитель, первые вход и выход кото рого подключены соответственно к тре тьему выходу и к второму входу коммутатора, второй выход - к третьему входу блока экстраполяции, а третий выход накопителя подключен к первому входу вычислителя, блок регистров, первый выход которого подключен к че вертому входу блока экстраполяции и к второму входу накопителя, второй вход - к второму входу вычислителя, а третий выход блока регистров подключен к третьему входу накопителя, дополнительный кo Iмyтaтop, первый вход которого подключен к выходу бло ка определения, кратности сбоев, второй вход - к второму выходу блока коррекции, третий вход - к второму выходу блока экстраполяции, а четвертый вход дополнительного коммутатора подключен к второму выходу вычислителя, первые выход дополнительного коммутатора подключен ко входам блока регистров, блок определения адреса сбоя, выход которого подключе к пятому входу дополнительного коммутатора, и блок синхронизации, выхо .которого подключен к шестому входу дополнительного коммутатора. На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 схема блок экстраполяции, вычислителя и накопителя. Устрйство содержит блок 1 индикации, блок 2 экстраполяции, вычислитель 3, блок 4 регистров, накопитель 5, дополнительный коммутатор б, блок 7 синхронизации, блок 8 опре деления кратности сбоев, KoiviMyTaTop 9, -блок 10 определения адреса сбоя, блок 11 коррекции, информационный регистр 12, блок 13 управле:ния, блок 14 кодирования-декодирования, преобразователь 15 информации, инфор мацион.ный выход 16 блоки 2 экстраполяции, управляющий вход 17 блока 2 экстраполяции, информационный вход 18 блока 2 экстраполяции, узел 19 сравнения, регистр 20, информационные входы 21 и 22 блока 2 экстрапол ции, управляющие входы 23 блока 2 экстраполяции, информационные входы 24 блока 2 экстраполяции, экстраполятор 25, сумматор 26, информационные выходы 27 и 28 вычислителя3, вычислитель 29 средней кратности сбоев, вычислитель 30 дисперсии кратности сбоев, информационные выходы 31 вычислителя 3,параллельный сумматор 32, первый узел 33 ключевых схем, схема 34 задержки, информационный выход 35 накопителя 5, управляющий вход 36 накопителя 5, триггер 37, блок 38 элементов И, регистр 39, усилители 40 считывания, управляющие входы 41 и 42 накопителя 5, ключ 43, регистр 44 сдвига зон, информационные входы 45 накопителя 5, управляющий вход 45 накопителя 5, ключ 47, регистр 48 сдвига слов, запоминающая матрица 49, информационные входы 50-54 накопителя 5, управляющий, вход 55 накопителя 5, второй узел 56 ключевых схем, усилители 57 записи, управляющий вход 58 Накопителя 5, информационный вход 59 накопителя 5. Устройство работает следующим эбразом. С блока 13 управления оператор на узле 19 сравнения блока 2 экстраполяции задает требуемое время нормальной работы с носителем для решения задач. В режиме воспроизведения после установки носителя и начала работы с ним с блока 10 бпределения адреса сбоя на блок 13 управления поступает код адреса первой зоны носителя, в которой записан файд, предыстории сбоев носителя. По сигналу с блока 13 управления блокируется выход информации в ЦВМ в коммутаторе 9 и. информация с носителя через преобразователь 15 информации, блок 1J кодирования-декодирования, информацифнный регистр 12 и коммутатор 9 поступает в накопитель 5. В накопителе 5 информация о параметрах каждого сбоя хранится в следующем виде: код адреса сбоя в виде номера зоны и номе.ра синхроимпульса в зоне, количество сбоев, озкидание и дисперсия кратности сбоев, код момента времени последнего возниконовения сбоя по данному адресу и спрогнозированное время, в течение которого не произойдет отказа сбойного участка носителя. . Одновременно со считыванием информации в накопитель 5 из дополнительного коммутатора 6 на узел 19 сравнения блока 2 экстраполяции поступает код спрогнозированного времени, в течение которого не произойдет отказа сбойного участка носителя. В узле 19 сравнения этот код сравнивается с заданным с блока 13 управления кодом требуемого времени нормальной работы и при превы1яении его подается сигнал на блок 14 индикации и иа блок 13 управления.

При поступлении с блока 10 опредеения адреса сбоя на блок 13 управления «ода адреса другой зоны блокируется в коммутаторе 9 поступление информации в накопитель 5 и блок 2 экстраполяции и растянутые кодо- вые слова поступают в преобразователь 15 информации, где они сжимаются к исходному (до записи) виду и оттуда поступают в блок кодирования-декодирования. Каждое декодированное слово поступает затем на информационный регистр 12, где оно корректируется, если в нем была одиночная ошибка, с помощью блока 11 коррекции. Первый же сигнал ошибки блока 11.коррекции при воспроизведении является сигналом начала цикла измерения кратности сбоя блоком 8 определения кратности сбоев. Одновременно по сигналу с блока 11 20 коррекции через дополнительные коммутатор б на блок 4 регистров поступают коды времени момента обнаружения сбоя с блока 7 синхронизации, адреса сбоя - с блока 10 определе- 25 ния адреса сбоя, кратности сбоя - с блока 8 определения кратности сбоев . С блока 4 регистров на вход 45 накопителя 5 подается код адреса сбоя. На регистр 39 подается код 30 адреса сбоя, хранящегося в накопителе- 5. При совпадении этих кодов с блока 38 элементов И подается сигнал на триггер 37, ключ 43 запиается, и адрес зоны в запоминающей ос атрице 49 фиксируется в регистре 44 сдвига зон для дальнейшего обновления информации в накопителе 5. Одновременно отпирается ключ 47 и через схему 34 задержки через первый узел 33 ключевых схем на параллельный сумматор 32 подается количество сбЬев по данному адресу, на вычислитель 29 средней кратности сбоев - математическое ожидание кратности сбоев, на вычислитель 30 дисперсии кратности сбоев - дисперсия кратности сбоев. В параллельном сумматоре 32 -под ко- , ичество сбоев по данному адресу увеличивается на единицу и поступает на вычислители 29 и 30.50

При отсутствии в накопителе 5 информации о сбое с регистра 44 сдвига зон на второй узел 56 ключевых схем подается сигнал и в зайоминанадУю i а грицу 49 в свободную зону с блока 55 4 регистров передаются коды времени омента обнаружения сбоя, полученные с блока 7 синхронизации кратности боя, полученный с блока 8 определеия кратности сбоев, адреса сбоя на Q осителе, полученный с блока 1.0 опеделения адреса сбоя.

Вычисленные значения мат..ожидания и дисперсии кратности сбоя постуают на входы сумматора 26 и значения 65

суммы поступает в экстраполятор 25 блока 2 экстраполяции.

Сюда же поступают коды момента времени последнего обнаружения сбоя по данному адресу и мат. ожидания кратности сбоя накопителя 5, код времени момента обнаружения сбоя, полученный с блока 7 синхронизации через дополнительный коммутат б и блок 4 регистров. По сигналу . с блока 13 управления на блока 2 экстраполяции проводится цикл прогнозирования момента времени достижения кратностью сбоя границы К. Полученный код времени поступает чёрез регистр 20 на узел 19 сравнения, где он сравнивается с указанным на блоке 13-управления и .при его превышении подается сигнал на блок 1 индикации и блок 13 управления.

По сигналу с блока 13 управления на второй узел 56 ключевых схем накопителя . 5 и на дополнительный коммутатор б в накопитель 5 по тому же адресу записывается вновь полученная информация, характеризующая сбой: с экстраполятора 25 блоКа 2 экстраполяции - код спрогнозированного времени работы со сбойным участком носителя, в течение которого возможно исправление сбоя устройством с вычислителя 29 средней крат.ности сб91ев и вычислителя 30 дисперсии кратности-сбоевы вычислителя 3 соответственно коды мат.ожидания и дисперсии кратности сбоев, с блока 4 регистров - код момента времени Обнаружения сбоя по данному адресу, с параллельного сумматора 32 вычислителя 3 - код количества сбоев по данному адресу. По новому сигналу от блока 11 коррекции цикл прогнозирования повторяется . После окончания работы с носителем по сигналу с блока 13 управления в первую зону носителя через коммутатор 9 информационного регистра 12, блок 14 :кодирования-декодирования и прербра зователь 15 информации переписывают содержимое запоминающей матрицы накопите я 5.

Таким образом, в устройстве значительно расширены функциональные воможности. Появляется возможность непосредственного контролирования опе ратором моментов отказов каждого отдельного сбойного участка носителя, тем самьам повышается точность и оперативность контроля ЗУ за счет фиксации и накопления информации о параметрах каждого отдельн,ого сбойного участка.

Кроме того, достигается увеличение срока службы носителей за счет оперативной замены предотказовых участков носителей нормальными резервными, сокращается время простоев ЗУ благодаря предотвращению отказов носителей, упрощается и облегчается техническое обслуживание ЗУ.

Формула изобретения

Устройство для контроля блоков памяти, содержавшее информационный регистр, первые вход и выход которого подключены соответственно к первому выходу и к первому входу коммутатор, вторые вход и выход - соответственно . к первому выходу и первому входу блока кодирования - декодирования, а третий вход информационного регистра подключен к первому выходу блока коррекции и к входу блока определения кратности сбоя, блок экстраполяции, первый выход которого подключен к второму входу коммутатора, второй вход - к первому выходу вычислителя, а первый выход к входу блока индикации, преобразователь информации, вход и выход ко торого подключены соответственно к второму выходу и к второму входу блока кодирования-декодирования, третий выход блока кодирования-декодирования подключен к входу блока коррекции, блок управления, отличающееся тем, что, с цепью повышения точности контроля, оно содержит накопитель, первые вход и выход которого подключены соответственно к третьему выходу и к второму входу коммутатора, второй выход - к третьему входу блока экстраполяции, а третий выход накопителя подключен к первому входу вычислителя, блок регистров, первый выход которого подключен к четвертому входу блока экстраполяции и к второму входу Накопителя, второй вход - к второму входу вычислителя, а третий

0 выход блока регистров подключен к третьему входу, накопителя, дополнительный коммутатор, первый вход которого подключен к выходу блока определения кратности сбоев, второй

5 вход - к второму выходу блока коррекции, третий вход - к второму выходу блока экстраполяции, а четвертый вход дополнительного коммутатора подключен к второму выходу вычислиQ теля, первый выход дополнительного коммутатора подключен к входам блока регистров, блок о.пределения адре,.са сбоя, выход которого подключен к пятому входу дополнительного коммутаг- тора, и блок синхронизации, выход которого подключен к шестому входу дополнительного коммутатора.

.Источники информации, .принятЕде во внимание при экспертизе

1.Авторское свидетельство СССР по заявке , 2675108/18-24,

кл. G 11 С 29/00, 1980.

2.Авторское свидетельство СССР . 431558, кл. G 11 С,29/00, 1973

(прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ контроля магнитных накопителей | 1982 |

|

SU1095232A1 |

| Устройство для контроля запоминающих устройств | 1978 |

|

SU769638A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243032A1 |

| Запоминающее устройство | 1981 |

|

SU1014042A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1249590A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1048520A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1988 |

|

SU1566414A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU942163A2 |

| Запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1374286A1 |

Авторы

Даты

1982-09-23—Публикация

1980-03-19—Подача