(А

С

Изобретение относится к вычислительной технике и может быть использовано в основных запоминающих устройствах цифровых ЭВМ и специализированных вычислителей.

Цель изобретения - повышение надежности устройства.

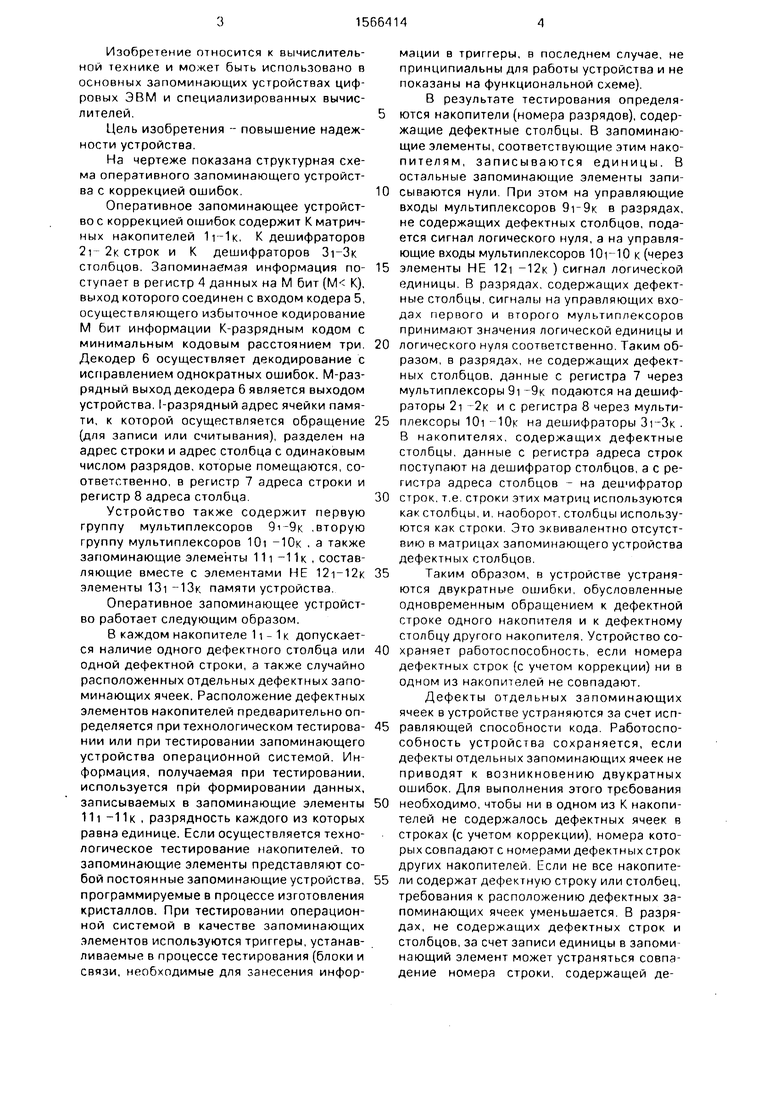

На чертеже показана структурная схема оперативного запоминающего устройства с коррекцией ошибок

Оперативное запоминающее устройство с коррекцией ошибок содержит К матричных накопителей , К дешифраторов 2i-2к строк и К дешифраторов Зт-Зк столбцов. Запоминаемая информация поступает в регистр 4 данных на М бит (М К), выход которого соединен с входом кодера 5, осуществляющего избыточное кодирование М бит информации К-разрядным кодом с минимальным кодовым расстоянием три Декодер 6 осуществляет декодирование с исправлением однократных ошибок. М-раз- рядный выход декодера 6 является выходом устройства. 1-разрядный адрес ячейки памяти, к которой осуществляется обращение (для записи или считывания), разделен на адрес строки и адрес столбца с одинаковым числом разрядов, которые помещаются, соответственно, в регистр 7 адреса строки и регистр 8 адреса столбца

Устройство также содержит первую группу мультиплексоров 9i-9 .вторую группу мультиплексоров 10i -10к , а также запоминающие элементы 111 -11 к , составляющие вместе с элементами НЕ 12-|-12к элементы 13т -13к памяти устройства

Оперативное запоминающее устройство работает следующим образом.

В каждом накопителе 11 - 1 к допускается наличие одного дефектного столбца или одной дефектной строки, а также случайно расположенных отдельных дефектных запоминающих ячеек. Расположение дефектных элементов накопителей предварительно определяется при технологическом тестировании или при тестировании запоминающего устройства операционной системой. Информация, получаемая при тестировании, используется при формировании данных, записываемых в запоминающие элементы 11i -11 к , разрядность каждого из которых равна единице. Если осуществляется технологическое тестирование накопителей, то запоминающие элементы представляют собой постоянные запоминающие устройства, программируемые в процессе изготовления кристаллов. При тестировании операционной системой в качестве запоминающих элементов используются триггеры, устанавливаемые в процессе тестирования (блоки и связи, необходимые для занесения информации в триггеры, в последнем случае, не принципиальны для работы устройства и не показаны на функциональной схеме)

В результате тестирования определяются накопители (номера разрядов), содержащие дефектные столбцы. В запоминающие элементы, соответствующие этим нако- пителям, записываются единицы. В остальные запоминающие элементы эапи0 сываются нули При этом на управляющие входы мультиплексоров 9г9к в разрядах, не содержащих дефектных столбцов, подается сигнал логического нуля, а на управляющие входы мультиплексоров 1СН-10 к (через

5 элементы НЕ 12i -12к ) сигнал логической единицы В разрядах, содержащих дефектные столбцы, сигналы на управляющих входах первого и второго мультиплексоров принимают значения логической единицы и

0 логического нуля соответственно Таким образом, в разрядах, не содержащих дефектных столбцов, данные с регистра 7 через мультиплексоры 9i -9к подаются на дешифраторы 2i -2« и с регистра 8 через мульти5 плексоры 10i-10к на дешифраторы 31-Зк . В накопителях, содержащих дефектные столбцы, данные с регистра адреса строк поступают на дешифратор столбцов, а с регистра адреса столбцов - на дешифратор

0 строк, т е строки этих матриц используются как столбцы, и наоборот, столбцы используются как строки Это эквивалентно отсутствию в матрицах запоминающего устройства дефектных столбцов

5Таким образом, в устройстве устраняются двукратные ошибки, обусловленные одновременным обращением к дефектной строке одного накопителя и к дефектному столбцу другого накопителя. Устройство со0 храняет работоспособность, если номера дефектных строк (с учетом коррекции) ни в одном из накопителей не совпадают.

Дефекты отдельных запоминающих ячеек в устройстве устраняются за счет исп5 равляющей способности кода Работоспособность устройства сохраняется, если дефекты отдельных запоминающих ячеек не приводят к возникновению двукратных ошибок. Для выполнения этого требования

0 необходимо, чтобы ни в одном из К накопителей не содержалось дефектных ячеек в строках (с учетом коррекции), номера которых совпадают с номерами дефектных строк других накопителей Если не все накопите5 ли содержат дефектную строку или столбец, требования к расположению дефектных запоминающих ячеек уменьшается В разрядах, не содержащих дефектных строк и столбцов, за счет записи единицы в запоми нающий элемент может устраняться совпадение номера строки, содержащей дефектную запоминающую ячейку, в одном разряде с номером дефектной строки в другом разряде. Аналогично преобразование адресов может использоваться для устранения двукратных ошибок, вызванных дефек- тами запоминающих ячеек с одинаковыми адресами.

Дефекты дешифраторов столбцов и дешифраторов строк в устройстве могут быть идентифицированы с дефектами столбца или строки и устраняются аналогичным образом.

В устройстве исправляются также случайные сбои, вызванные, например, разрядом конденсаторов динамических матриц памяти при воздействии альфа-частиц, если они не приводят к возникновению двукратных ошибок.

Формула изобретения

Оперативное запоминающее устройст- во с коррекцией ошибок, содержащее матричные накопители, дешифраторы строк, дешифраторы столбцов, кодер и декодер, причем вход выборки по строке и вход выборки по столбцу каждого матричного нако- пителя подключены, соответственно, к выходам соответствующих дешифратора

строк и дешифратора столбцов, информационные входы матричных накопителей подключены к соответствующим выходам кодера, входы которого являются информационными входами устройства, информационные выходы матричных накопителей соединены с соответствующими входами декодера, выходы которого являются информационными выходами устройства, отличающееся тем. что, с целью повышения надежности устройства, в него введены первая и вторая группы мультиплексоров и элементы памяти, причем прямой и инверсный -выходы каждого элемента памяти подключены к управляющим входам соответствующих мультиплексоров первой и второй групп, выходы мультиплексоров первой и второй групп подключены к входам соответствующих дешифраторов строк и дешифраторов столбцов, первые информационные входы мультиплексоров первой и второй групп объединены поразрядно и являются первым адресным входом устройства, вторые информационные входы мультиплексоров первой и второй групп объединены поразрядно и являются вторым адресным входом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1539844A1 |

| Устройство памяти на телевизионный кадр | 1987 |

|

SU1559430A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU864339A1 |

| Запоминающее устройство матричного типаС САМОКОНТРОлЕМ | 1979 |

|

SU849309A1 |

| Запоминающее устройство с самоконтролем | 1987 |

|

SU1432613A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU877614A1 |

| Устройство для преобразования Хо изображения | 1990 |

|

SU1785004A1 |

| Запоминающее устройство с исправлением ошибок | 1984 |

|

SU1226536A1 |

| Устройство декодирования для системы передачи цифровых сигналов | 1985 |

|

SU1305884A1 |

| Запоминающее устройство с резервированием | 1989 |

|

SU1674252A1 |

Изобретение относится к вычислительной технике и может быть использовано в основных запоминающих устройствах цифровых ЭВМ и специализированных вычислителей. Цель изобретения - повышение надежности устройства. Устройство содержит матричные накопители 1, дешифраторы 2 строк, дешифраторы 3 столбцов, регистр 4 данных, кодер 5, декодер 6, регистр 7 адреса строк, регистр 8 адреса столбцов, мультиплексоры 9 и 10, запоминающие элементы 11 и элементы НЕ 12. В устройстве осуществляется "поворот" матричных накопителей (для этого накопители должны быть квадратными), содержащих, например, дефектные столбцы, так, что устройство содержит, например, только дефектные строки. 1 ил.

| Electronics, 1982, v | |||

| Устройство двукратного усилителя с катодными лампами | 1920 |

|

SU55A1 |

| 539-544 | |||

| Зарубежная электронная техника | |||

| Сборник обзоров, 1985, № 10, с | |||

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

Авторы

Даты

1990-05-23—Публикация

1988-07-06—Подача