жит сумматор, вычислитель средней кратности сбоев, вычислитель дисперсии кратности сбоев, счетчик сбоев и счетчик разрядов. Одни из входов сумматора подключены соответственно к выходам вычислителя средней кратности сбоев и вычислителя дисперсии кратности сбоев, одни из входов которых соединены соответственно с выходами счетчика сбоев и счетчика разрядов. Другие входы сумматора, вычислителя средней кратности сбоев и вычислителя дисиерсии кратности сбоев, входы счетчика сбоев и счетчика разрядов подключены ко входам узла определения текущих значений нрогнознруемого иараметра отказа, выход которого соединен с выходом сумматора.

Узел определения прогнозируемого параметра отказа целесообразно выполнить в виде узла, который содержит экстраполятор и регистр, входы которого подключены к выходу экстраполятора и одним из входов узла определения ирогнозируемого параметра отказа, другой вход и выход которого соединеиы соответственно с первым входом экстраполятора и первым выходом регистра, второй выход которого соединен со вторым входом экстраполятора.

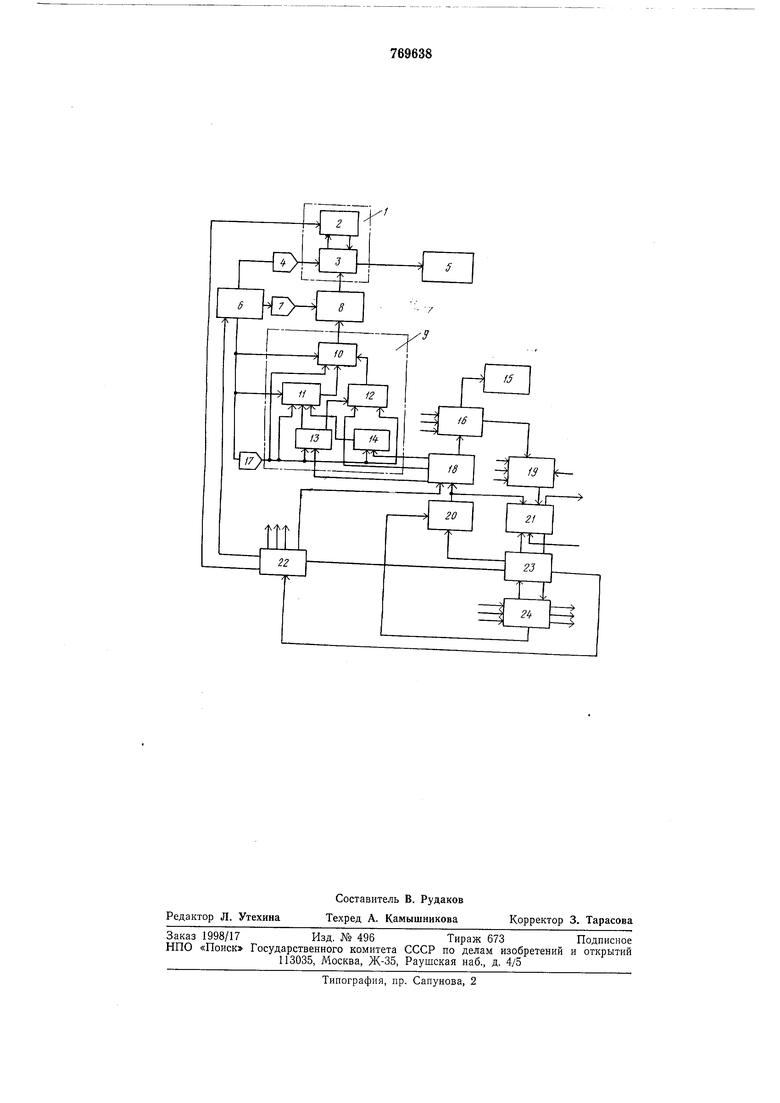

Г1а чертеже изображена структуриая схема предложенного устройства.

Устройство содержит узел определения прогнозируемого параметра 1, состоящий из экстраиолятора 2 и регистра 3, служащего для фиксации значений прогнозируемого параметра, первый элемент задержки 4, дополнительный блок индикации 5, блок местного управления 6, второй элемент задержки 7, расиределитель сигналов 8, узел онределення текущих значений прогнозируемого параметра отказа 9, в состав которого входят сумматор 10, вычислитель средней кратности сбоев 11, вычислитель дисперсии кратности сбоев 12, счетчик сбоев 13 и счетчик разрядов 14, служащий для иодсчета числа искажеииых разрядов, блок индикации 15, узел регистрации распределений кратности сбоев 16, третий элемент задержки 17, узел определения кратности сбоев 18, блок ключевых схем 19, узел коррекции 20, входной регистр 21, блок управления 22, узел кодирования - декодирования 23 и узел растяжения - сжатия кодированных слов 24.

Входы узла 1 подключены соответственно к одному из выходов блока 22 и выходу элемента задергкки 4, а выход - ко входу блока 5. Вход блока 6 соединен с другим выходом блока 22, а выходы - соответственно со входами элементов задерл ки 7 и 8 и одними из входов узла 9, другие входы которого иодключены соответственно к выходам элемента задержки 17 и узла 18, а выход соединен с одним из входов расиределителя 8, другой вход которого подключен к выходу элемента задержки 7.

Одии из входов сумматора 10 подключены соответственно к выходам вычислителей И и 12, одни из входов которых соединены соответственно с выходами счетчиков 13 и 14. Другие входы сумматора 10, вычислителей 11 и 12 и входы счетчиков 13 и 14 подключены ко входам узла 9, выход которого соединен с выходом сумматора 10. Входы регистра 3 иодключены к выходу

экстраполятора 2 и одним из входов узла 1, другой вход и выход которого соединены соответственно с первым входом экстраполятора 2 и первым выходом регнстра 3, второй выход которого соединен со вторым входом экстраполятора 2.

Устройство работает следующи.м образом.

В режиме записи поступающие из ЦВМ иа входной регистр 21 слова кодируются в

ysJte кодироваиия - декодирования 23, растягиваются в узле 24 и выдаются для записи в ВЗУ. Параметры растяжения - сжатия выбраны из условия расщепления групповых сбоев кратности до Л включительно

иа одиночные, причем устанавливают величину К, соответствующую границе нормальной работы тракта каждого из ВЗУ. На блоке управления 22 устанавливается требуемый интервал времени, через который с

блока 6 иоступает сигнал обращеиия к узлу 1, соответствующий нулевому состоянию всех счетчиков и регистров.

Этот иитервал соответствует периоду отсчета прогнозируемого параметра.

В режиме воспроизведения растянутые кодовые слова поступают в узел растяжения - сжатия 24, где онн сжимаются к исходному (до записи) виду и оттуда иоступают в узел кодироваиия - декодирования

23. Каждое декодированное слово поступает затем ,на входной регистр 21, где оно корректируется, если в нем была одиночная ошибка, с помощью узла коррекции 20. Первый сигнал ошибки узла 20 при воспроизведении является сигиалом начала цикла измерения кратности сбоя, по окончании которого из узла определения кратности сбоев 18 результат одиого измерения поступает в узел 16. Результат измерения переписывается также в узел 9. За интервал времени, отсчитываемый блоком 6, происходит накопление информации на счетчиках 13 и 14. По истечении этого промежутка времени но сигналу с блока 6 данные со

счетчиков 13 и 14 поступают на вычислитель 11, который вычисляет среднюю кратность сбоев, и данные со счетчика 13 поступают иа вычислитель 12, который вычисляет разброс кратпости сбоев. Данные с

вычислителей 11 и 12 за интервал времени, установленный на блоке 22, на сумматор 10. Далее текущее значение прогнозируемого параметра с выхода сумматора 10 пересылается через распределитель 8 на

регистр 3. После измерения, начиная с заданного, с помощью элемента задержки 4 и блока управления 22 проводится цикл прогнозирования момента достижения прогнозируемым параметром границы К.

С блока 6 подается сигнал на элемент задержки 17, и содержимое всех элементов узла 9 приводится в первоначальное состояние. С экстраполятора 2 точечные значения прогнозируемого параметра переносятся в узел 3 фиксации значений прогнозируемого параметра, после чего эти данные поступают на дополнительный блок индикации 5, где оператор может считывать значение времени нормальной работы трактов записи - воспроизведения ВЗУ.

Таким образом, приближенная визуальная оценка оператором моментов отказов трактов ВЗУ заменяется точной и оперативной автоматизированной процедурой прогнозирования. Это обеспечивает высокую точность предсказания отказов трактов ЗУ и снижение времени их простоев, оперативность оценки состояния тракта в процессе его функционирования и возможность оперативного принятия решений но обеспечению выполнения текущих задач. Кроме того, существенно облегчается и упрощается работа оператора.

Формула изобретения

1. Устройство для контроля запоминающих устройств по авт. св. № 431558, отличающееся тем, что, с целью повыщения точности и онеративности контроля, оно содержит узел определения прогнозируемого параметра отказа, узел определения текущих значений прогнозируемого параметра отказа, распределитель сигналов, блок местного управления, дополнительный блок индикации и элементы задержки, причем входы узла определения прогнозируемого параметра отказа подключены соответственно к одному из входов блока управления и выходу первого элемента задержки и распределителя сигналов, а выход - ко входу дополнительного блока индикации, вход блока местного управления соединен с другим выходом блока управления, а выходы - соответственно со входами второго и третьего элементов задержки и одними из входов узла определения текущих значений прогнозируемого параметра отказа, другие входы которого подключены соответственно к выходам третьего элемента задержки и узла определения кратности сбоев, а выход соединен с одним из входов распределителя сигналов, другой вход которого подключен к выходу второго элемента задержки.

2.Устройство по п. 1, отличающееся тем, что узел определения текущих значеНИИ прогнозируемого параметра отказа содержит сумматор, вычислитель средней кратности сбоев, вычислитель дисперсии кратности сбоев, счетчик сбоев и счетчик разрядов, причем одни из входов сумматора подключены соответственно к выходам вычислителя средней кратности сбоев и вычислителя дисперсии кратности сбоев, один из входов которых соединены соответственно с выходами счетчика сбоев и счетчика

разрядов, другие входы сумматора, вычислителя средней кратности сбоев и вычислителя диснерсии кратности сбоев, входы счетчика сбоев и счетчика разрядов подключены ко входам узла определения текущих значений прогнозируемого параметра отказа, выход которого соедппен с выходом сумматора.

3.Устройство по пп. 1 и 2, отличающееся тем, что узел определения прогнозируемого параметра отказа содержит экстр аполятор и регистр, входы которого подключены к выходу экстраполятора и одннм из входов узла определения прогнозируемого параметра отказа, другой вход и выход

которого соединены соответственно с первым входом экстраполятора и первым выходом регистра, второй выход которого соединен со вторым входом экстраполятора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 431558, кл. G ПС 29/00, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков памяти | 1980 |

|

SU960958A1 |

| Устройство для контроля системы автоматической стабилизации параметров | 1986 |

|

SU1374248A1 |

| Устройство для регулирования выдачи топлива | 1982 |

|

SU1043716A1 |

| Устройство прогнозирования работоспособности радиоэлектронной аппаратуры | 1987 |

|

SU1422196A2 |

| Устройство для контроля знаний обучаемых | 1981 |

|

SU1012317A1 |

| Устройство для тестового контроля процессора | 1986 |

|

SU1408438A1 |

| Низкоскоростной дельта-модулятор | 1984 |

|

SU1203706A1 |

| Устройство дл прогнозирования неисправностей радиоэлектронной аппаратуры | 1978 |

|

SU742958A1 |

| Устройство цикловой синхронизации для внешней памяти | 1983 |

|

SU1092510A1 |

| Устройство для определения показателей надежности объектов | 1983 |

|

SU1170466A1 |

Авторы

Даты

1980-10-07—Публикация

1978-10-18—Подача