Изобретение касается вычислитель ной техники и автоматики и быть использовано для счета импульсов . Известен счетчик, содержащий груп пы разрядов , тактовые входы соединены с входом счетчика, а выход переноса каждой группы соединен с тактовыми входами разрядов .следук)uoix групп Е1 . Недостатком этого счетчика является относительно .„низкое быстро. действие. Известен счетчик содержащий групm разрядов, каждый из которых содержит первый и второй..ког мутационные триггеры и триггер гТамяти, тактовые входы всех коммутационных триггеров соединены с входом счетчик и выходами переноса предыдущих групп разрешающие входы всех ксммутацион ных триггеров разрядов данной группы разрядов, креме последнего разря да той же группы, и разрешающий вход niepBoro коммутационного триггера последнего разряда данной груп пы разрядов соединены с выходами пе реноса каждого разряда, предшествую щего данному в той же группе разрядов 2. Недостатком этого счетчика является относительно низкое быстродействие. Это связано с необходимостью использования связи каж,цого разряда со всеми последующими, что приводит к большой нагрузке на элементы и снижению быстродействия. Цель изобретения - повышение быстродействия. Для этого -в счетчик, содержащий группы разрядов, каждый из которых содержит первый и второй коммутационные триггеры и триггер памяти, тактовые входы всех коммутационны триггеров соединены с входом счетчика и вы: одами переноса предыдущих групп, разрешающие входы всех коммутационных триггеров разрядов данной группы разрядов, кроме последнего разряда той же группы, и разрешающий вход первого коммутационного триггера последнего разряда данной группы разряд&в соединены с выходами переноса каждого разряда, предшествующего данному в этой группе разрядов, дополнительные входы первого коммутационного триггера

последнего разряда данноЯ группы разрядов соединены с нулевыми и единич ными выходами соответственно первого коммутационного триггера и триггера памяти всех разрядов кроме последнего в той же группе разРядов, а выход переноса последнего разряда данной группы разрядов соединен с выходом переноса данной группа разрядов.

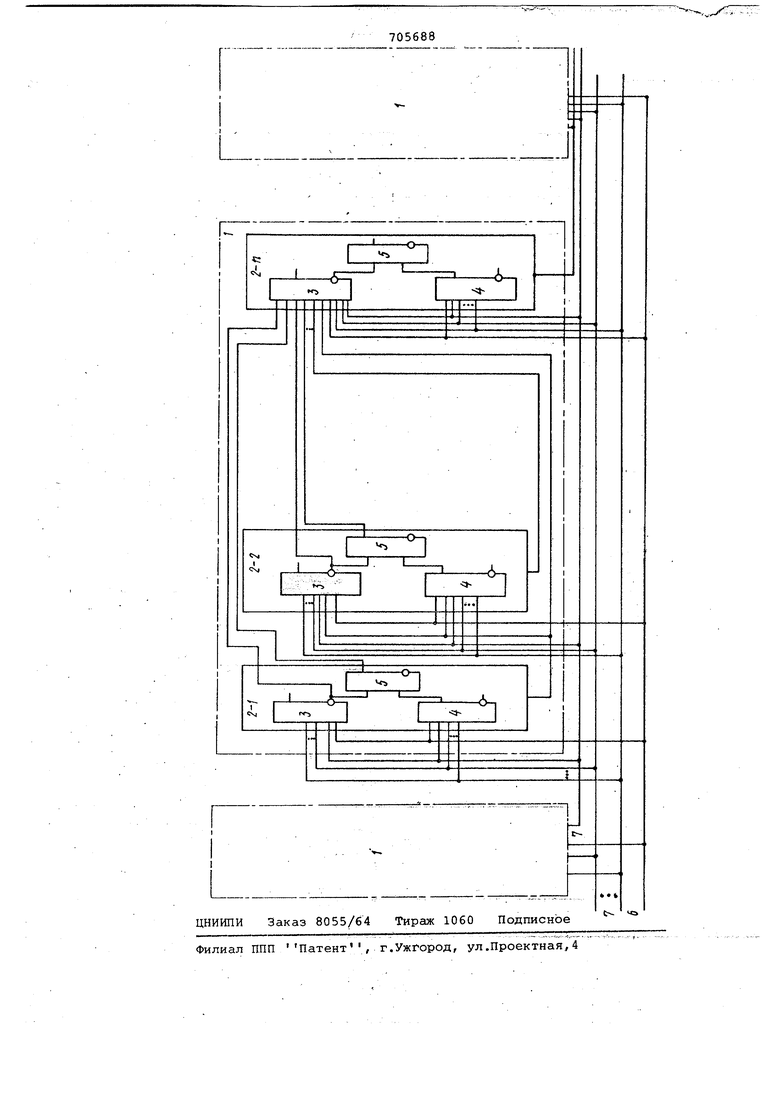

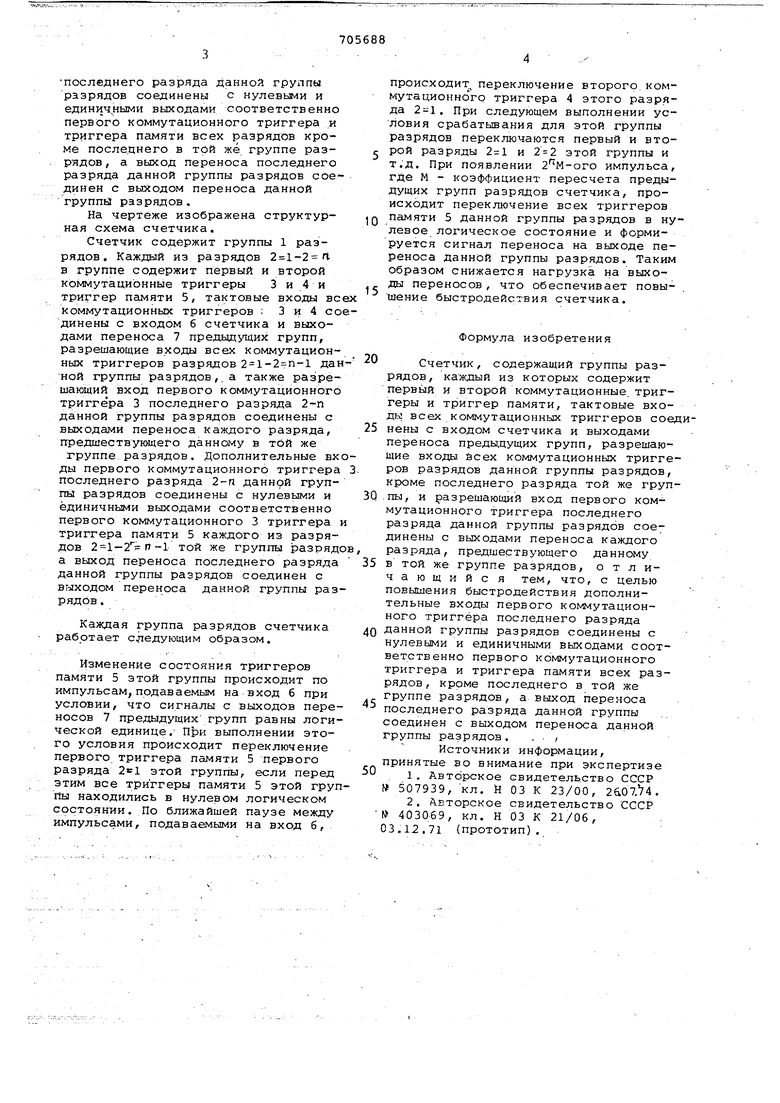

На чертеже изображена структурная схема счетчика.

Счетчик содержит группы 1 разрядов. Каждый из разрядов в группе содержит первый и второй коммутационные триггеры 3 и 4 и триггер памяти 5, тактовые входы вс коммутационных триггеров : 3 и 4 содинены с входом б счетчика и выходами переноса 7 предьщущих групп, разрешающие входы всех коммутационных триггеров разрядов 2 1-2 п-1 дан НОЙ группы разрядов,, а также разрешающий вход первого коммутационного триггера 3 последнего разряда 2-п данной группы разрядов соединены с выходами переноса каждого разряда, предшествующего данному в той же группе,разрядов. Дополнительные вхды первого коммутационного триггера последнего разряда 2-п данной группы разрядов соединены с нулевыми и единичными выходами соответственно первого коммутационного 3 триггера триггера памяти 5 каждого из разрядов 2 1-2 той же группы разряд а выход переноса последнего разряда данной группы разрядов соединен с выходом переноса данной группы разрядов .

Каждая группа разрядов счетчика работает следующим образом.

Изменение состояния триггеров памяти 5 этой группы происходит по импульсам,подаваемым на вход б при

условии, что сигналы с выходов пере

носов 7 предыдущих групп равны логической единице. При выполнении этого условия происходит переключение первого, триггера памяти 5 первого разряда этой группы, если перед этим все триггеры памяти 5 этой группы находились в нулевом логическом состоянии. По ближайшей паузе между импульсами, подаваемыми на вход б,

происходит, переключение второго, коммутационного триггера 4 этого разряда 2-1. При следующем выполнении условия срабатывания для этой группы разрядов переключаются первый и второй разряды и этой группы и т.д. При появлении 2 М-ого импульса, гДе М - коэффициент пересчета предыдущих групп разрядов счетчика, происходит переключение всех триггеров памяти 5 данной группы разрядов в нулевое логическое состояние и формируется сигнал переноса на выходе переноса данной группы разрядов. Таким образом снижается нагрузка на выходы переносов, что обеспечивает повышение быстродействия счетчика.

Формула изобретения

Счетчик, содержащий группы разрядов, каждый из которых содержит первый и второй коммутационные, триггеры и триггер памяти, тактовые входы всех коммутационных триггеров соенены с входом счетчика и выходами переноса преды,цущих групп, разрешающие входы йсех коммутационных триггеров разрядов данной группы разрядов, кроме последнего разряда той же груп,пы, и разрешающий вход первого коммутационного триггера последнего разряда данной группы разрядов соединены с выходами переноса каждого разряда, предшествующего данному в той же группе разрядов, отличающийся тем, что, с целью повышения быстродействия дополнительные входы Первого коммутационного триггера последнего разряда данной группы разрядов соединены с нулевыми и единичными выходами соответственно первого коммутационного триггера и триггера памяти всех разрядов , кроме последнего в той же группе разрядов, а выход переноса последнего разряда данной группы соединен с выходом переноса данной группы разрядов. . . ,

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 507939, кл. Н 03 К 23/00, 2U07.V4.

2,Авторское свидетельство СССР № 403069, кл. Н 03 К 21/06, 03,12.71 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетчик | 1981 |

|

SU961154A1 |

| Реверсивный счетчик | 1981 |

|

SU1003356A1 |

| Параллельный счетчик | 1981 |

|

SU999168A1 |

| Многоканальное устройство управления резервированной системой | 1979 |

|

SU866558A2 |

| Счетчик | 1985 |

|

SU1267614A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1444770A1 |

| Многоразрядный счетчик с параллельным переносом | 1976 |

|

SU788388A1 |

| Счетчик с параллельным переносом | 1974 |

|

SU507943A1 |

| Генератор испытательных кодов | 1986 |

|

SU1405058A1 |

| Формирователь тестов | 1985 |

|

SU1260963A1 |

Авторы

Даты

1979-12-25—Публикация

1977-01-07—Подача