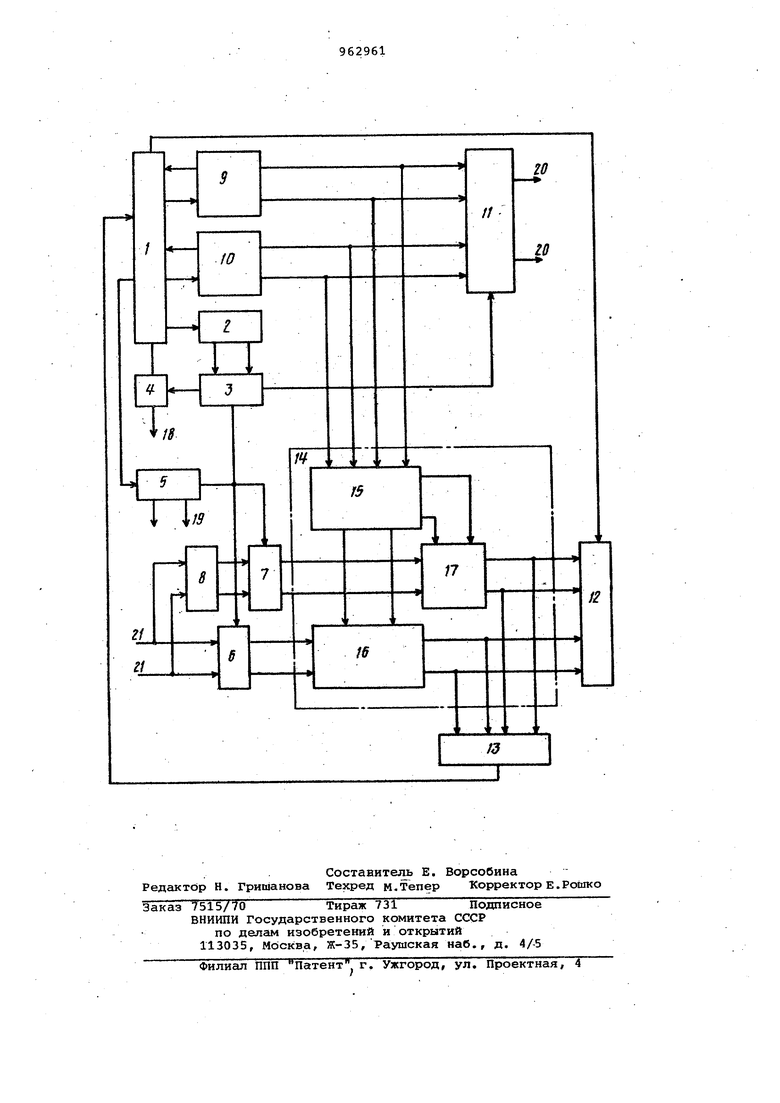

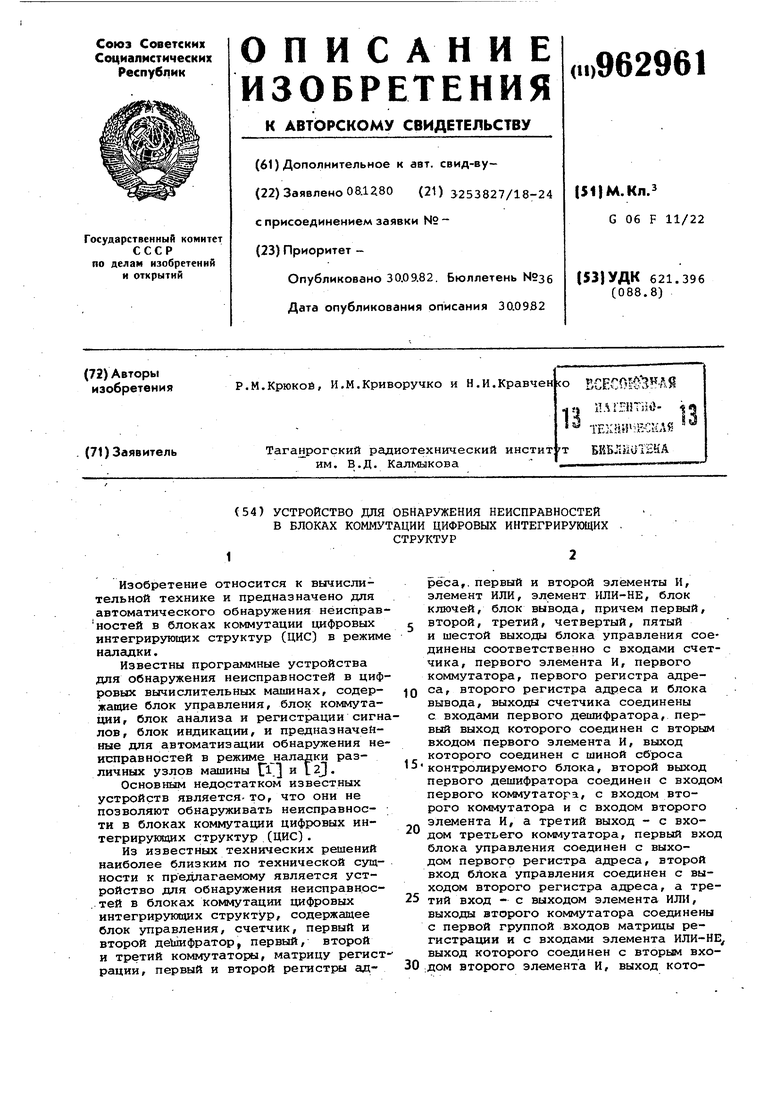

цэого соединен с входом блока ключей, .рервая группа выходов первого регист ра адреса соединена с первой группой входов третьего коммутатора и с первой группой входов второго дешифрато ра, а первая группа выходов второго регистра адреса соединена с второй группой входов третьего коммутатора и второй группой входов второго дешифратора, первая группа выходов которого соединена с второй группой входов матрицы регистрации, а вторая группа выходов - .с группой входо блока ключей, первая группа входов блока вывода соединена с выходами матрицы регистрации, а вторая группа входов - с выходами блока ключей, первый вход элемента ИЛИ соединен с выходом второго элемента И, а остальные входы - с выходами.матри цы регистрации, выходы первого и третьего коммутаторов соединены соответственно с информационными и управляющими шинами контролируемого блока, а входы второго коммутатора соединены с контрольными точками кон ролируемого блока З. Однако устройство обладает недостаточной эффективностью обнаружения неисправностей, так как оно не позволяет обнаруживать неисправности типа несрабатывание контролируемого коммутирующего элемента при одновременном ложном срабатывании произвольных коммутирующих элементов. Цель изобретения - расширение фун циональных возможностей и повышение точности устройства. Поставленная цель достигается тем что в устройство для обнаружения неисправностей в -блоках коммутации циф ровых интегрирующих структур, содержащее блок управления, первый и второй выходы которого подключены ко входам соответственно первого и второго регистров адреса, первые выходы которых соединены соответственно с первым и вторым входом блока управ ления, третий выход которого подключен через последовательно соединенные счетчики первый дешифратор к пе вым входам первого и второго коммутаторов, четвертый выход - к первому входу элемента И, соединенного вторы входом с вторым выходом первого дешифратора, пятый выход - к второму входу первого коммутатора, шестой вы ход - к первому входу блока вывода, соединенного вторыми входами с выход ми первой матрицы регистрации и с пе выми входами элемента ИЛИ, выход которого подключен к третьему входу бл ка управления, второй выход первого дешифратора соединен с первым входом третьего коммутатора, вторые вхо ды которого подключены к выходам первого и второго регистров адреса и к входам второго дешифратора , nepвые выходы которого подключены к первым входам первой матрицы регистрации, вторыми входами соединенной с выходами второго коммутатора, введены последовательно соединенные блок инверторов, четвертый-коммутатор и вторая матрица регистрации, вторые входы которой подключены к вторым выходам второго дешифратора, а выходы - к вторым входам элемента ИЛИ и к третьим входам блока вывода, а входы блока инверторов соединены с вторыми входами- второго коммутатора. На чертеже дана электрическая схема устройства для обнаружения неисправностей. В состав устройства для обнаружения неисправностей в блоках коммутации ЦИС входят блок 1 управления, ;счетчик 2, первый дешифратор 3, эле мент И 4, первый коммутатор 5, второй коммутатор 6, четвертый коммутатор 7, блок инверторов 8, первый регистр 9 адреса, второй регистр 10 адреса, третий коммутатор 11, блок 12 вывода, элемент ИЛИ 13, блок 14 анализа и регистрации сигналов, содержащий дешифратор 15, первую матрицу 16 регистрации, вторую матрицу 17 регистрации,.шина 18 сброса контролируемого блока, информацион- . ные шины 19 контролируемого блока, управляющие шины 20 контролируемого блока, контрольные точки 21 контролируемого блока. Контролируемый блок - блок коммутации ЦИС - представляет собой набор коммутирующих элементов, позволяющих устанавлива.ть связь любого выхода из N решакяцих блоков ЦИС с любым из d входов каждого из N решающих блоков. Каждый коммутирующий элемент представляет собой элемент памяти (триггер) с входным клапаном и элементом и, управляемым этим триггером. Коммутация решающих блоков осуществляется в соответствии с матрицей коммутации, определяемой при программировании задачи. При .этом выбор соответствующего элемента производится выбором определяемых матрицей коммутации соответствукадего адреса строки и адреса столбца коммутирукндих элементов. Эти адреса по управляющим шинам поступают на входные клапаны коммутирующих элементов и устанавливают триггер выбираемого коммутирукяцего элемента в единичное. состояние. Информационные же сигналы поступают иа входы элементов И, вторые входы которых управляются этими триггерами. Основными неисправностями блока коммутации ЦИС являются несрабатывание выбираемого коммутируемого элемента при отсутствии ложного срабатывания произвольных коммутирукяцих элементов, несрабатывание выбираемого коммутирующего элемента при наличии одновременно ложно1-о срабатывания произвольных коммутирующих элементов и ложное срабатывание произвольных коммутирующих элементов при отсутствии несрабаты вания выбираемого коммутирующего элемента. Предлагаемое устройство позволит автоматически обнаруживать эти неисправности и указывать номер неисправного коммутирующего элемента. Устройство работает следующим об разом. Перед началом работы блок 1 прои водит установку в исходное.состояни счетчика 2, первого регистра 9 и вт рого регистра 10, Поиск неисправностей в контролируемом блоке коммутации ЦИС осущест вляется последовательным выбором ком мутируквдих элементов и проверкой их неисправности. Проверка исправности каждого коммутирующего элемента осуществляется за цикл, состоящий из трех тактов: установка в исходное (Состояние блока коммутации/ выбор контролируемого коммутирующего элеiMeHTaJ проверка его исправности. После выработки блоком 1 сигнала Пуск начинается первый цикл проверка неисправности первого коммутирующего элемента, соответствующего первой строке первого столбца матрицы коммутации. При этом в первом такте этого цикла блок 1 заноси единицы в первые разряды регистров 9 и 10 и одновременно подачей сигна ла на счетчик 2 устанавливает его в единичное состояние. В результате этого дешифратор 3 открывает элемент И 4 и сигнал установки в исходное состояние поступает через элемент И 4 на шину 18 сброса контролируемого блока и устанавливает его в исходное состояние. Во втором такте первого цикла счетчик 2 перебраюывается в состояние, равное двум. При этом децифратор 3 подает управляющий сигнал ia коммутатор 11 и в результате с выходов регистров 9 и ГО сигналы пос тупают через коммутатор 11 на управляющие шины 20 контролируемого бло- ;са, а так как в регистрах 9 и 10 /записаны единицы в первых разрядах то происходит выбор первого коммутирующего элемента. В третьем такте первого цикла счетчик 2 перебрасывается в состояние, равное трем, а дешифратор 3 подает разрешающий сигнал на коммутаторы 5-7. В результате блок 1 подает сигналы через коммутатор 5 на все информационные шины 19 контролируемого блока, а коммутато|ры б и 7 снимают сигналы соответстве но с контрольных точек 21 и их инвер ные значения с выходов блока инверторов 8 и Подают их на входы блока 14 анализа и регистрации сигналов. Этот блок производит выявление неисправностей. В случае отсутствия неисправностей в первом коммутирующем элементе блок 1 начинает второй цикл проверки, в течение которого проверяется второй ко иутирующий элемент, соответствующий вт;орой строчке первого столбца матрицы коммутации. При этом в первом такте второго цикла блок 1 сдвигает на один разряд единицу в регистре 9 и устанавливает счетчик 2 в единичное состояние, а далее проверка исправности второго коммутирующего элемента первого столбца осуществляется аналогично проверке исправности первого коммутирующего элемента. Когда единица в регистре 9 сдвинется в последний разряд и будет проверен последний коммутирукядий элемент первого столбца, то в первом такте следующего цикла проверки эта единица переза пишется в первый разряд этого регистра и одновременно в регистре 10 единица сдвинется сигналом из блока 1 во второй разряд и аналогично будут проверены все коммутирующие элементы, соответствующие второму столбцу матрицы коммутации. В случае, если в каком-то.коммутирукядем элементе блока кс 1мутации ЦИС возникла неисправность, то при выборе этого коммутирующего элемента в третьем такте его проверки эта неисправность буЯет обнаружена блоком 14. При этом, если возникла неисправность типа несрабатывание контролируемого коммутирующего элемента при отсутствии ложного срабатывания произвольных коммутирующих элементов, то обнаружение этой неисправности производится в матрице 17 бло+i ка 14, состоящей из двухвходовых элементов И, на первые входвл которых поступешт CHrHcLnK с выходов коммутатора 7, а входы соединены с единичными выходами дешифратора 15, который расшифровывает номер контролируемого коммутирующего элемента и подачей сигнала «а элемент И, соответствующий контролируемому коммутируняцему элементу, подготавливает этот элемент И к прохождению сигнала неисправности. Тогда в случае несрабатывания контролируемого коммутирующего элемента при отсутствии ложного срабатывания произвольных коммутирующих элементов на всех контрольных точках 21 контролируемого блока коммутации ЦИС будут нулевые сигналы и в результате на всех выходах блока инверторов 8 будут единичные сигналы, которые пройдут через коммутатор 7 и поступят через группу входов матрицы 17 блока 14 на первые входы двухвходовых элементов И этой матрицы, в том числе и на элемент И, который соответствует кoнтpoлиpyeмo : ког мутирующему элементу и уже подго товлен к прохождению сигнала неисправности. В результате сигнал неисправности пройдет через этот элеиент И матрицы 17 и поступит в блок 12 вывода, где произойдет индикация номера неисправного коммутирующего элемента контролируемого блока коммутации ЦИС. Одновременно сигнал о неисправности контролируемого коммутирующего элемента с выхода соответствующего элемента И матрицы, 17 поступает через элемент ИЛИ 13 в блок 1 управления. Если же возникла неисправность- типа ложное срабатывание коммутирующих элементов при отсутствии несрабатывания контролируемого коммутирующего элемента, то обнаружение этой неисправности производится в матрице 16 блока, 14, состоящей также из двухвхо довых элементов И, на первые входы которых поступают сигналы с выходов коммутатсЗра 6, а на вторые входы инверсные выходы дешифратора 15 бло-ка 14, которые подготовят к пр9хождению сигналов все элементы И матрицы 16 блока 15, кроме одного, соответствующего контролируемом коммутирующему элементу. Тогда в случае ложного срабатывания коммутирующих элементов при отсутствии несрабатывания контролируемого коммутирующего элемента, единичные сигналы, с выходов Неисправных коммутирующих элементов поступают через коммутатор 6и через соответствующие элементы И матрицы 16 блока 14 в блок 12 вывода,- где происходит индикация номеров неисправных коммутирующих элементов контролируемого блока коммутации ЦИС. Одновременно сигналы о неисправности коммутируюпщх элементов с выходов матрицы 16 блока 14, также, как и в предыдущем случае с .выходов матрицы 17, поступают через элемент ИЛИ 13 в блок 1 управ ления. В то же время, так как в этом случае несрабатывание контролируем го коммутирующего элемента отсутству ет, т.е. контролируемый коммутирующи элемент исправен и сработал, то единичный сигнал с выхода этого конт ролируемого коммутирующего элемента поступит на вход блока инверторов 8 и, проинвертировавшись, у.же нулевым сигналом поступит через коммутатор 7в матрицу 17 на первый вход того элемента И этой матрицы, который со ответствует контролируемому коммути рующему элементу. В результате матр ца 17 регистрирует отсутствие неисп ности и на свой выход сигнал о неис правности не выдает. Если же возник неисправность типа несрабатывание контролируемого коммутирующего элемента при одновременном ложном сра тывании произвольных коммутирующих элементов, то обнаружение этой неисправности производится одновременно в первой 16 и второй 17 матрицах блока 14. При этом, обнаружение несрабатывания контролируемого коммутирующего элемента производится матрицей 17 так же,как и при описанном выше первом типе неисправностей, а обнаружение ложного срабатывайия коммути рующих элементов производится матрицей 16 так же, к-ак и при описанном выше втором типе неисправностей. Полученные сигналы неисправностей с выходов -матрицы 16 и матрицы 17 поступают в:блок 12 вывода, где происходит индикация номеров неисправных коммутирующих элементов контролируемого блока коммутации ЦИС. Одновременно сигна.лы о неисправности коммутирующих элементов с выходов матрицы 16 и матрицы 17 поступают через элемент ИЛИ 13 в блок 1 управления. При этом блок 1 управления запрещает переход к следующему циклу проверки, но продолжает подавать сигнешы на счетчик 2, который работает как счетчик по модулю три, в результате чего три такта проверки - установка. в исходное состояние блока коммутации, выбор контролируемого коммутирующего элемента и проверка его исправности - начинают циклически повторяться при. одном и том же контролируемом коммутирунхдем элементе, при котором обнаружена неисправность. После выявления причины неисправности этого коммутирукяцего э.)1емента в внешним осмотром или с помощью осциллографа, входящего в блок 12 вывода, устройство выключается и неисправ locTb уЬтраняется. Затем снова уст эойство .включается и снова производится проверка исправности коммутйруквдих элементов блока коммутации ЦИС, начиная с первого. После окончания проверки исправности последнего коммутирукядего элемента, соответствукяцего последней строчке последнего столбца матрицы коммутации, единицы с последних разрядов регистров 9 и 10 одновременно поступят в блок 1 управления и этот блок выработает сигнал окончания проверки и сигнал исправности контролируемого блока коммутации ЦИС, который поступит на индикацию в блок 12 вывода. Таким образом, предлагаемое устройство наряду с обнаружением неисправностей типа несрабатывание, контролируемого коммутирующего элемента при отсутствии ложного сраба тывания произвольных коммутирующих элементов и ложное срабатывание произвольных коммутирующих элементов обеспечивает также возможность обнаружения неисправностей типа несрабатывание контролируемого коммутирующего элемента при одновременном ложном срабатывании произвольных коммутирующих элементов, что известным устройством не обнаруживалось. Вследствие этого предлагаемое устройство позволяет повысить эффективность обнаружения неисправностей в блоках коммутации ЦИС и сократить время их наладки.

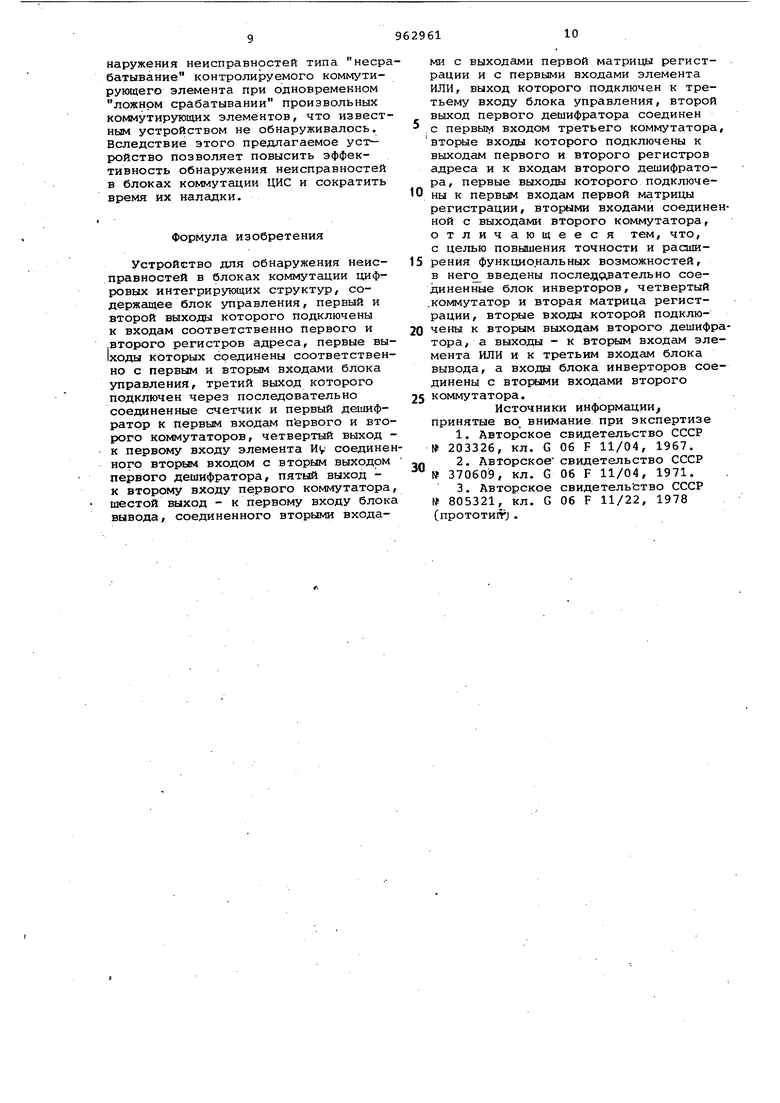

Формул а изобретения

Устройство для обнаружения неисправностей в блоках коммутации цифровых интегрирующих структур, содержащее блок управления, первый и второй выходы которого подключены к входам соответственно первого и второго регистров адреса, первые выводы которых соединены соответственно с первым и вторым входами блока управления, третий выход которого подключен через последовательно соединенные счетчик и первый дешифратор к первым входам первого и второго коммутаторов, четвертый выход к первому входу элемента HV соединенного вторым входом с вторым выходом первого дешифратора, пятый выход к второму входу первого коммутатора шестой выход - к первому входу блока вывода, соединенного вторыми входами с выходами первой матрицы регистрации и с первыми входами элемента ИЛИ, выход которого подключен к третьему входу блока управления, второй выход первого дешифратора соединен с первы1 1 входом третьего коммутатора, вторые входы которого подключены к выходам первого и второго регистров адреса и к входам второго дешифратора, первые выходы которого подключе0ны к первым входам первой матрицы регистрации, вторыми входами соединенной с выходами второго коммутатора, отличающееся тем, что, с целью повышения точности и расши5рения функциональных возможностей, в него введены последд вательно соединенные блок инверторов, четвертый .коммутатор и вторая матрица регистрации, вторые входы которой подключены к вторым выходам второго дешифратора, а выходы - к вторым входс1М элемента ИЛИ и к третьим входам блока вывода, а входы блока инверторов соединены с вторыми входами второго коммутатора.

5

Источники информации принятые во внимание при экспертизе

1.Авторское свидетельство СССР 203326, кл. G 06 F 11/04, 1967.

2.Авторское свидетельство СССР

0 370609, кл. G 06 F 11/04, 1971.

3.Авторское свидетельство СССР № 805321, кл. G 06 F 11/22, 1978 (прототиРП .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения неисправ-НОСТЕй B блОКАХ КОММуТАции цифРОВыХиНТЕгРиРующиХ СТРуКТуР | 1978 |

|

SU805321A1 |

| Устройство для диагностики неисправностей цифровых интеграторов | 1979 |

|

SU877551A1 |

| Устройство для контроля монтажных схем | 1981 |

|

SU1018062A1 |

| Устройство для обнаружения неисправностей в электрическом монтаже | 1973 |

|

SU490123A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для контроля памяти | 1984 |

|

SU1236558A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1982 |

|

SU1108451A1 |

| Устройство для контроля монтажных схем | 1980 |

|

SU920747A1 |

| Устройство для обнаружения и локализации неисправностей цифровых блоков | 1982 |

|

SU1067507A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1278855A1 |

Авторы

Даты

1982-09-30—Публикация

1980-12-08—Подача