ролируемого элемента блока анализа и регистрации сигналов подключены ко входу блока вывода и через дешифратор блока анализа и регистрации сигналов - ко входам матрицы регистрации рабочих сигналов и матрицы регистрации помех блока анализа и регистрации сигналов 2 .

Основным недостатком известного устройства является то, что оно не позволяет обнаруживать неисправност в блоках коммутации ЦИС..В то же время ручной поиск неисправностей в блоках коммутации ЦИС в режиме наладки требует очень много времени, так как необходимо выполнить . очень большое количествйпереборов коммутирующих элементов.

Цель изобретения - расширение функциональных возможностей устройг ства.

Поставленная цель достигается тем, что в устройство для обнаружения неисправностей в блоках коммутации цифровых интегрирующих структур, содержащее блок управления, подключенный первым выходом ко входу счетчика, а вторым выходом - к первому входу выходного блока, первый дешифратор, соединенный первыми выходами с первыми входами матрицы регистрации, вторые входы которой подключены к выходам первого-коммутатора, i введены второй и третий коммутаторы, первый и второй регистры адреса, второй дешифратор, первый элемент И,элемент ИЛИ,блок ключей, элемент ИЛИ-НЕ и второй элемент И, первый вход которого через элемент ИЛИ-НЁ подключен ко вторым входам матрицы регистрации, второй вход - к первому входу второго коммутатора, входу первого коммутатора и первому выходу второго дешифратора, входы которого соединены с выходами счетчика, а второй выход - с первьв 1 входом первого элемета И, второй вход которого подключен к третьему выходу блока управления, четвертый выход и первый вход которого соединень соответствено с первыми входами и выходом первого регистра адреса, а пятый выход и второй вход - соответственно с первыми выходом и входом второго регистра, вторые выходы первого и второго регистров адреса подключены к первым входам третьего коммутатора и первого дешифратора, вторые выходы которого через блок ключей соединены со вторялми входами выходного блока, подключенного третьими входами к выходам матрицы регистрации и первым входгии чэлеМента ИЛИ, второй вход которого соединен со втрым входом блока KJШ)чeй и выходом второго элемента И, а выход - с третьим входом блока управления, люстой выход которого подключен ко

второму входу второго коммутатора, выходы счетчика соединены со входами второго дешифратора, третий выход которого подключен ко второму входу третьего коммутатора.

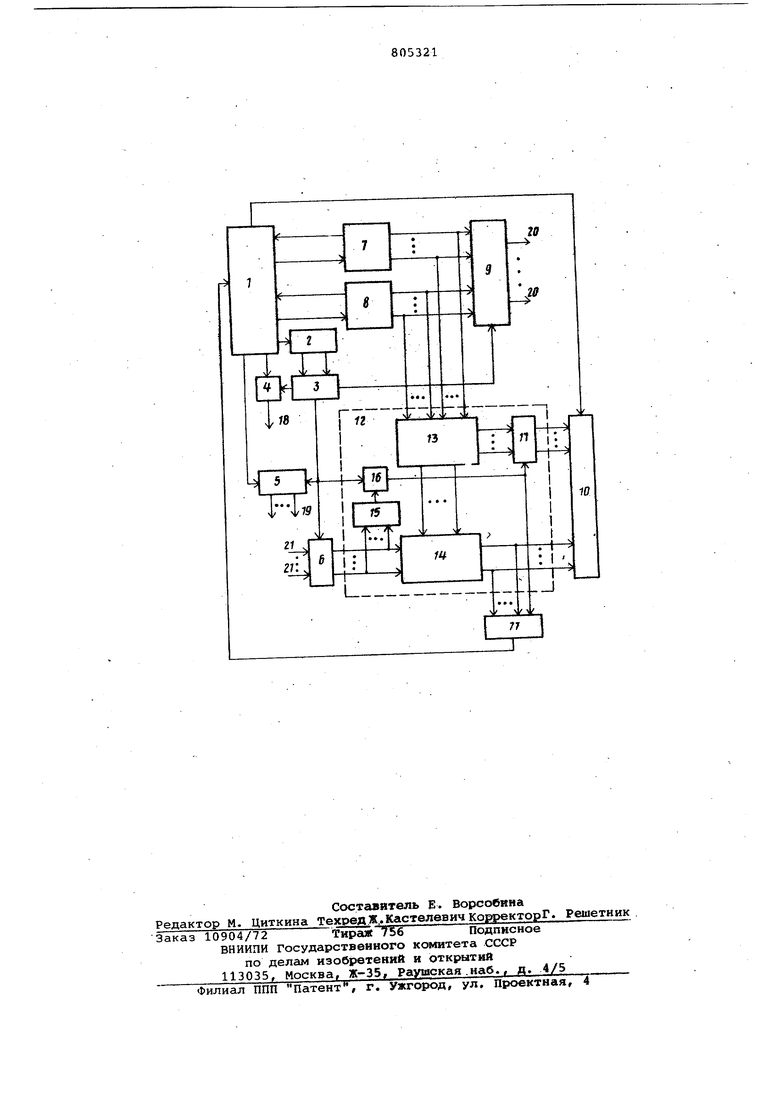

На чертеже представлена функциональная схема устройстваi

Устройство содержит блок 1 управления, счетчик 2, второй дешифратор 3, первый элемент И 4, второй коммутатор 5, первый коммутатор б, первый регистр 7 адреса, второй регистр 8 адреса, третий коммутатор 9, выходной блок 10, элемент ИЛИ 11, блок 12 анализа и регистрации сигналов, первый дешифратор 13, матрица 14 регистрации, элемент ИЛИ-НЕ,15, второй элемент И 16, блок 17 ключей, шина 18 сброса контролируемого блока, информационные шины 19 контролируемого блока, управляющие шины 20 контролируемого блок, контрольные точки 21 контролируемого блока.

Предлагаемое устройство позволяет автоматически обнаруживать неисправности и указывать номер неисправного коммутирующего элемента.

Устройство работает следующим образом.

Перед началом работы блок 1 управления производит установку в исходное состояние счетчика 2 ,. регистров 7 и 8.

Поиск неисправностей в контролиру емом блоке коммутации ЦИС осуществляется последовательным выбором коммутирующих элементов и проверкой их исправности. Проверка исправности каждого коммутирующего элемента осуществляется за Цикл, состоящий из трех тактов: установка в исходное состояние блока коммутации;выбор контролируемого коммутирующего элемента; проверка его исправности.

После выработки блоком 1 управления сигнала Пуск начинается первый цикл - проверка исправности первого коммутирующего элемента, соответствующего первой строчке первого столбца матрицы коммутации. При этом в первом такте этого цикла блок

1заносит единицы в первые разряды регистров 7 и 8 и одновременно с подачей сигнала на счетчик 2 устанавливает его в единичное состояние.

В результате этого дешифратор 3 открывает элемент И 4, и сигнал установки в исходное состояние поступает через элемент И 4 на шину 18 сброса контролируемого блока и устанавливает его в исходное состояние. Во втором такте первого цикла счетчик

2перебрасывается в состояние, равно двум. При дешифратор 3 подает управлшощий сигнал на коммутатор 9,

и в -результате с. выходов регистров 7 и 8 сигналы поступают через коммутатор 9 на управляющие шины 20 контролируемого блока, а так как в регистрах 7 и 8 записаны единицы в первых разрядах, то происходит выбор первого коммутирующего элемента В третьем такте перйогЬ цикЛа счетчи 2 перебрасывается в состояние,- равное трем, и дешифратор 3 подает разрешающий сигнал на коммутаторы 5 и 6 и на элемента И 16 блока 12. В результ.ате блок 1 управления подает сигнатш через коммутатор 5 н все ин формационные шины 19 контролируемог блока, а коммутатор 6 снимает сигналы с контрольных точек 21 и подает их на входы блока 12 анализа и регистрации сигналов.Этот блок производит выявление неисправностей.. В случае отсутствия неисправностей в первом кокилутирукадем элементе блок управления начинает второй цикл проверки, в течении которого проверяется второй когимутирующий элемент, соответствующий второй строчке первого столбца матрицы коммутации. При этом в первом такте второго цикла блок 1 .сдвигает на один разряд единицу в регистре 7 и устанавливает 2 в единичное Ъостояние, а далее проверка.исправности второго коммутирующего эл мента первого столбца осуществляется аналогично проверке исправности первого коммутирующего элемента. Когда единица в регистре 7 сдвиг . ется в последний разряд и проверяет ся последний коммутирующий элемент первого столбца, в первом такте следующего цикла проверки эта единица перезаписывается в первый разряд этого регистра, одновременно в регистре 8 единица сдвигается сиг налом из блока 1 во второй разряд и аналогично проверяются все коммутирующие элементы, соответствующие второму,столбцу матрицы коммутации. В случае, если в каком-то коммут рующем элементе блока коммутации ЦИС возникает неисправность, при вы боре этого коммутирующего элемента в третьем такте его проверки эта не исправность обнаруживается блоком 12. При этом, если в.озникла неисправность типа несрабатывание контролируемого коммутирующего элемента при отсутствии ложного срабатывания, то на контрольных точках 21 контролируемого блока коммутации имеются нулевые.сигналы и в ре зультате на выходе элемента ИЛИ-НЕ 15 блока 12 появляется единичный сигнал, который через элемент И 16 блока 12 поступает на вход блока 17 Дешифратор 13 блока 12 расшифровывает номер контролируемого коммутирующего элемента и подает разретоающий сигнал на соответртвуюйий. ключ блока 17, с выхода которого сигнал о неисправности поступает на индика цию в блок 10 вывода. Одновременно сигнал о неисправности контролируем го коммутирующего элемента с выхода элемента-И 16 поступает через элемент ИЛИ 11 в блок 1 управления. Если же возникает, неисправность типа ложное срабатывание коммутирующих элементов, то обнаружение этой неиспра вности производится в матрице , регистрации, состоящей из двухвходовых элементов И, на первые входы которых поступшот сигналы с выхода коммутатора 6, а на вторые - инверсные выходы дешифратора 13, которые подготавливают к прохождению сигналов все элементы И матрицы, 14 регистрации, кроме одного, соответствующего контролируемому коммутирующему элементу. Тогда в случае ложного ср батывания коммутирующих элементов сигналы с их выходов поступают через коммутатор 6 и через соответствующие элементы И матрицы 14 регистрации помех в блок 10,где происходит индикация номеров- неисправных коммутирующих элементов контролируемого блока коммутации ЦИС. Одновременно сигналы о неисправности коммутируквдих элементов с выходов матрицы 14 так же, как и в предыдущем случае с выхода элемента И 16, поступают через элемент ИЛИ 11 в блок 1 управления. При этом блок управления 1 запрещает переход к следующему циклу проверки, но продолжает подавать счгналы на счетчик 2, который работает .как счетчик по модулю 3. В результате этого 3 такта проверки - установка в исходное состояние блока коммутации, выбор контролируемого коммутирующего элемента и проверка его исправности - начинают циклически повторяться при одном и том же контролируемом коммутирующем элементе, при котором обнаружена неисправность. После выявления причины неисправности этого коммутирующего элемента внешним осмотром или с помощью осциллографа, входящего в блок 10, устройство выключается и неисправность устраняется. Затем снова устройство включается и снова производится проверка исправности коммутирующих элементов блока коммутации ЦИС, начиная с первого. После окончания проверки исправности последнего коммутирующего элемента, соответствующего последней строчке последнего столбца матрида коммутации, единицы в последних разрядов регистров 7 и 8 одновременно поступают в блок 1 управления и этот блок выраб тывает сигнал окон.-. чания проверки и сигнал исправности контролируемого блока коммутации ЦИС, который поступает на индика- . цию в блок 10. Как уже отмечалось, блок коммутации ЦИС позволяет соединять любой выход из N решающих блоков с любой из d входов каждого из. N решаюсшх блоков, т.е. блок коммутации ЦИС состоит из dN коммутирующих элементов. Тогда время обнаружения неисправностей в этом блоке при по мощи предлагаемого устройства составляетtoB 3-d где fm - тактовая частота работы устройства. Так как , 100 fm 1 - 2 МГц, то з.и-тН5о- оос,,,.,, И-2)-10Ь в то же время при ручном поиске не исправностей время обнаружения сос тавляет от десятков минут до неско ких часов. Таким образом,, предлагаемое уст ройство позволяет автоматизировать процесс поиска неисправностей в бл ках коммутации ЦИС и тем самым зна чительно сократить время обнаружения неисправностей в этих блоках при их наладке. Формула изобретения Устройство для обнаружения неисправностей в блоках коммутации цифровых интегрирующих структур, содержащее блок управления, подклю ченный первым выходом ко входу сче чика, а вторым выходом - к первому входу выходного блока, первый дешифратор, соединенный с первыми выходами с первыми входами матрицы регистрации, вторые входы которой подключены к выходам первого коммутатора, отличающееся тем, что, с целью расширения функциональных возможностей устройства в него введены второй и третий коммутаторы, первый и второй регистры адреса, второй дешифратор, первый элемент И, элемент ИЛИ, блок ключей, элемент ИЛИ-ПЕ и второй элемент И, первый вход которого через элемент ИЛИ-НЕ подключен ко вторым входам матрицы регистрации, второй входк первому входу второго коммутатора, входу первого коммутатора и первому выходу второго дешифратора, входы которого соединены с выходами счетчика, а второй выход - с первым входом первого элемента И, второй вход которого подключен к третьему выходу блока управления, четвертый выход и первый вход которого соединены соответственно с первыми входами и выходом первого регистра адреса, а пятый выход и второй вход - соответственно d первыми выходом и входом второго регистра, вторые выходы первого и второго регистров адреса подключены к первым входам третьего коммутатора и первого дешифратора, вторые выходы которого через .блок ключей соединены со вторыми входами выходного блока, подключенного третьими входами к выходам матрицы регистрации и первым входам элемента ИЛИ, второй вход которого соединен со вторым входом блока ключей и выходом второго элемента И, а выход - с третьим входом блока управления, шестой выход которого подключен ко второму входу второго коммутатора, выходы счетчика соединены со входами второго дешифратора, третий выход которого подключен ко второму входу третьего коммутатора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР I 203326, кл. & 06 F 11/00, 1964. 2.Авторское свидетельство СССР 370609, кл. G Об F 11/04, 1969 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения неисправностей в блоках коммутации цифровых интегрирующих структур | 1980 |

|

SU962961A1 |

| Устройство для диагностики неисправностей цифровых интеграторов | 1979 |

|

SU877551A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1014041A1 |

| Способ диагностики отказов динамических объектов и устройство для его осуществления | 1990 |

|

SU1718190A1 |

| Устройство для контроля памяти | 1984 |

|

SU1236558A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1278855A1 |

| Устройство для контроля электрического монтажа | 1985 |

|

SU1390616A1 |

| Устройство для контроля монтажных схем | 1980 |

|

SU920747A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для обнаружения и локализации неисправностей цифровых блоков | 1982 |

|

SU1067507A1 |

Авторы

Даты

1981-02-15—Публикация

1978-11-28—Подача