Изобретение относится к вычислительной технике и может быть использовано для сопряжения мультипроцессорных средств предварительно обработки телеметрической информаци с универсальными вычислительными ма шинами или с периферийными средствами регистрации и отображения. Известно устройство, содержащее блок приема информации, первый вход которого подключен к выходу блока адреса данных, а первый выход - к блоку выдачи данных, выход которого соединен с первым входом блока адреса данных и с первым входом блока объема данных, выход которого соединен с вторым входом блока адреса данных 1. Недостаток этого устройства большие затраты оборудования. Наиболее близким по технической сущности к изобретению является ус ройство, содержащее блок приема информации, вход-выход которого является первым входом-выходом устройства, первый вход подключен к выходу блока хранения адреса данных, а первый выход - к входу блока выдачи данных, вход-выход которого является вторым входом-выходом устройства, выход соединен с первыми входа- , ми блока хранения адреса данных, и блок хранения объема данных, выход которого соединен со вторым входом блока хранения адреса данных 2. Недостаток этого устройства состоит в больших затратах оборудования. Известные устройства позволяют восстановить исходную последовательность сообщений абсолютно точно. Однако при построении некоторых комплексов обработки-телеметрической информации бывает вполне достаточно иметь не абсолютное, а относительное восстановление исходной последовательности, смысл которого состоит в том, что при параллельной

обработке телеинформации несколькими блоками (процессорами ) предварительной обработки допускается нарушение результирующей выходной последовательности относительно входной между реперными сообщениями (,измерениями, точками, к которым привязываются все остальные сообщения. Реперными сообщениями могут быть как Временные посылки (оцифровки секунд или сигналы милисекунд), так и специальные периодические или непериодические посылки (наличие какого-либо канала, определенное состояние какого-либо канала и т.п.). Нарушение последовательности между реперными сообщениями происходит из-за случайного времени обработки исходных сообщений в блоках предварительной обработки,так как это время определяется выполнением конкретного алгоритма из совокупности имеющихся. Как правило, частота появления реперных сообщений крайне низка по сравнению с частотой следования исходных телеизмерений.

Цель изобретения - сокращение затрат оборудования и упрощение устройства.

Поставленная цель достигается тем, что, в устройство, содержащее блок приема информации, вход-выход которого является первым входом-выходом устройства,первый вход подключе к выходу блока хранения адоеса данных, а первый выход - к входу блока выдачи данных, вход-выход которого является вторым входом-выходом устройства, а выход соединен с первыми входами блока хранения адреса данных, и блок хранения объема данных, выход которого соединен с вторым Входом блока хранения адреса данных, введен блок формирования сигнала, разрешения, включающий группу триггеров, элемент И, триггер и элемент задержки, причем второй выход блока приема информации соединен с третьим входом блока хранения адреса данных и с вторым входом блока хранения объема данных, второй входс выходом блока хранения объема данных, а третьи вход и выход - соответственно с выходом элемента И и первым входомТриггера, первые и вторые входы триггеров группы соединены с соответствующими выходами первой и второй групп выходов блока приема информации, выходы - с группой входов элемента И, выход которого соединен через элемент задержки с вторым входом триггера, выход которого соединен с входом элемента И.

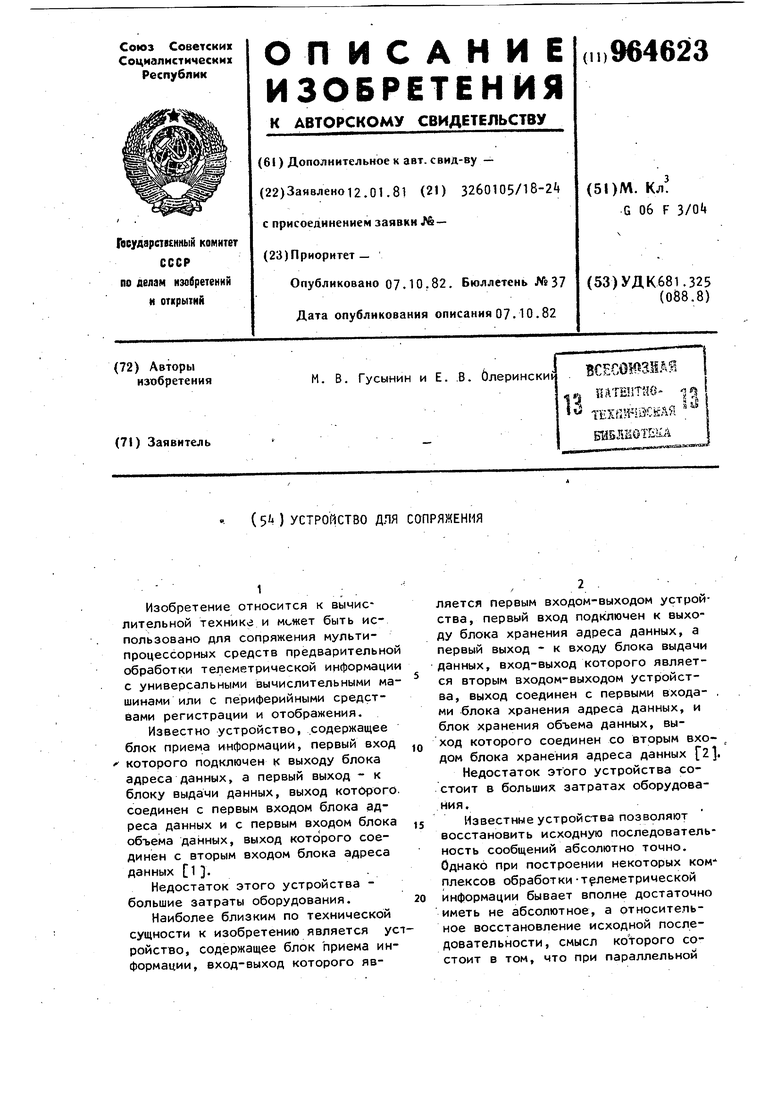

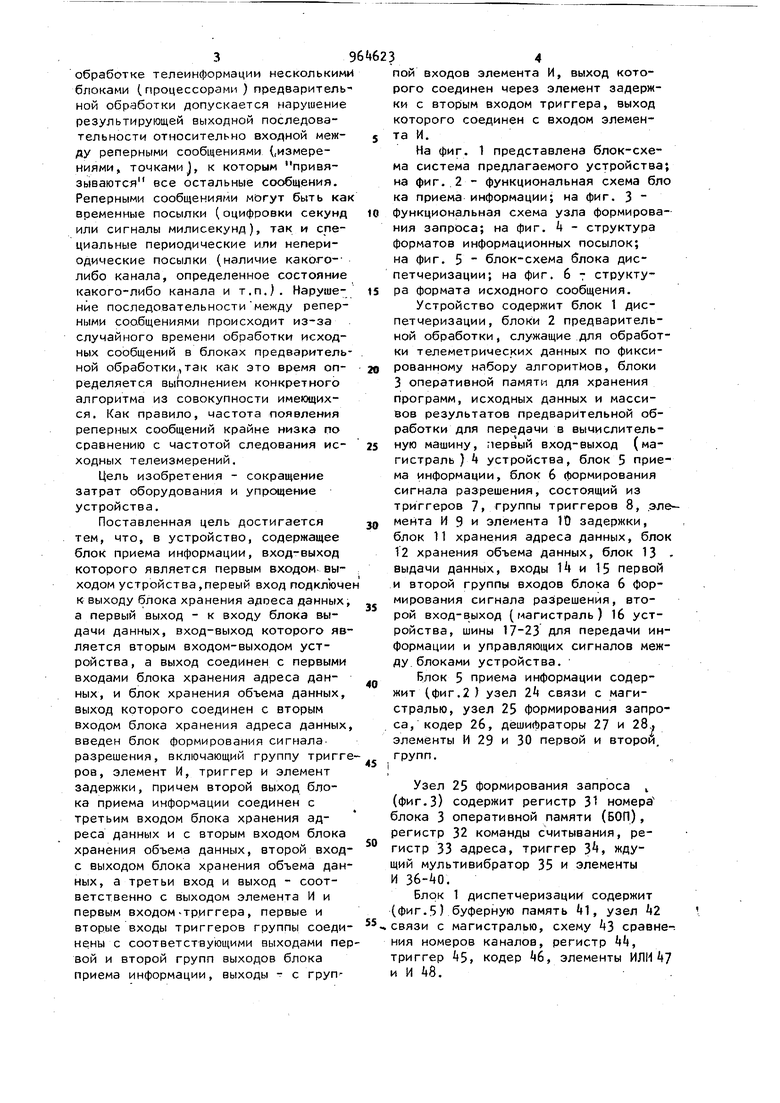

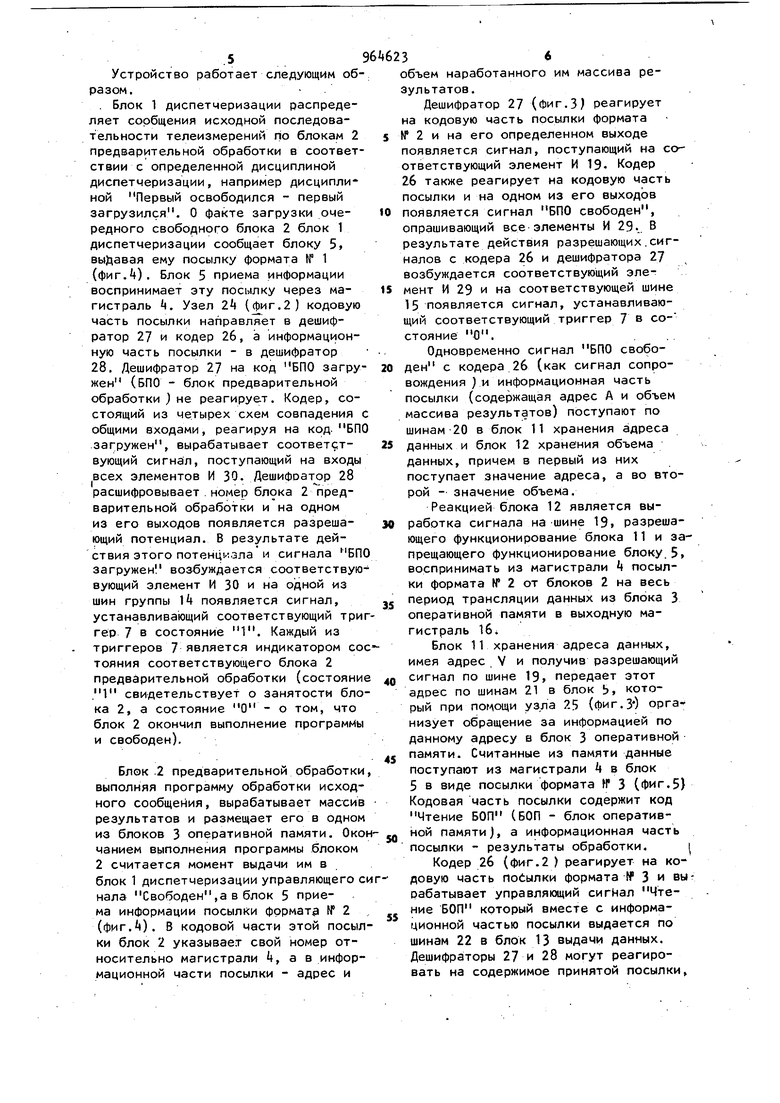

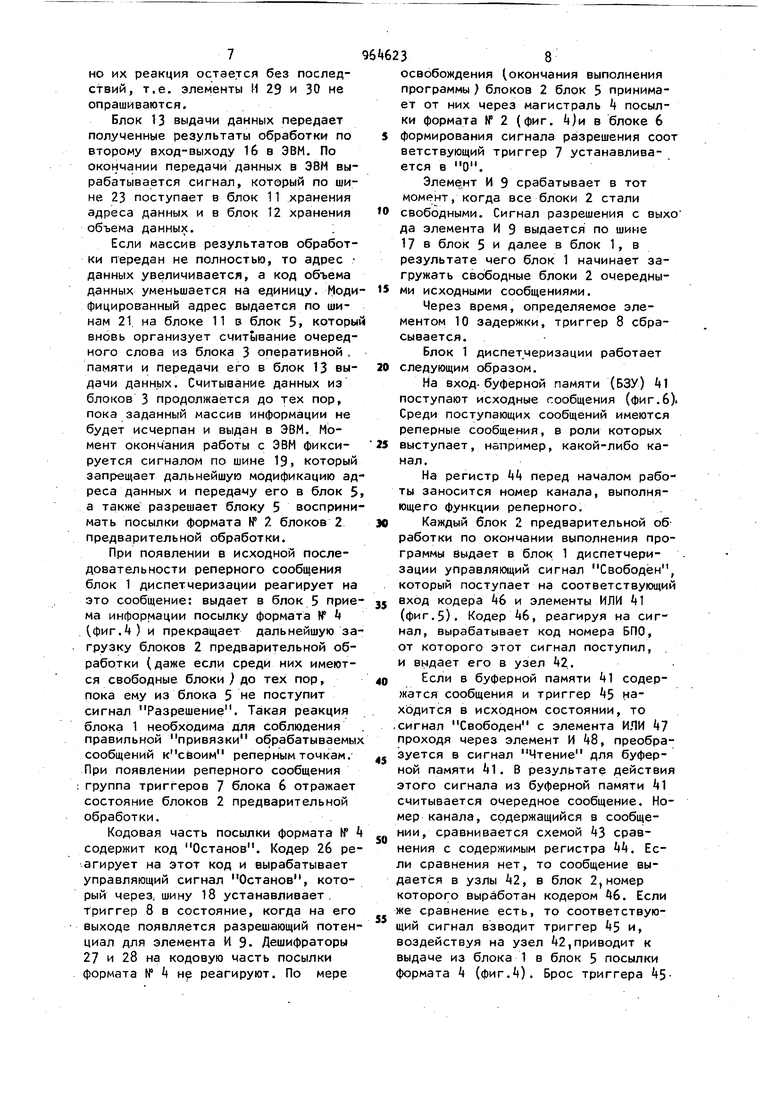

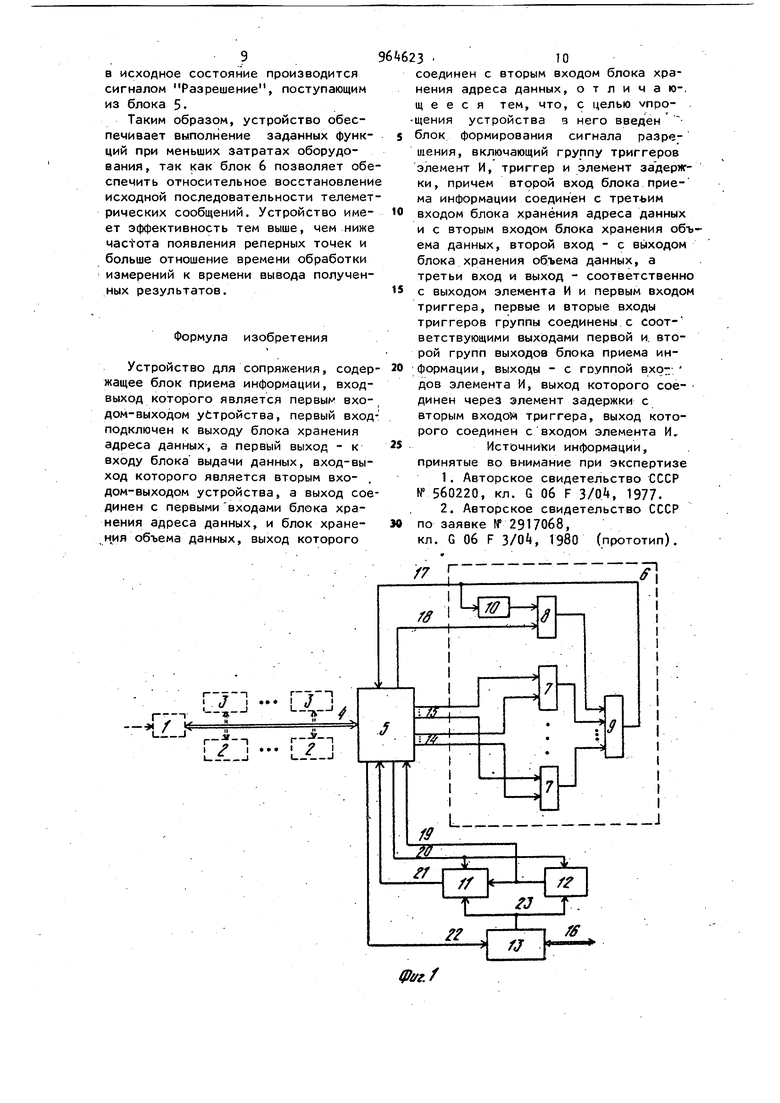

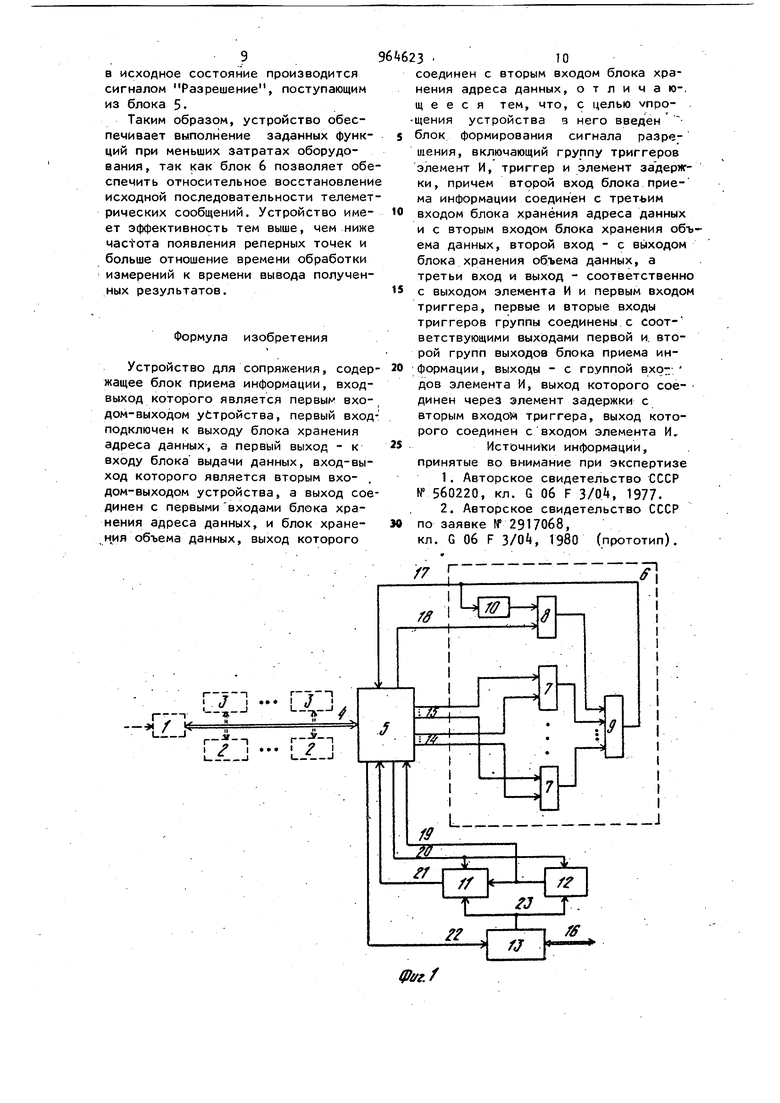

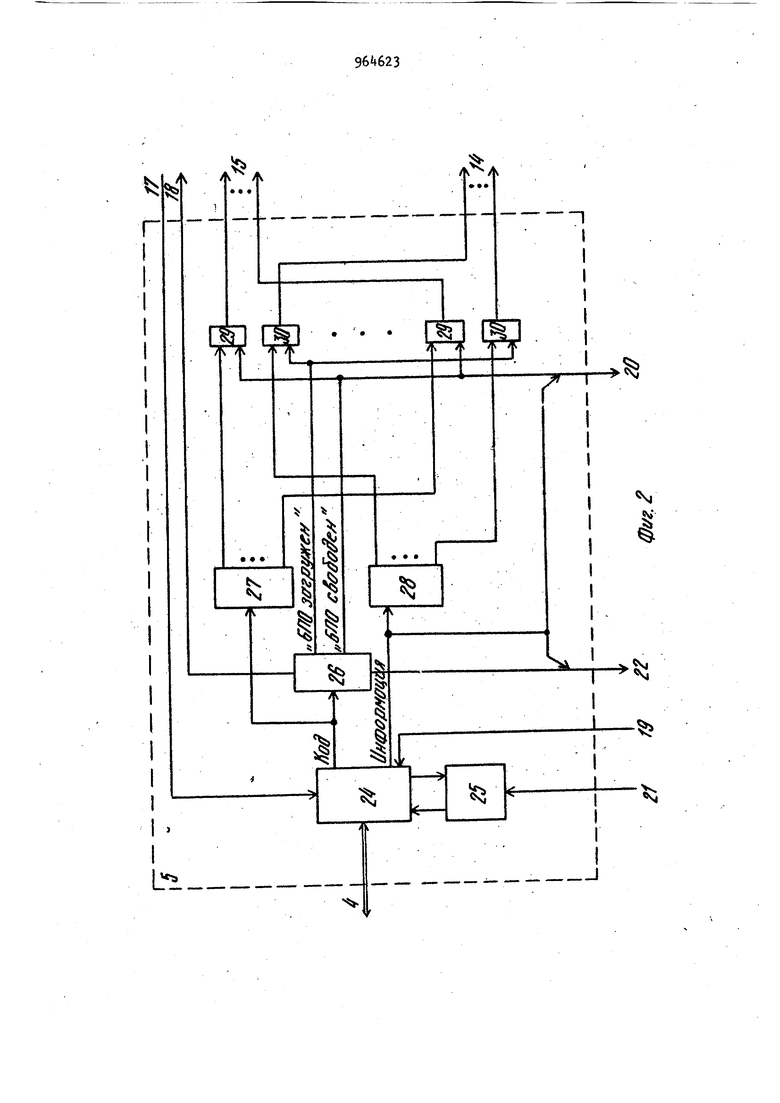

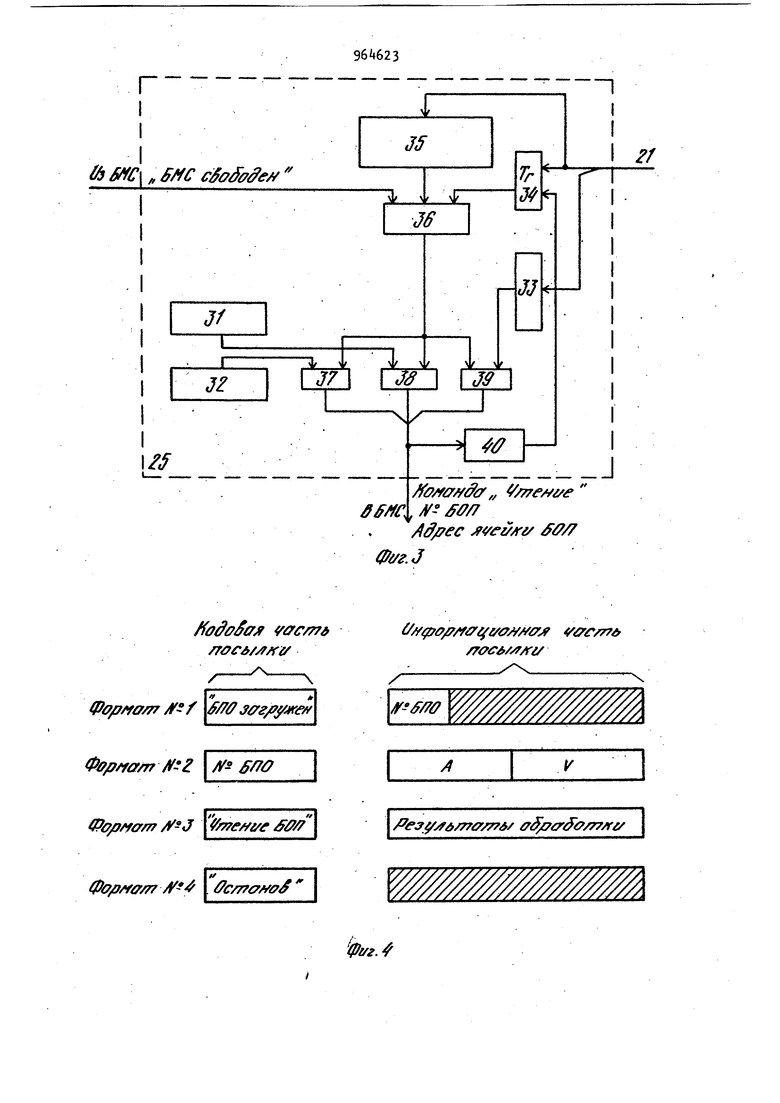

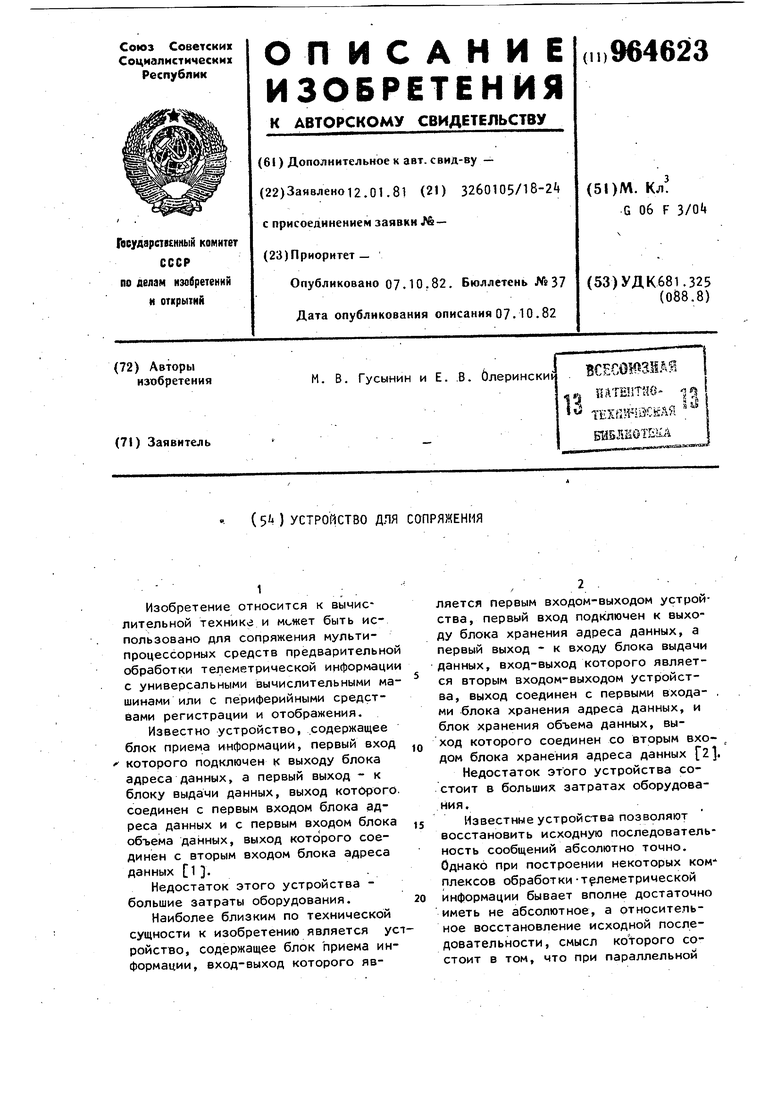

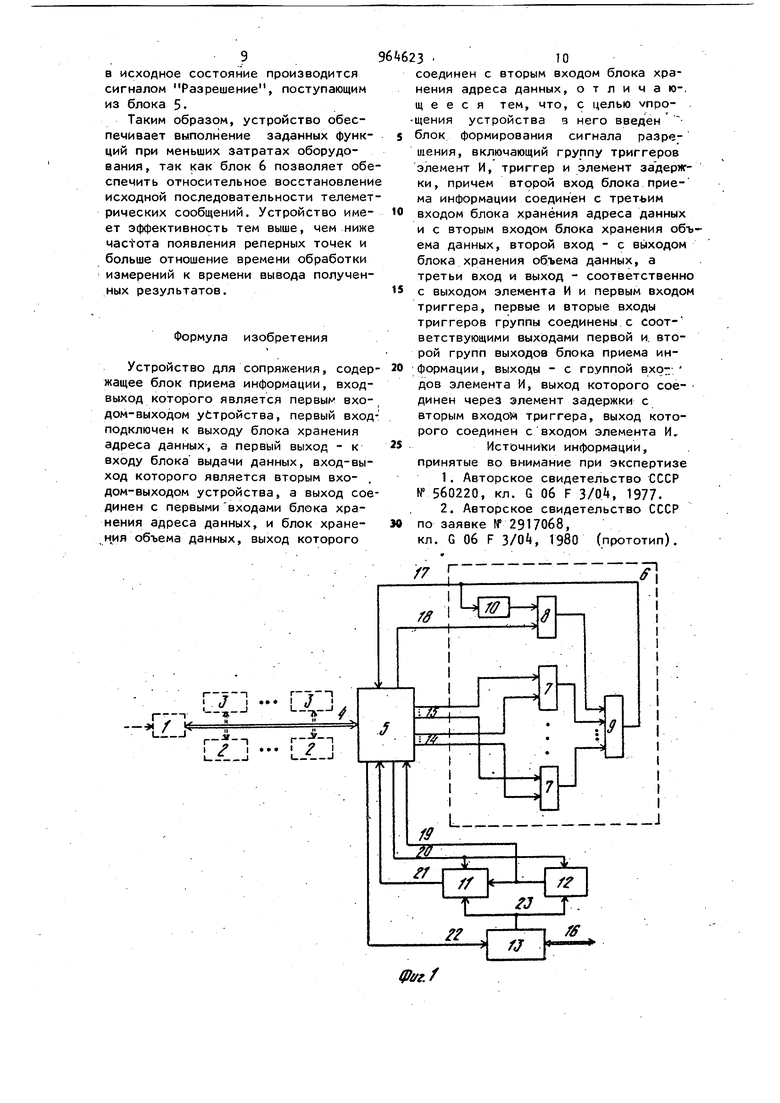

На фиг. 1 представлена блок-схема система предлагаемого устройства; на фиг. 2 - функциональная схема бло ка приема информации; на фиг. 3

0 функциональная схема узла формирования запроса; на фиг. 4 - структура форматов информационных посылок; на фиг. 5 блок-схема блока диспетчеризации; на фиг. 6 7 структура формата исходного сообщения.

Устройство содержит блок 1 диспетчеризации, блоки 2 предварительной обработки, служащие для обработки телеметрических данных по фиксированному набору алгоритмов, блоки 3 оперативной памяти для хранения программ, исходных данных и массивов результатов предварительной обработки для передачи в вычислительную машину, первый вход-выход (магистраль ) устройства, блок 5 приема информации, блок 6 формирования сигнала разрешения, состоящий из триггеров 7, группы триггеров 8, :эпе- мента И 9 и элемента 10 задержки, блок 11 хранения адреса данных, блок 12 хранения объема данных, блок 13 выдачи данных, входы 14 и 15 первой и второй группы входов блока 6 формирования сигнала разрешения, второй вход-выход (магистраль) 16 устройства, шины 17-23 для передачи информации и управляющих сигналов между, блоками устройства.

Блок 5 приема информации содержит (фиг. 2 ) узел 2 связи с магистралью, узел 25 формирования запроса, кодер 26, дешифраторы 27 и 28 элементы И 29 и 30 первой и второй, групп.

Узел 25 формирования запроса (фиг.З) содержит регистр 31 номера блока 3 оперативной памяти (БОП), регистр 32 команды считывания, регистр 33 адреса, триггер 3, «ДУ щий мультивибратор 35 и элементы И 36-40.

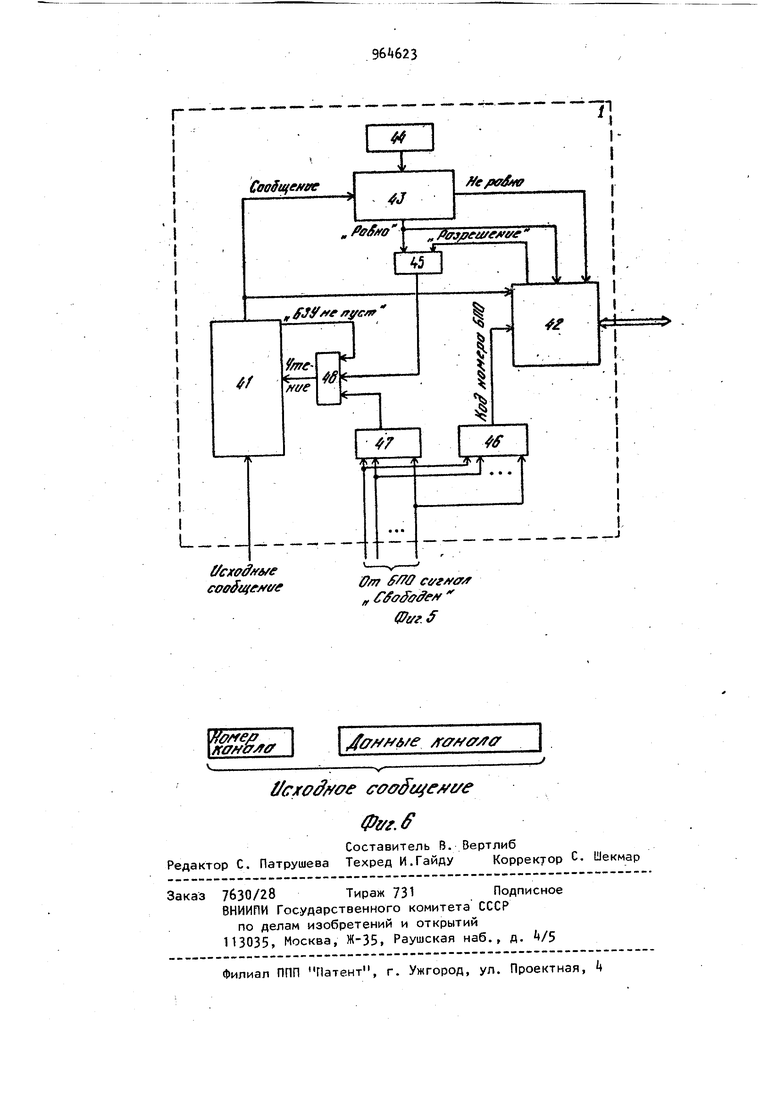

Блок 1 диспетчеризации содержит (фиг.5) буферную память 41, узел 42 связи с магистралью, схему 43 сравне-. ния номеров каналов, регистр 44, триггер 45, кодер 46, элементы ИЛИ 47 и И 48. Устройство работает следующим образом, . Блок 1 диспетчеризации распределяет сообщения исходной последовательности телеизмерений по блокам 2 предварительной обработки в соответствии с определенной дисциплиной диспетчеризации, например дисциплиной Первый освободился - первый загрузился. О факте загрузки очередного свободного блока 2 блок 1 диспетчеризации сообщает блоку 5 выйавая ему посылку формата № 1 (фиг.). Блок 5 приема информации воспринимает эту посылку через магистраль Ц, Узел 2Ц (фиг.2) кодовую часть посылки направляет в дешифратор 27 и кодер 26, а информационную масть посылки - в дешифратор 28. Дешифратор 27 на код БПО загру жен (БПО - блок предварительной обработки ) не реагирует. Кодер, состоящий из четырех схем совпадения общими входами, реагируя на код. БП .загружен, вырабатывает соответс;твующий сигнал, поступающий на входы всех элементов И 30. Дешифоат эр 28 расшифровывает.номер блока 2 предварительной обработки и на одном из его выходов появляется разрешающий потенциал. В результате действия этого потейцизла и сигнала БП загружен возбуждается соответствую вующий элемент И 30 и на одной из шин группы 14 появляется сигнал, устанавливающий соответствующий три гер 7 в состояние 1. Каждый из триггеров 7 является индикатором со тояния соответствующего блока 2 предварительной обработки (состояни .1 cвидeтeльcтвyet о занятости бло ка 2, а состояние О - о том, что блок 2 окончил выполнение программы и свободен). Блок 2 предварительной обработки выполняя программу обработки исходного сообщения, вырабатывает массив результатов и размещает его в одном из блоков 3 оперативной памяти. Око чанием выполнения программы блоком 2 считается момент выдачи им в блок 1 диспетчеризации управляющего с нала Свободен,а в блок 5 приема информации посылки формата № 2 (фиг.). В кодовой части этой посыл ки блок 2 указывает свой номер относительно магистрали k а в информационной части посылки - адрес и бъем наработанного им массива реультатов. Дешифратор 27 (фиг.З) реагирует на кодовую часть посылки формата 2 и на его определенном выходе оявляется сигнал, поступающий на соответствующий элемент И 19- Кодер 26 также реагирует на кодовую часть посылки и на одном из его выходов появляется сигнал БПО свободен, опрашивающий все элементы И 29... В результате действия разрешающих.сигналов с кодера 2б и дешифратора 27 возбуждается соответствующий элемент И 29 и на соответствующей шине 15 появляется сигнал, устанавливающий соответствующий триггер 7 в состояние 3. Одновременно сигнал БПО свободен с кодера 26 (как сигнал сопровождения ) и информационная часть посылки (содержащая адрес А и объем массива результатов) поступают по шинам 20 в блок И хранения адреса данных и блок 12 хранения объема данных, причем в первый из них поступает значение адреса, а во второй - значение объема. Реакцией блока 12 является выработка сигнала на -шине 19 разрешающего функционирование блока 11 и запрещающего функционирование блоку.5. воспринимать из магистрали Ц посылки формата № 2 от блоков 2 на весь период трансляции данных из блока 3 оперативной памяти в выходную магистраль 16 i Блок 11 хранения адреса данных, имея адрес V и получив разрешающий сигнал по шине 19, передает этот адрес по шинам 21 в блок Ь, который при помощи узла 25 (фиг.З) организует обращение за информацией по данному адресу в блок 3 оперативной памяти. Считанные из памяти данные поступают из магистрали А в блок 5 в виде посылки формата tf 3 СФиг.Б} Кодовая часть посылки содержит код Чтение БОП (БОП - блок оперативной памятиj, а информационная часть посылки - результаты обработки. Кодер 2б (фиг.2 ) реагирует на кодовую часть посылки формата № 3 и вырабатывает управляющий сигнал Чтение БОП который вместе с информационной частью посылки выдается по шинам 22 в блок 13 выдачи данных. Дешифраторы 27 и 28 могут реагировать на содержимое принятой посылки.

но их реакция остается без последствий, т.е. элементы И 29 и 30 не опрашиваются.

Блок 13 выдачи данных передает полученные результаты обработки по второму вход-выходу 16 в ЭВМ. По окончании передачи данных в ЭВМ вырабатывается сигнал, который по шине 23 поступает в блок 11 хранения адреса данных и в блок 12 хранения объема данных.;

Если массив результатов обработки передан не полностью, то адрес данных увеличивается, а код объема данных уменьшается на единицу. Модифицированный адрес выдается по шинам 21. на блоке 11 в блок 5 который вновь организует считьшание очередного слова из блока 3 оперативной . памяти и передачи его в блок 13 выдачи данных. Считывание данных из блоков 3 продолжается до тех пор, пока заданный массив информации не будет исчерпан и выдан в ЭВМ. Момент окончания работы с ЭВМ фиксируется сигналом по шине 19, который запрещает дальнейшую модификацию адреса данных и передачу его в блок 5 а также разрешает блоку 5 воспринимать посылки формата № 2 блоков 2 предварительной обработки.

При появлении в исходной последовательности реперного сообщения блок 1 диспетчеризации реагирует на это сообщение: выдает в блок 5 приема информации посылку формата W , (, ) и прекращает дальнейшую загрузку блоков 2 предварительной обработки (даже если среди них имеются свободные блоки ) до тех пор, пока ему из блока 5 не поступит сигнал Разрешение. Такая реакция блока 1 необходима для соблюдения правильной привязки обрабатываемых сообщений к своим репернымточкам. При появлении реперного сообщения группа триггеров 7 блока 6 отражает состояние блоков 2 предварительной обработки.

Кодовая часть посылки формата № k содержит код Останов. Кодер 26 реагирует на этот код и вырабатывает управляющий сигнал Останов, который через, шину 18 устанавливает, триггер 8 в состояние, когда на его выходе появляется разрешающий потенциал для элемента И 9. Дешифраторы 27 и 28 на кодовую часть посылки формата № 4 не реагируют. По мере

освобождения (окончания выполнения программы ) блоков 2 блок 5 принимает от них через магистраль k посылки формата № 2 (фиг. )и в блоке 6

$ формирования сигнала разрешения соот ветствующий триггер 7 устанавливается в О.

Элемент И 9 срабатывает в тот момент, когда все блоки 2 стали

О свободными. Сигнал разрешения с выхо да элемента И 9 выдается по шине 17 8 блок 5 и далее в блок 1, в результате чего блок 1 начинает загружать свободные блоки 2 очередными исходными сообщениями.

Через время, определяемое элементом 10 задержки, триггер 8 сбрасывается.

Блок 1 диспетчеризации работает

20 следующим образом.

На вход, буферной памяти (БЗУ) 1 поступают исходные сообщения (фиг.6). Среди поступающих сообщений имеются реперные сообщения, в роли которых 5 выступает, например, какой-либо канал.

На регистр kk перед началом работы заносится номер канала, выполняющего функции реперного.

О Каждый блок 2 предварительной обработки по окончании выполнения программы Выдает в блок 1 диспетчеризации управляющий сигнал Свободен, который поступает на соответствующий

J вход кодера А6 и элементы ИЛИ Ц (фиг.5). Кодер А6, реагируя на си|- нал, вырабатывает код номера БПО, от которого этот сигнал поступил, и выдает его в узел .

0 Если в буферной памяти 41 содержатся сообщения и триггер нахЬдится в исходном состоянии, то .сигнал Свободен с элемента ИЛИ проходя через элемент И 48, преобра., зуется в сигнал Чтение для буферной памяти 41. 8 результате действия этого сигнала из буферной памяти 41 считывается очередное сообщение. Номер канала, содержащийся в сообщении, сравнивается схемой 43 сравнения с содержимым регистра 44. Если сравнения нет, то сообщение выдается в узлы 42, в блок 2,номер которого выработан кодером А6. Если же сравнение есть, то соответствующий сигнал взводит триггер 45 и, воздействуя на узел 42,приводит к выдаче из блока 1 в блок 5 посылки формата 4 (фиг.4). Брос триггера 45в исходное состояние производится сигналом Разрешение, поступающим из блока 5. Таким образом, устройство обеспечивает выполнение заданных функций при меньших затратах оборудования, так как блок 6 позволяет обе спечить относительное восстановлени исходной последовательности телемет рических сообщений. Устройство имеет эффективность тем выше, чем ниже 4actoTa появления реперных точек и больше отношение времени обработки измерений к времени вывода полученных результатов. Формула изобретения Устройство для сопряжения, содер жащее блок приема информации, входвыход которого является первым входом-выходом устройства, первый вход подключен к выходу блока хранения адреса данных, а первый выход - к входу блока выдачи данных, вход-выход которого является вторым входом-выходом устройства, а выход сое динен с первымивходами блока хранения адреса данных, и блок хране,Ния объема данных, выход которого 3 10 соединен с вторым входом блока хранения адреса данных, о т л и ч а ю-, щ е е с я тем, что, с целью vnpo- . щения устройства з него введен блок формирования сигнала разрешения, включающий группу триггеров элемент И, триггер и элемент задержки, причем второй вход блока приема информации соединен с трет-ьим входом блока хранения адреса данных и с вторым входом блока хранения объема данных, второй вход - с выходом блока хранения объема данных, а третьи вход и выход - соответственно с выходом элемента И и первым входом триггера, первые и вторые входы триггеров группы соединены с соответствующими выходами первой и. второй групп выходов блока приема информации , выходы - с гоуппой вхо-; дов элемента И, выход которого соединен через элемент задержки с вторым входов триггера, выход которого соединен с входом элемента И, Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 560220, кл. G Об F 3/ОЛ, 1977. 2.Авторское свидетельство СССР по заявке tf 2917068, кл. G Об F 3/Q, 1980 (прототип).

Г

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения | 1981 |

|

SU1001072A1 |

| Устройство для сопряжения | 1980 |

|

SU903853A1 |

| Устройство для сопряжения | 1982 |

|

SU1022143A1 |

| Устройство для управления обменом информации | 1982 |

|

SU1081638A1 |

| Устройство для сопряжения ЭВМ с каналом связи | 1988 |

|

SU1656544A1 |

| Адаптивная система обработки данных | 1984 |

|

SU1241250A1 |

| Устройство для обмена информацией | 1980 |

|

SU898414A1 |

| Буферное запоминающее устройство | 1978 |

|

SU750567A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ИСПРАВЛЯЮЩЕЙ СПОСОБНОСТИ ПРИЕМНИКОВ ДИСКРЕТНЫХ СИГНАЛОВ | 1992 |

|

RU2040118C1 |

| Устройство для обмена данными в вычислительной сети | 1988 |

|

SU1599864A1 |

/fo ffSffjr VffC/77d

ffCAM/fe

ff

fPo/Jffff/TT S f

Фffp/faf/r7 /if:Z IЖ fff7O

o/f/ fffTf Ж-J /7 е//г/е ff

rf

ffc/77f7M7

/Й7/Гг7/У«:, /77e/ ufe

ег/л1 ff/7

Фt/г.J

f//f pff/7/fffi i ff////a

/7ffCA/ /ri/

X

/f-/

ey jfA/7ra//76/ ff /7er 0/77/f /

фуг.

Авторы

Даты

1982-10-07—Публикация

1981-01-12—Подача