Изобретение относится к запоминающим устройствам.

Известно запоминающее устройство, которое содержит регистры памяти, логические схемы по числу регистров памяти, триггеры по числу регистров памяти и элементы И Ч.

Недостатком этого устройства являются большие аппаратурные затраты. .

Наиболее близким техническим решением к изобретению является буферное запоминающее устройство, содержащее накопитель на регистрах памяти и логические схемы ПО числу регистров памяти

Недостаткомэтого устройства является его сложность, вследствие чего снижается его надёжность.

Цель изобретения - повышение надежности устройства..

Поставленная цель достигается тем, что в буферное запоминающее, устройство, содержащее накопитель, одни из входов и выходы которого являются информационными входами и выходами устройства, введены блок управления режима.ми работы и адресный блок, входы и первый выход которого I соединены с другими входами накопителя, второй, третий и четвертый. .

выходы адресного блока подключены соответственно к первому, второму и третьему входам блока управленияг режимами, выходы которого и входы адресного блока являются соответственно управляющими выходами и входами устройства.

Адресный блок содержит дешифратор,

10 счетч«ки, элементы И, элементы задержки и элемент ИЛИ, выход которого соединен с входом дешифратора, а вхот ды подключены соответственно к выходам первого и второго элементов И,

15 первые входаа которых соединены с входами первого и второго элементов задержки соответственно, выходы которых подключены соответственно к входам первого и второго счетчиков,

20 выход первого счетчика соединен с вторым входом первого элемента И и первым входом третьего элемента И, второй вход которого подключен к выходу второго счетчика и второму входу второго элемента И, выходы дешифратора и третьего элемента И, выходы и входы первого и второго элементов задержки являются соответственно выходами с первого по четвертый

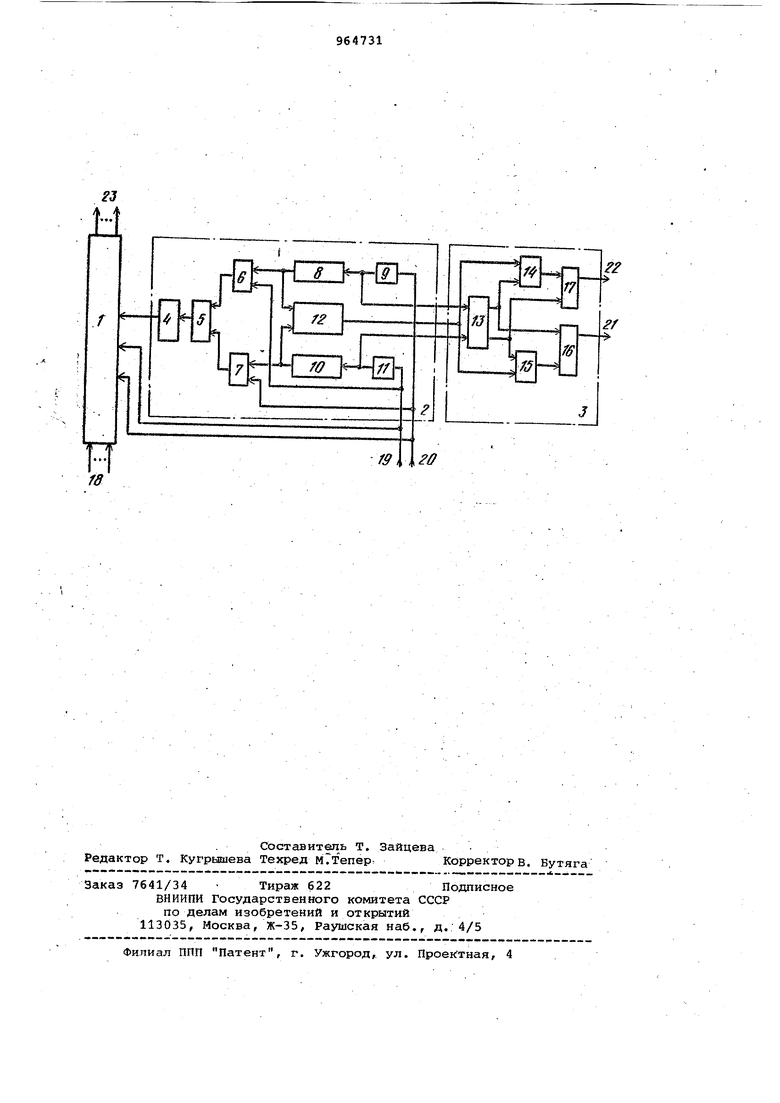

30 и входами блока. Кроме того, блок управления режи мами работы содержит триггеры,, четвертый и пятый элементы И, причем прямой вйхрд первого триггера подкл чен к первым входам четвертого элемента И и второго триггера, второй вход которого соединен с выходом пятого элемента И, первый вход кото рого подключен к инверсному выходу первого триггера и-первому входу трет его триггера, второй вход которого соединен с выходом четвертого элеме та И, вторые входы четвертого и пят го элементов И объединены и являютс первыми входами блока, вторым и третьим входами и выходами которого являются первый и второй входа первого триггера и выходы второго и третьего триггеров.. . На чертеже изображены функционал ные схемы предложенного устройства, адресного блока и блока управления режимами работы. Устройство содержит накопитель 1 на регистрах памяти (не показаны), .адресный блок 2 и блок 3 управления режимами работы. Адресный блок содер жит дешифратор 4, элемент ИЛИ 5, первый 6 и второй 7 элементы И, первый счетчик 8, предназначенный для формирования адреса чтения, первый элемент 9 задержки, второй счетчик 10, предназначенный для формирования адреса записи, второй элемент 11 эадержки и третий элемент И 12. Блок управления режимами работы содержит первый триггер 13, четвертый 14 и пятый 15 элементы И,, второй 16 и Третий 17 триггеры. На чертеже обозначены информационные 18 и,управляющие 19 и20 входы устройства, управ ляющие 21 и 22 и информационные 23 выходы устройства. . Предложенное устройство работает следующим образом. Адресный блок 2 вырабатывает адрее, в соответствии с которым происходит запись или чтение данных из . накопителя 1. Блок 3 служит для индикации состояния накопителя 1 (полностью свободен, частично занят или полностью занят), в соответствии с которым организуется работа устройства. В исходном состоянии все регистры накопителя 1 свободны. Триг гер 13 находится в единичном состоянии и сигнал с его прямого выхода устанавливает триггер 16 в единичное состояние, на выходе 21 устройства появляется единичный сигнал,, что соответствует разрешению записи. Содер жимое счетчиков 10 и 8 равно нулю. Элемент И 12 вырабатывает сигнал сов падения, который через элемент И 14 устанавливает триггер 17 в нулевое состояние, при этом на выходе 22 уст ройства появляется нулевой сигнал, что соответствует запрету чтения. Таким образом, в исходном состоянии разрешена только запись данньлх в накопитель 1. При подаче управляющего сигнала записи на сход 19 устройства он поступает в накопитель 1, информация с входов 18 устройства подается в на опитель 1. Этот же управляющий сигнал записи открывает элемент И 7, и так. как содерхсимое счетчика 10 равно нулю, то нулевой код-адреса записи через элемент ИЛИ 5 поступает на вход дешифратора 4, сигнал с нулевого выхода которого организует запись слова данных в нулевой регистр накопителя 1. . Задержанный управляющий сигнал за-, писи с выхода элемента 11 задержки увеличивает содержимое счетчика 10: на единицу, т.е. формируется следующий адрес для .записи данных.. Эти.м же задержанным сигнешом устанавливается в нулевое состояние триггер 13, сигнал с инверсного выхода которого устанавливает в единичное состояние триггер 17, снимая запрет чтения. Таким образом, чтение данных из накопителя 1 возможно только в том случае, еслд. происходит запись внего хотя бы одного слова. Работа устройства при чтении данных аналогична рассмотренной выше за исключением того, что триггер 13 в этом случае устанавливается в единичное состояние и снимает сигнал запрета записи, если он установлен. Информация при .этом считывается с выходов 23.устройства. В устройстве вырабатываются сигналы запрета записи данных в полностью занятый накопитель 1, а также запрета чтения данных из пустого накопителя 1. В таких случаях содержимое счетчиков 10 и 8 равно между собой, что приводит к срабатыванию элемента И 12, сигнал с выхода которого через элементы И 14 или 15 приводит к установке в нулевое состояние триггеров 16 или 17, что соответствует сигналам запрета записи, или чтения. . Например, происходит .запись данных в накопитель 1 до полного его. запол- нения, -причем чтение данных .не производится. В этом случае после записи последнего слова данных в накопитель 1 сигнал, задержанный элементом 11 задержки, вызьавает переполнение (обнуление) счетчика 10, а так как . содержимое счетчика 8 также равно нулю, то срабатывает элемент И 12, сигнал с выхода которого через элеент и 15- устанавливает в нулевое состояние Триггер 16, тем самым выабатывая сигнал запрета записи дан ных в накопитель 1.

Аналогичным образом хпроисходит выработка запрета чтения данных из пустого накопителя 1.

Таким образом, в устройстве определяется степень занятости накопителя 1 (полностью свободен - разрешена только запись, частично содержит данные - разрешены и чтение и запись, полностью занят - разрешено только чтение), о чем сообщается абонентам, что расширяет область приме нения Устройства и по вышает надежность работы; устройства.

Доли дппа|)а урных затрат, приходящейся на йШоянейие адресного блока 2 и блока3 управления режимш и работы, значительно снижается при увеличении емкости накопителя 1, за счет чего также повышается надежность устройства.

, Технико-экономическое преимущество предложенного, устройства заключается в его более высокой надежности по сравнению с известным.

Формула изобретения

1.Буферное запоминающее устройство , содержащее накопитель, Один

из входов и выходов которого являются информационными входами и выхода 4и устройства, о т л и ч а ю щ е ес я тем, что, с целью повышения надежности устройства, оно содержи блок управления режимами работы и, адресный блок, входы и первый выход которого соединены с другими входами накопителя, второй, третий и четвертый выходы адресного блока подключены соответственно к первому, второму и третьему входам блока управления режимами работы, выходы которого и входы адресного блока являются соот вётственно управляющими выходами и входами устройства.

2.Устройство по п.. 1, о т л ичающее с я тем, что адресный блок Содержит дешифратор, счетчики,

элементы И, элементы задержки и элемент ИЛИ выход КОТОРОГО соединен .с входом дешифратора а входы подключены соответственно к выходам пеового и второго элементов И, первые входы которых соединены с входами первого и второго элементов задерж . ки соответственно, выходы последних подключены соответственно к входам первого и второго счетчиков, выход

0 первого счетчика соединен с вторым входом первого элемента И и первым входом третьего элемента И, в торой вход которого по ключен к выходу второго счетчика и второму входу второго элемента И, выходы дешифратора и третьего элемента И, выходы и вхр ды первого и второго элементов задержки являются соответственно выходами с первого по четвертый и входами блока.

3 Устройство по пп. 1 и 2, о Тл и ч а ю щ е е с я тем, что блок управления режимами работы содержит триггеры, четвертый и пятьш элементы И, причем прямой выход первого триггера подключен к первым входам четвертого элемента И и второго триггера, второй вход которс го соединен с выходом пятого элемента И, перQ вый вход последнего подключен к инйерсному выходу первого триггера и первому В1ходу третьего триггера, второй вход которого соединен с выходом четвертого элемента И, вторые входы .

C четвертого и пятого элементов И объединены и являются первым входом блока, вторым и Третьим входами и выходами которого являются первый и второй входы первого триггера и выходы второго и третьего триггеров.

Источники информации,

принятые во внимание при экспертизе

1. Патент Великобритании 2009984, кл.. G С 5/06, опублик. 1979.

5 2. Патент Великобритании

2009983, кл. G 4 С 5/06, рпублик. 1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1984 |

|

SU1156140A1 |

| Устройство для сопряжения электронно-вычислительной машины с накопителями на магнитных носителях | 1983 |

|

SU1156082A1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Устройство для поиска информации в накопителе на магнитных дисках | 1982 |

|

SU1117652A1 |

| Многоканальный преобразователь код-частота | 1985 |

|

SU1267621A1 |

| Устройство для контроля трассировки и воспроизведения информации о прокладке кабельной трассы | 1984 |

|

SU1238106A1 |

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1562921A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

Авторы

Даты

1982-10-07—Публикация

1981-03-11—Подача