Изобретение относится к вычислительной технике, в частности к запоминаюьдам устройствам.

Известны резервированные запоминающие устройства 1,2.

Известно устройство, -содержащее блок выборки адресов, основные одноразрядные блоки йамяти, шины записи и управления, резервный одноразрядный блок памяти, эле мент НЕ, элементыИ, ИЛИ, логический блок l .

Недостатком этого устройства является низкая надежность.

Наиболее к предложенному по техническо решению является резервированное запоминающее устройство, содержащее рабочие блоки памяти, один резервный блок памяти, суг-яиировйния, группы схем И, блркй контроля по модулю два, коммутаторы, блок формирования сигнала неисправности, генератор тактовых импульсов, причем информационные выходы рабочих блоков памяти подключены к первым входам коммутаторов, первым входам .элемейтов И Первой, группы и одним из вхо дов блоков контроля по модулю два, другие входы КОТОЕИХ соединены с . контрольными выходами блоков памяти, а выходы подключены ко вторым входам соответствующих элементов И первой группы и управляющим входам соответствующих коммутаторов, выхо,ды которых подключены к первым входам соответствующих элементов И втрой группы, выходы которых являютСя выходами устройства, а вторые |входы подключены к выходу генератора тактовых импульсов и первому , входу блока форшгрования сигнала нисправности, вторые входы которого подключены к:.вторым входам комг.5утаторов и выходам блока суммирования входы которого подключены к выходам соответствуювдах элементов И первой ГРУППЫ и йыходам резервно1Х блока памяти i Z.

-1. ,

Недостаткам прототипа являются низкая надежность, обусловленная тем, что применение блоков контре ля по модулю два не позволяет обнаруживать ошиб1ш , .кратные двум, в рабочих блоках памяти, а также низкое быстродействие вследствие временных затрат на работу блоков контроля по модулю, неполного испол зования информации рабочих блоков памяти {наличие в них контрольных разрядов), выдачи из устройет-ва сигналов;неисправности как при сбоях, так и при выявленных ранее отказах в ячейках рабочих блоков памяти так как при этом требуется повторное обращение к памяти.

Цель изобретения - повышение быстродействия и надежности устройства.

Поставленная цель достигается тем, что в резервированное запоминающее устройство, содержащее основные блоки памяти, выходы которых подключены к одним из входов комзчутаторов и одним из входов элементов И первой группы, выходы которых 0 подключены к одним из входов сумматора по модулю два, другой вход.которого соединен с выходом резервного блока памяти, а. выход - с другими входами коммутаторов и первым ;

5 входом формирователя сигнала неиспг. разности, второй вход которого и пер-; вые входы элементов И второй группы подключены к выходу генератора -тактовых импульсов, причем выходы ком0 гЛУтаторов соединены с вторыми входами элементов И второй группы, выходы которых являются информационны- , ми В1лходами устройства, введены до. полнительный блок памяти и первый

5 дешифратор, вход которого подключен к вы-ходу дополнительного блока памяти, а одни из выходов соединены с другими входами элементов И первой группы и управляющими входами коммуQ таторов причем другой выход пер.вого дешифратора подключен к третьему входу фо мирователя сигнала неисправности, выход которого является контрольным выходом устройства.

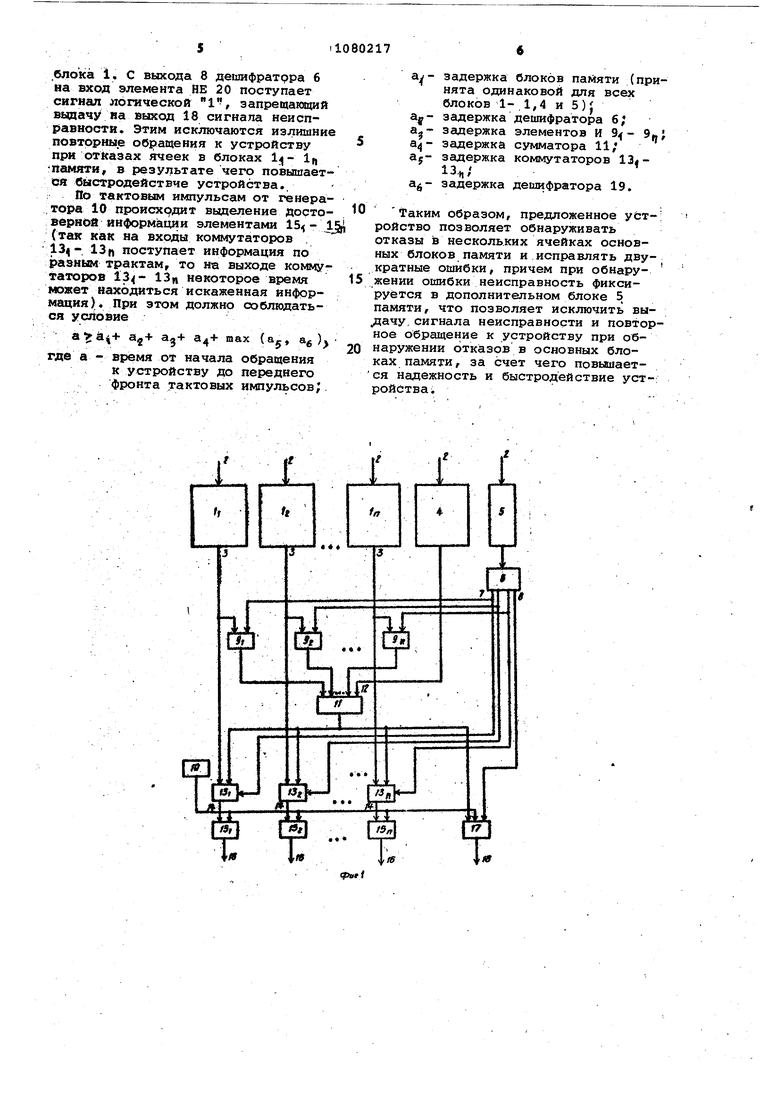

Формирователь сигнала неисправности содержит второй дешифратор, выход которого подключен к первому входу элемента И, , второй вход кото- . рого соединен с выходом элемента . НЕ, причем вход второго дешифратора,

0 третий вход элемента И и вход элемента НЕ являются соответственно первым/ вторым и третьим входами формирователя, ВЕЛХОДОМ которого является выход элемента И.

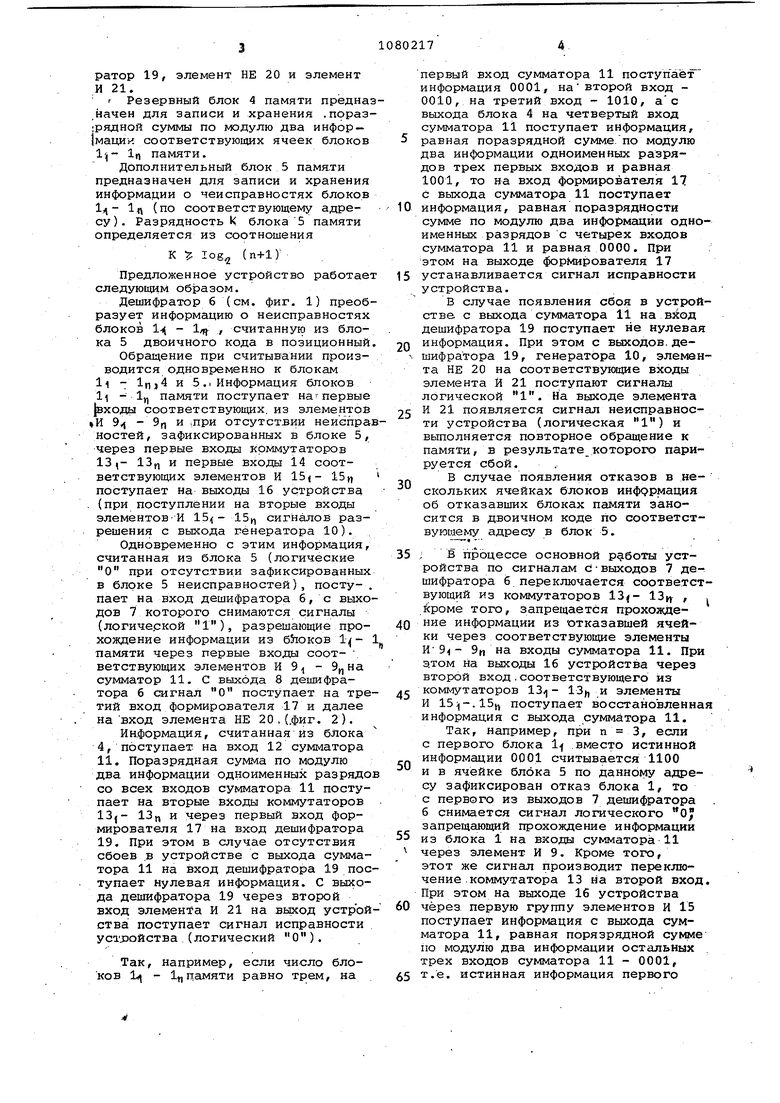

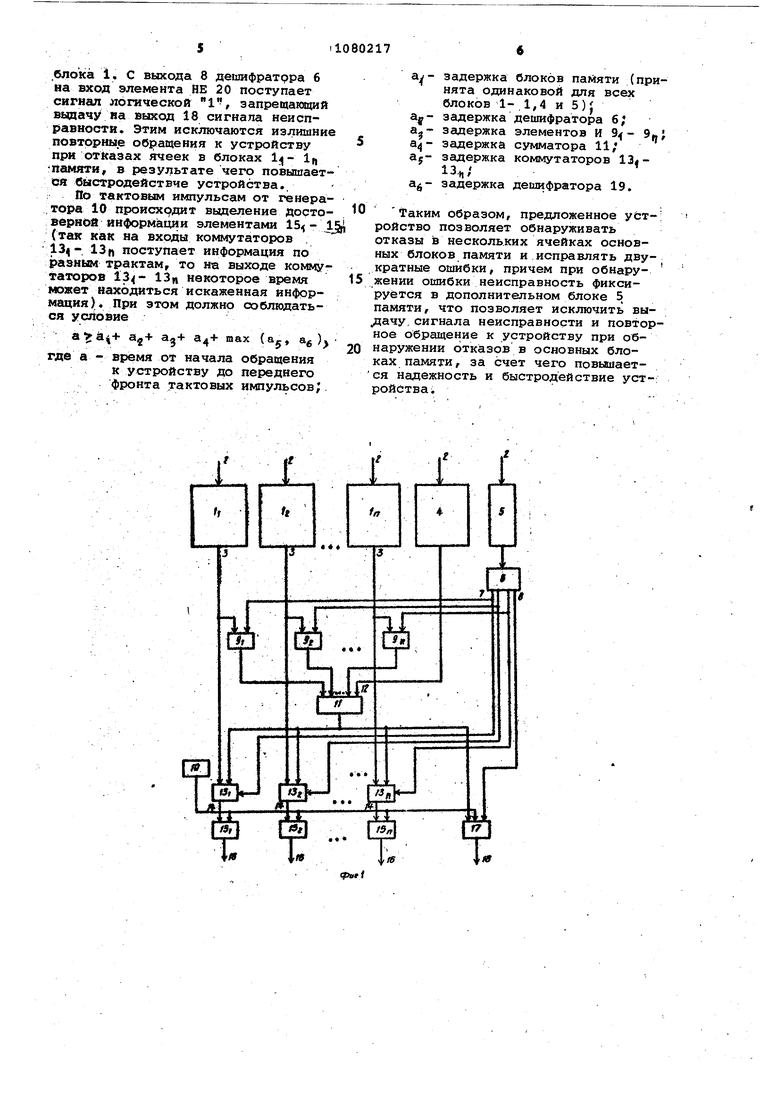

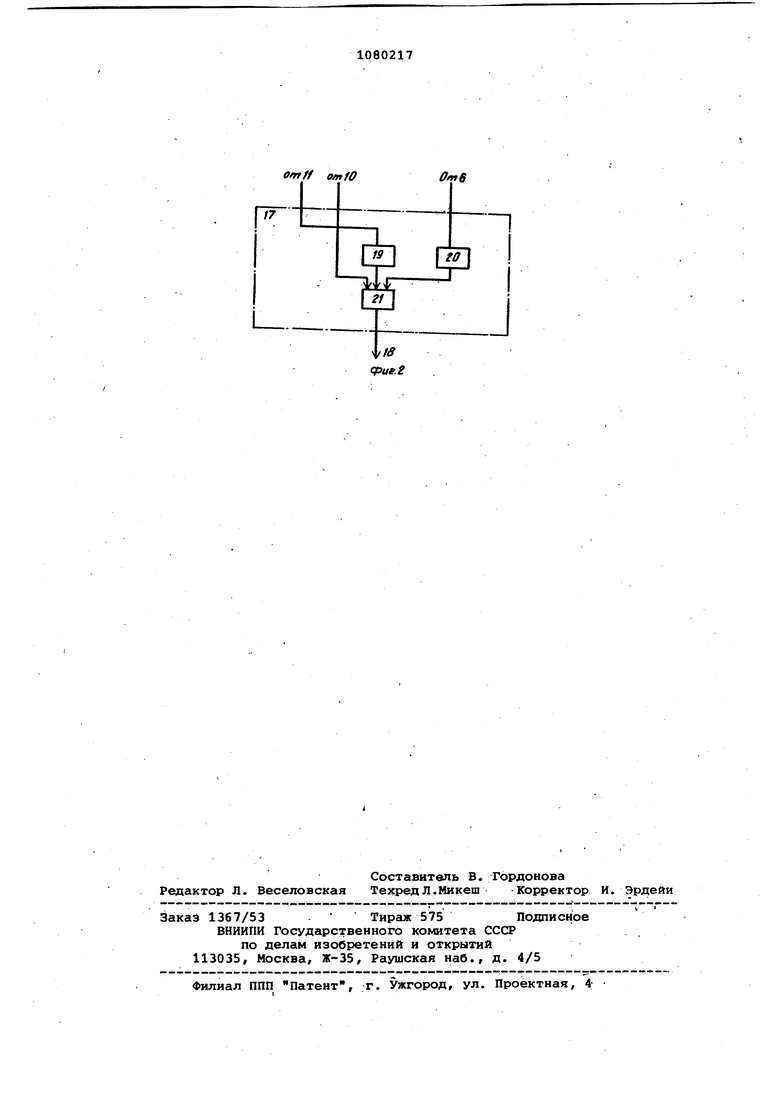

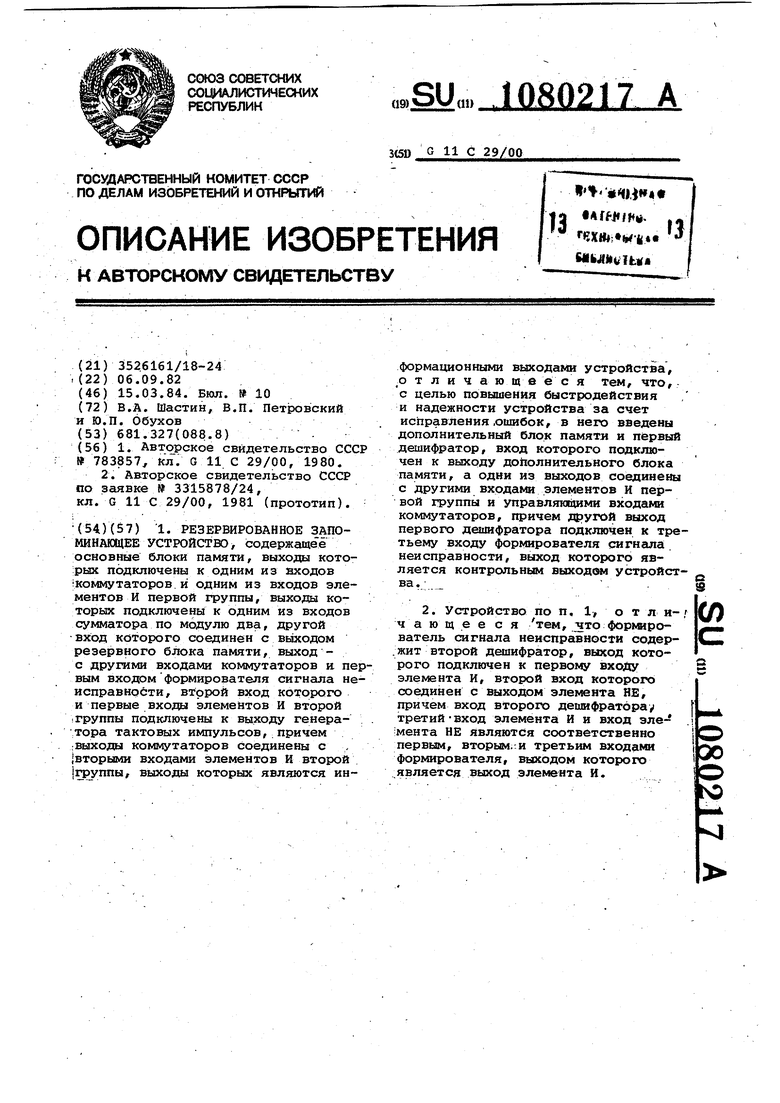

5 На фиг. 1 приведена функциональная схема предложенного устройства на фиг. 2 - функциональная схема формирователя сигнала неисправности.

0 Предложенное устройство содержит (фиг. 1) основные блоки 1 - 1 па|Мяти (где п 5,1 - целое число) с ад|ресными входами 2 и выходами 3, резервный блок 4 памяти, дополни5 (тельный блок 5 памяти, первый дешифратор б с выходами 7 и выходом 8, первую группу элеме.нтов И 9. - 9f), генератор 10 тактовых илшульсов, сумматор 11 по модулю два с входом 12,

л коммутаторы 13 13f| с выходами 14, вторую группу элементов И 15(f - 15 п с вьзходами 16 и формирователь 17 сигнала неисправности с выходом 18.

Формирователь сигналов неисправ5 йости содержит (фиг, 2) дешифратор 19, элемент НЕ 20 и элемент И 21.

Резервный блок 4 памяти предназначен для записи и хранения .поразядной суммы по модулю два инфор- мации соответствующих ячеек блоков Ifl памяти.

Дополнительный блок 5 памати предназначен для записи и хранения информации о неисправностях блоков 1д- 1ц (по соответствующему адресу). Разрядность К блока 5 памяти определяется из соотношения

К log (п+1)

Предложенное устройство работает следующим образом.

Дешифратор 6 (см. фиг. 1) преобразует информацию о неисправностях блоков 1ч( - 1/ff , считанную из блока 5 двоичного кода в позиционный.

Обращение при считывании производится одновременно к блокам ll - Inj4 и 5.. Информация блоков ll - ly, памяти поступает на первые входы соответствующих, из элементов И 9 9п и лри отсутствии неисправностей, зафиксированных в блоке 5, через первые входы коммутаторов 13,- и первые входы 14 соответствующих элементов И 15ц поступает на выходы 16 устройства (при поступлении на вторые входы элементов-И 15 - 15, сигналов разрешения с выхода генератора 10).

Одновременно с этим информация, считанная из блока 5 (логические О при отсутствии зафиксированных в блоке 5 неисправностей), посту-, пает на вход дешифратора б, с выходов 7 которого снимаются сигналы (логической 1), разрешающие прохождение информации из блоков 1ц - 1 памяти через первые входы соот- ветствующих элементов И 9 - 9„на сумматор 11. С выхода 8 дешифратора 6 сигнал О поступает на третий вход формирователя 17 и далее навход элемента НЕ 20,(.фиг. 2).

Информация, считанная из блока 4, поступает на вход 12 сумматора 11. Поразрядная сумма по модулю два информации одноименных разрядов со всех входов сумматора 11 поступает на вторые входы ком2У1утаторов 13J- 13п и через первый вход формирователя 17 на вход дешифратора 19. При этом в случае отсутствия сбоев в устройстве с выхода сумматора 11 на вход дешифратора 19 поступает Нулевая информация. С выхода дешифратора 19 через второй вход элемента И 21 на вькод устройства поступает сигнал исправности ycTjDoftcTBa (логический О).

Так, например, если число блоков 1, - Ifl памяти равно трем, на

первый вход сумматора 11 поступ а ёт информация 0001, на второй вход 0010, на третий вход - 1010, ас выхода блока 4 на четвертый вход сумматора 11 поступает информация,

равная поразрядной сумме.по модулю два информации одноименных разрядов трех первых входов и равная 1001, то на вход формирователя 17 с выхода сумматора 11 поступает

информация, равная поразрядности

сумме по модулю два информации одноименных разрядов с четырех входов сумматора 11 и равная 0000. При ; этом на выходе формирователя 17

устанавливается сигнал исправности устройства.

В случае появления сбоя в устройстве с выхода сумматора 11 на вз4од дешифратора 19 поступает не нулевая

информация. При этом с выходов.дешифратора 19, генератора 10, элемента НЕ 20 на соответствующие входы элемента И 21 поступают сигналы

На выходе элемента

логической

И 21 появляется сигнал неисправности устройства (логическая 1) и выполняется повторное обращение к памяти, в результате которогхэ парируется сбой.

В случае появления отказов в нескольких ячейках блоков инф9рмация об отказавших блоках памяти заносится в двоичном коде по соответствующему адресу в блок 5.

, в процессе основной работы устройства по сигналам с-выходов 7 дешифратора б переключается соответствующий из коммутаторов 13(- 13 , йроме того, запрещается прохождение информации из отказавшей ячейки через соответствующие элементы И94- 9п на входы сумматора 11. При этом на выходы 16 устройства через второй вход.соответствующего из

коммутаторов 13(, и элементы

И ISij-.lSj, поступает восстановленная информация с выхода сумматора 11. Так, например, п 3, если с первого блока 1 .вместо истинной информации 0001 считывается 1100 и в ячейке блока 5 по данному адресу зафиксирован отказ блока 1, то с первого из выходов 7 дешифратора 6 снимается сигнал логического О запрещающий прохождение информации

из блока 1 на входы сумматора 11 через элемент И 9. Кроме того, этот же сигнал производит переключение .коммутатора 13 на второй вход. При этом на выходе 16 устройства

через первую группу элементов И 15 поступает информация с выхода сумматора 11, равная порязрядной сумме по модулю два информации остальных трек входов сумматора 11 - 0001,

т.е. истинная информация первого блока 1. С выхода 8 дешифратора 6 на вход элемента НЕ 20 поступает сигнал логической 1, эапрецакхций вьщачу на выход 18 сигнала неисправности. Этим исключаются излишние повторные обращения к устройству при отказах ячеек в блоках 1ц Памяти, в результате чего повышается быстродействие устройства. По тактовым импульсам от генератора 10 происхрдит выделение достоверной информации элементами 15,( - 1 (так как на входы коммутаторов 13h поступает информация по разным трактам, то иа выходе коммутаторов 13(1 некоторое время может находиться искаженная информация ) При этом должно соблюдаться условие a -tн- шах 5 6 где а - время от начала обращения к устройству до переднего фронта тактовых импульсов;. а/- задержка блоков памяти (принята одинаковой для всех блоков 1- 1,4 и 5)J ay- задержка дешифратора б; задержка элементов И 9| - , задержка сумматора 11; ае- задержка коммутаторов задержка дешифратора 19. Таким образом, предложенное уЬт-; ройство позволяет обнаруживать отказы в нескольких ячейках основных блоков памяти и исправлять двукратные ошибки, причем при обнаружении ошибки неисправность фиксируется в дополнительном блоке 5 памяти, что позволяет исключить вы(ачу,сигнала неисправности и повторное обравдение к устройству при обнаружении отказов в основных блоках памяти, за счет чего повышается надежность и быстродействие уст-; ройства

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство | 1981 |

|

SU982086A1 |

| Резервированное запоминающее устройство | 1980 |

|

SU936034A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1070608A1 |

| Резервированное запоминающее устройство | 1979 |

|

SU881875A2 |

| Резервированное запоминающее устройство | 1981 |

|

SU983752A1 |

| Резервированное запоминающееуСТРОйСТВО | 1978 |

|

SU803014A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1076953A1 |

| Резервированное запоминающее устройство | 1987 |

|

SU1510012A1 |

| РЕЗЕРВИРОВАННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С КОРРЕКЦИЕЙ ОШИБОК В ДУБЛИРУЕМЫХ КАНАЛАХ | 2022 |

|

RU2826990C2 |

| Резервированное запоминающее устройство | 1986 |

|

SU1387048A2 |

1. РЕЗЕРВИРОВАННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТЮ>& содержаще'ё основные блоки памяти, выхода] которых подключены к одним из входов iкоммутаторов и одним из входов элементов И первой группы, выходы которых подключены к одним из входов сумматора по модулю два, другой вход которого соединен с выходом резервного блока памяти, выход - с другими входами коммутаторов и первым входом формирователя сигнала неисправности, второй вход которого и первые входы элементов И второй .группы подключены к выходу генератора тактовых импульсов,.причем гвыходы коммутаторов соединены с , |вторыми входами элементов И второй |груш1ы, выхода! которых являются информационными выходами устройства, о т л и ч а ю щ в е с я тем, что, 'с целью повышения быстродействия и надежности устройства за счет исправления .ошибок, в него введены дополнительный блок памяти и первый дешифратор, вход которого подключен к выходу дополнительного блока памяти, а одни из выходов соединены с другими входами элементов И первой группы и управляюощмн входами коммутаторов, причем д^)угой выход первого дешифратора подключен к третьему входу формирователя сигнала: неисправности, выход которого является контрольным выходом устройства. ;,_, • . . .2. Устройство по п. 1, о т л и-г чающее с я /тем, что форидаро- ватель сигнала неисправнос±и содер-.жит второй дешифратор, выход которого подключен к первому входу элемента И, второй вход которого соединен с выходом элемента НЕ, причем вход второго дешифраторау третий-вход элемента И и вход эле-:мента НЕ являются соответственно первым, вторым.ги третьим входами формирователя, выходом которого является выход элем&нта И.i(Л

от ft omfO

Отб

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство с автоматическим восстановлением работоспособности | 1979 |

|

SU783857A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Авторское свидетельство СССР по заявке » 3315878/24, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-03-15—Публикация

1982-09-06—Подача