(5) УСТРОЙСТВО для ПОДСЧЕТА ЧИСЛА ДВОИЧНЫХ ЕДИНИЦ

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное устройство для возведения в квадрат | 1988 |

|

SU1608653A1 |

| УСТРОЙСТВО ДЛЯ КОНВЕЙЕРНОГО СУММИРОВАНИЯ ЧИСЕЛ ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ | 2023 |

|

RU2805939C1 |

| Сумматор последовательного действия | 1989 |

|

SU1689945A2 |

| Сумматор по модулю три | 1991 |

|

SU1797109A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Устройство для сложения в избыточной двоичной системе | 1978 |

|

SU860064A2 |

| Устройство для преобразования двоичного кода в двоично-десятичношестидесятиричный код | 1976 |

|

SU599263A1 |

| Универсальное суммирующее устройство | 1990 |

|

SU1786484A1 |

| УСТРОЙСТВО ГРУППОВОЙ СТРУКТУРЫ ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП НУЛЕВЫХ И ЕДИНИЧНЫХ БИТ И ОПРЕДЕЛЕНИЕ ИХ КОЛИЧЕСТВА | 2018 |

|

RU2680762C1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

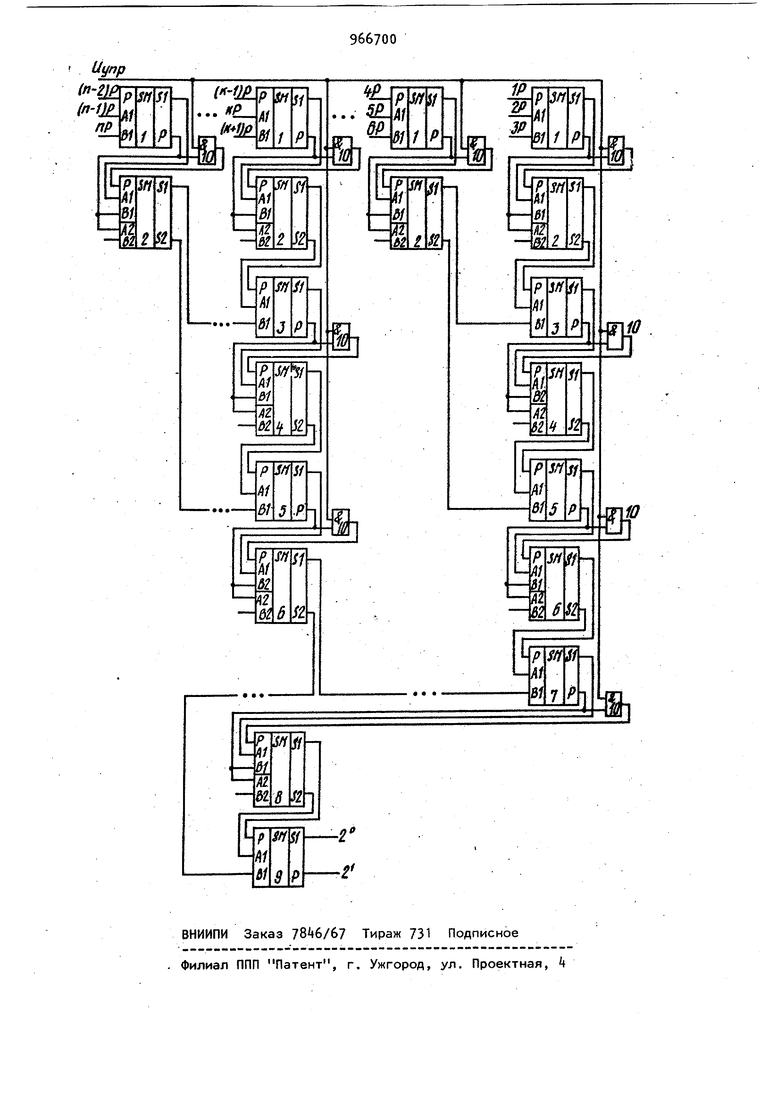

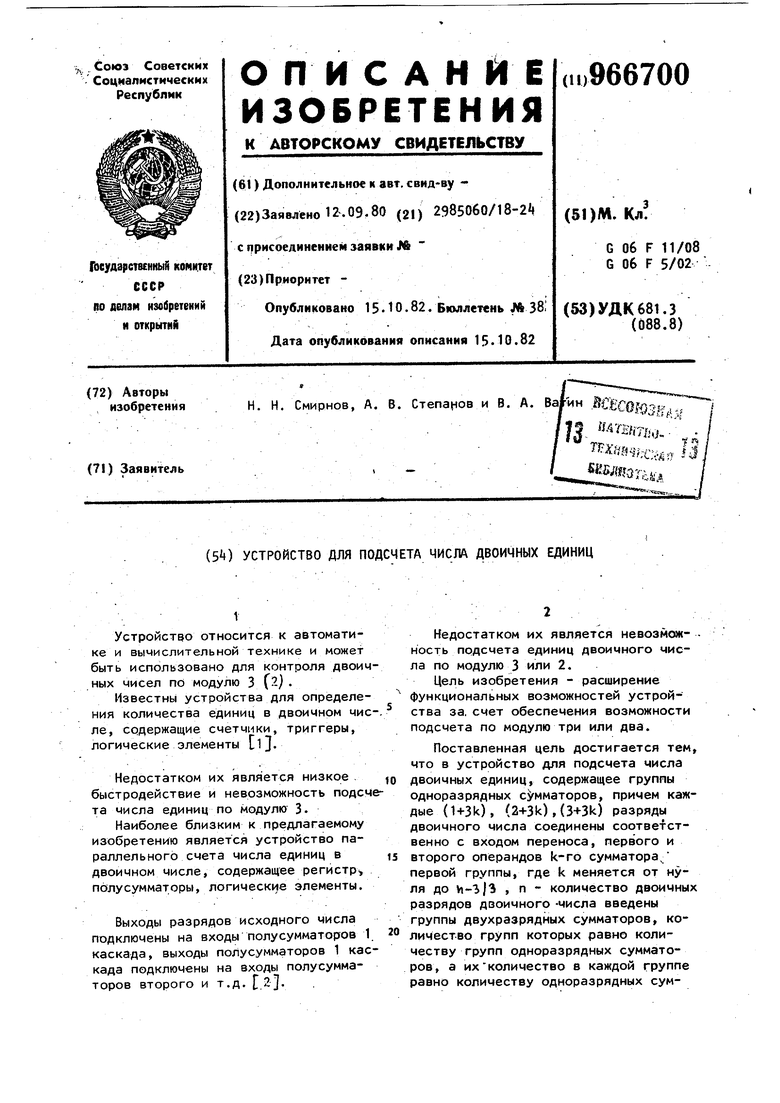

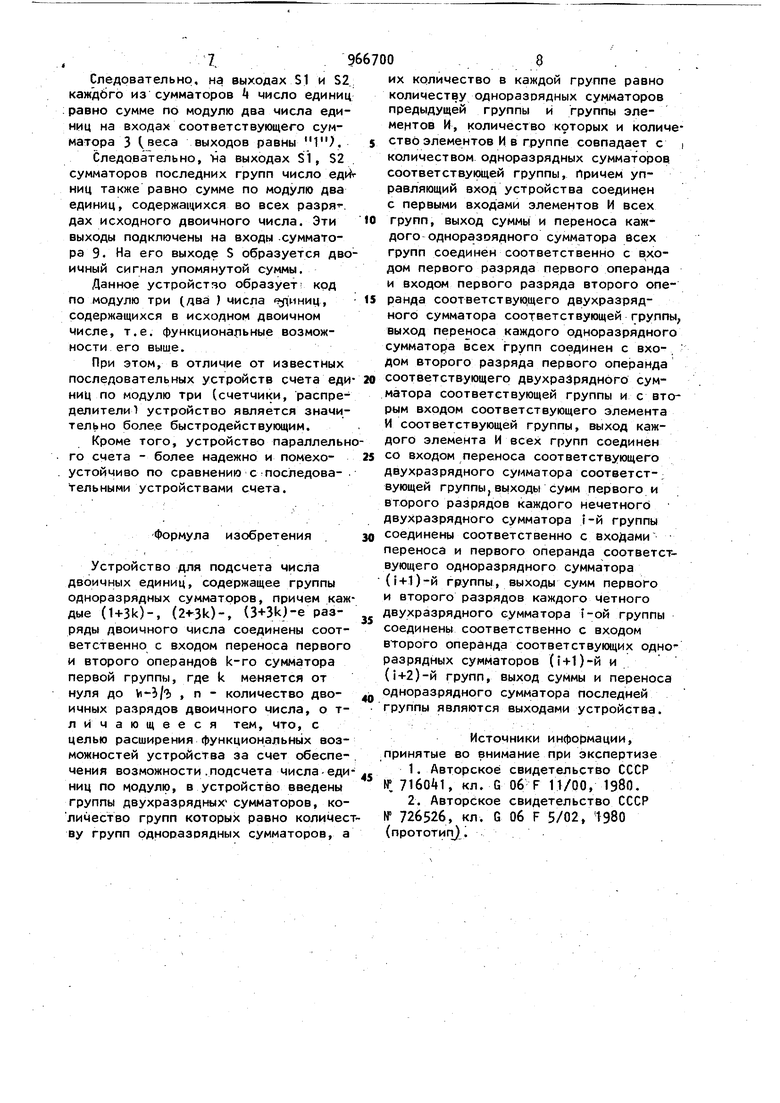

Устройство относится к автоматике и вычислительной технике и может быть использовано для контроля двоич ных чисел по модулю 3 С-) Известны устройства для определения количества единиц в двоичном чис ле, содержащие счетчики, триггеры, логические элементы lj. Недостатком их является низкое быстродействие и невозможность подсч та числа единиц по модулю 3. Наиболее близким к предлагаемому изобретению является устройство параллельного счета числа единиц в двоичном числе, содержащее регистр полусумматоры, логические элементы. Выходы разрядов исходного числа подключены на входы полусумматоров 1 каскада, выходы полусумматоров 1 кас када подключены на входы полусумматоров второго и т.д. f 2. Недостатком их является невозмож- ность подсчета единиц двоичного числа по модулю 3 или 2. Цель изобретения - расширение функциональных возможностей устройства за. счет обеспечения возможности подсчета по модулю три или два. Поставленная цель достигается тем, что в устройство для подсчета числа двоичных единиц, содержащее группы одноразрядных сумматоров, причем каждые {l+3k), (2+3k),(3+3k) разряды двоичного числа соединены соответственно с входом переноса, первого и второго операндов k-ro сумматора первой группы, где k меняется от нуля до Vi-l|3 , п - количество двоичных разрядов двоичного -числа введены группы двухразрядных сумматоров, количество групп которых равно количеству групп одноразрядных сумматоров, а ихколичество в каждой группе равно количеству одноразрядных сум3 9 маторов предыдущей группы сумматоров и группы элементов И, количество которых и количество элеме1 гов Ивгруппе совпадает с количеством одноразрядных сумматоров соответствующей группы, причем управляющий вход устройства соединен с первыми входами элементов И всех групп, выход суммы и переноса каждого одноразрядного сумматора всех |Групп соединен соответственно с входом первого разряда первого операнда и входом первого разряда второго операнда соответствующего двухразрядного сумматора соответствующей группы, выход переноса каждого одноразрядного сумма- . тора всех групп соединен с входом второго разряда первого операнда соответствующего двухразрядного сумматора соответствующей группы и с вторым входом .соответствующего элемента И соответствующей группы, выход каждого элемента М вбех груфп со динен с входом переноса соответствую щего двухразрядного сумматора соответствующей группы, выходы сумм первого и второго разрядов каждого нечетного двухразрядного сумматора i-й группы соединены соответственно с входами переноса и первого операнда соответствующего одноразрядного сумматора ((+Т)-ой группы, выходы сумм первого и второго разрядов каждого четного двухразрядного сумматора i-й группы соединены сбответствен но с входом второго операнда соответ ствующих одноразрядных сумматоров (|Н-1}-й и (1+2)-и групп, выход суммы и переноса одноразрядного сумматора последней группы являются выходами устройства. На чертеже изображена функциональ ная схема устройства. , Устройство содержит одноразрядные сумматоры 1 первой группы, двухразря Hbie сумматоры 2 первой группы двухразрядных сумматоров, одноразрядные сумматоры /3 второй группы, двухразСумматор 1

Входы

Выходы А1 В1 S1 Р О О

.0 О

1

1 О

О 1

Сумматор 2

ВходыВыходы

Р А1 В1 А2 В2 S1 5,2

000000О

010-0 01 О 010001 О 0 рядные сумматоры Ч второй группы, одноразрядные сумматоры 5 третьей группы, двухразрядные сумматоры 6 третьей группы, одноразрядные сумматоры 7 четвертой группы, двухразрядные сумматоры а четвертой группы, одноразрядный сумматор 9 пятой группы, группы элементов И 10. Входы А1, В1, Л2, В2, S1, 52 и Р, соответственно, означают В)од первого разряда первого операнда, вход первого разряда второго операнда, вход второго разряда первого опер1анда, вход .второго разряда второго операнда, первый разряд суммы, второй разряд суммы й перенос. На входы А1, В1, Р сумматоров 1 подключен выходы разрядов исходного числа. Выходы S1 сумматоров 1 подключены на входы А 1 сумматоров 2. Выходы Р сумматоров 1 подключены на входы 81 и А1 сумматоров 2. Выходы S1 и S2 сумматоров 2 подключены на входы Р, А1, В1 сумматоров 3, а также сумматоров 5 и т.д. Выходы двух последних сумматоров подключены на входы сумматора 9. На первые входы всех элементов И 10 подключен управляющий вход устройства. На вторые входы всех элементов И 10 подключены выходы переносов сумматоров 1,3... Устройство работает следующим образом. В режиме счета числа единиц по модулю 3 на управляющий вход устройства подается нулевой управляющий сигнал .у. На выходах каждого из сумматоров 1 образуются двоичные коды (с весами S1 , Р - 2) числа единиц, содержащихся в трехразрядных группах, на которые разбито исходное число и которые подключены на входы сумматоров 1. На входах S1, S2 каждого из сумматоров 2 (как видно из схемы} вырабатываются следующие сигналы в зависимости от сигналов на входах. Сумматор 1 Выходы 01 О 1 1 1О О 1 Таким образом, на выходах S1 и S2 .каждого из сумматоров 2 число единиц равно сумме по модулю три числа единиц на входах соответствующего сумматора 1, т.е. О, 1 или 2,(веса выходов S1 и S2 равны 1). Выходы S1, S2 сумматоров 2, сгруппированные по три, подключены на входы сумматоров 3, Выходы 51, Р сумматоров 3 подключены аналогично сумматорам 1 на входы сумматоров 4. Следовательно, на выходах S1 и S каждого из сумматоров k число единиц равно сумме по модулю 3 числа единиц на входах соответствующего сумматора 3 (веса выходов равны 1). Таким образом, на входах S1, S2 сумматоров последних каскадов число еди ниц также равно сумме по модулю 3 ед ниц, содержащихся, во всех разрядах Сумматор 1 Выходы Входы Р А1 В1 S1 Р 000 00-1 1 1 1 1 1 Таким образом, на выходах S1 и S2 каждого из сумматоров 2 число единиц равно сумме по модулю два числа на входах соответствующего сумматора 1, т.е. О, 1 или 2 (веса выходов S1 и 52 равны 1). Сумматор 2 ВходыВыходы 001 1 01 1 О 1 О О 10 1 О 00 1 1 О 1 Т 00 1 101 1 0111 00 О исходного двоичного числа . Эти выходы подключены на входы сумматора 9. На его выходах S и Р образуется двоичный код упомянутой суммы. В режиме счета числа единиц по модулю два на элементы И 10 подается единичный управляющий сигнал. На выходах S1, Р каждого из сумматоров 1 образуется двоичный код (с весами S1 - 1, Р - 2) числа единиц, содержащихся в трехразрядных группах, на которые разбито исходное число и которые подключены на входы сумматоров 1. На выходах S1, S2 каждого из сумматоров 2 вырабатываются следующие сигналы в зависимости от сигналов на входе (сигнал переноса сумматоров 1 проходит через элементы И 10 без изменения). Сумматор 2 Входы Выходы Р А1 В1 А2 В2 S1 S2 0000000 010-00 1 О 1011000 1011000 1 1 i; 1 . 010 Выходы 51 и 52 суйматоров 2, сгрупг ированные по три, подключены на вхоы сумматоров 3, выходы51, Р суматоров 3 подключены аналогично умматорам 1 на входы сумматоов Ц. I9 Следовательно, на выходах SI и S2 каждого из сумматоров k число единиц равно сумме по модулю два числа единиц на входах соответствующего сумматора 3 (, веса выходов равны 1). Следовательно, на выходах S1, 52 сумматоров последних групп число едй ниц также равно сумме по модулю два единиц, содержащихся во всех разря. дах исходного двоичного числа. Эти выходы подключены на входы сумматора 9. На его выходе S образуется дво ичный сигнал упомянутой суммы. Данное устройство образует; код по модулю три (два ) числа , содержащихся в исходном двоичном числе, т.е. функциональные возможности его выше. При этом, в отличие от известных последовательных устройств счета еди ниц по модулю три (счетчики, распределителиТ устройство является значительно более быстродействующим. Кроме того, устройство параллельн го счета - более надежно и помехоустойчиво по сравнению с последовательными устройствами счета. Формула изобретения Устройство для подсчета числа двоичных единиц, содержащее группы одноразрядных сумматоров, причем каж дые (1+3k)-, (2i-3k)-, (3+3k)-e разряды двоичного числа соединены соответственно с входом переноса первого и второго операндоб k-ro сумматора первой группы, где k меняется от нуля до ) , п - количество двоичных разрядов двоичного числа, о тличающееся тем, что, с целью расширения функциональнь1х возможностей устройства за счет обеспечения возможности .подсчета числа-еди ниц по модулю, в устройство введены группы двухразрядных сумматоров, количество групп которых равно количес ву групп одноразрядных сумматоров, а ,8 0 их количество в каждой группе равно количеству одноразрядных сумматоров предыдущей группы и группы элементов И, количество К9торых и количество элементов И в группе совпадает с i количеством одноразрядных сумматоров соответствующей группы, причем управляющий вход устройства соединен с первыми входами элементов И всех групп, выход суммы и переноса каждого одноразоядного сумматора всех групп соединен соответственно с входом первого разряда первого операнда и входом первого разряда второго операнда соответствуедего двухразрядного сумматора соответствующей группы, выход переноса каждого одноразрядного сумматора всех групп соединен с вхо-. дом второго разряда первого операнда соответствующего двухразрядного сумматора соответствующей группы и с вторым входом соответствующего элемента И соответствующей группы, выход каждого элемента И всех групп соединен со входом переноса соответствующего двухразрядного сумматора соответст-; вующей группы,вцходы сумм первого и второго разрядов каждого нечеткого двухразрядного сумматора 1-й группы соединены соответственно с входами переноса и первого операнда соответствующего одноразрядного сумматора (+1)-й группы, выходы сумм первого и второго разрядов каждого четного двухразрядного сумматора 1-ой группы соединены соответственно с входом второго операнда соответствующих одно разрядных сумматоров ()-й и (1+2)-й групп, выход суммы и переноса одноразрядного сумматора последней группы являются выходами устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР №716041, кл. G Об F 11/00, 1980. 2.Авторское свидетельство СССР № 726526, кл. G Об F 5/02 1Э80 (прототип).

Авторы

Даты

1982-10-15—Публикация

1980-09-12—Подача