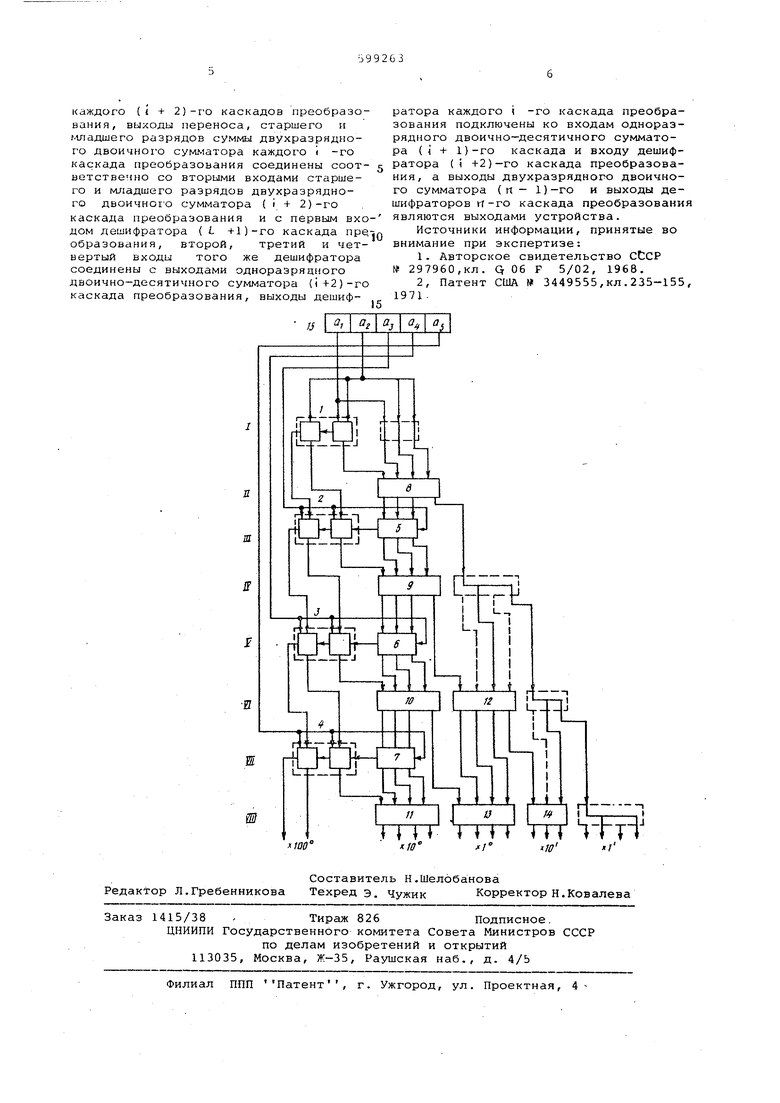

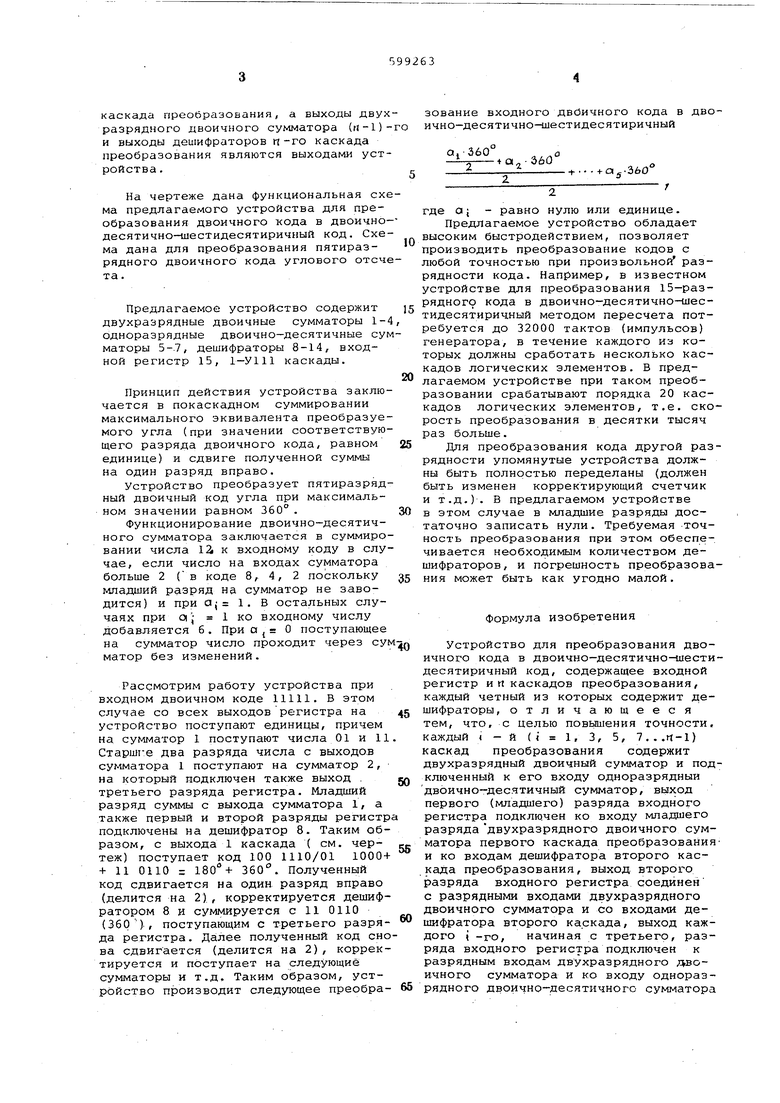

каскада преобразования, а выходы двухразрядного двоичного сумматора Cri-l)-ro и выходы дешифраторов п-го каскада преобразования являются выходами устройства.J На чертеже дана функциональная сх ма предлагаемого устройства для преобразования двоичного кода в двоично десятично-шестидесятиричный код. Схе ма дана для преобразования пятиразрядного двоичного кода углового отсч та . Предлагаемое устройство содержит двухразрядные двоичные сумматоры 1одноразрядные двоично-десятичные су маторы 5-7, дешифраторы 8-14, входной регистр 15, 1-У111 каскады. Принцип действия устройства заключается в покаскадном суммировании максимального эквивалента преобразуе мого угла (при значении соответствую щего разряда двоичного кода, равном единице) и сдвиге полученной суммы на один разряд вправо. Устройство преобразует пятиразряд ный двоичный код угла при максимальном значении равном 360°. Функционирование двоично-десятичного сумматора заключается в суммиро вании числа I2i к входному коду в слу чае, если число на входах сумматора больше 2 (в коде 8, 4, 2 поскольку младший разряд на сумматор не заводится) и при а( 1. В остальных случаях при О(; 1 ко входному числу добавляется 6. При а О поступающее на сумматор число проходит через су матор без изменений. Рассмотрим работу устройства при входном двоичном коде 11111. В этом случае со всех выходоврегистра на устройство поступают единицы, причем на сумматор 1 поступают числа 01 и 11 Старшт-е два разряда числа с выходов сумматора 1 поступают на сумматор 2, на который подключен также выход . третьего разряда регистра. Младший разряд суммы с выхода сумматора 1, а также первый и второй разряды регистр подключены на дешифратор 8. Таким образом, с выхода 1 каскада ( см. чертеж) поступает код 100 1110/01 1000+ + 11 ОНО 360°. Полученный код сдвигается на один разряд вправо (делится на 2), корректируется дешифратором 8 и суммируется cllOllO (360), поступающим с третьего разряда регистра. Далее полученный код сно ва сдвигается (делится на 2), корректируется и поступает на следующие сумматоры и т.д. Таким образом, устройство производит следующее преобразевание входного двоичного кода в двоично-десятично-шестидесятиричный

а.-ЗбО о

где О} - равно нулю или единице. Предлагаемое устройство обладает высоким быстродействием, позволяет производить преобразование кодов с любой точностью при произвольной разрядности кода. Например, в известном устройстве для преобразования 15-разРЯДНОГ9 кода в двоично-десятично-шестидесятиричный методом пересчета потребуется до 32000 тактов (импульсов) генератора, в течение каждого из которых должны сработать несколько каскадов логических элементов. В предлагаемом устройстве при таком преобразовании срабатывают порядка 20 каскадов логических элементов, т.е. скорость преобразования в десятки тысяч раз больше. Для преобразования кода другой разрядности упомянутые устройства должны быть полностью переделаны (должен быть изменен корректирующий счетчик и т.д.). В предлагаемом устройстве в этом случае в младшие разряды достаточно записать нули. Требуемая точность преобразования при этом обеспечивается необходимым количеством дешифраторов, и погрешность преобразования может быть как угодно малой. Формула изобретения Устройство для преобразования двоичного кода в двоично-десятично-шестидесятиричный код, содержащее входной регистр и« каскадов преобразования, каждый четный из которых содержит дешифраторы, отличающееся тем, что, с целью повышения точности, каждый ( -и ( 1, 3, 5, 7...I1-1) каскад преобразования содержит двухразрядный двоичный сумматор и подключенный к его входу одноразрядный двоично-десятичный сумматор, выход первого (младшего) разряда входного регистра подключен ко входу младшего разряда двухразрядного двоичного сумматора первого каскада преобразования и ко входам дешифратора второго каскаД;а преобразования, выход второго разряда входного регистра соединен с разрядными входами двухразрядного двоичного сумматора и со входами дешифратора второго каскада, выход каждого i -го, начиная с третьего, разряда входного регистра подключен к разрядным входам двухразрядного двоичного сумматора и ко входу одноразрядного двоично-десятичного сумматора

каждого (J 2)-го каскадов преобразования, выходы переноса, старшего и младшего разрядов суммы двухразрядного двоичного сумматора каждого 1 -го каскада преобразования соединены соответствечно со вторыми входами старшего и младшего разрядов двухразрядного двоичного сумматора ( i + 2)-го каскада преобразования и с первым входом дешифратора ( L +1)-го каскада npe. образования, второй, третий и четвертый входы того же дешифратора соединены с выходами одноразряцЕюго двоично-десятичного сумматора (i+2)-ro

каскада преобразования, выходы дешифратора каждого ( -го каскада преобразования подключены ко входам одноразрядного двоично-десятичного сумматора ( i + 1)-го каскада и входу дешифратора (i +2)-го каскада преобразования, а выходы двухразрядного двоичного сумматора (п - 1)-го и выходы дешифраторов и-го каскада преобразовани являются выходами устройства.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство CtCP № 297960,кл. Q 06 Р 5/02, 1968.

2,Патент США № 3449555,кл.235-155 19VI

Авторы

Даты

1978-03-25—Публикация

1976-08-09—Подача