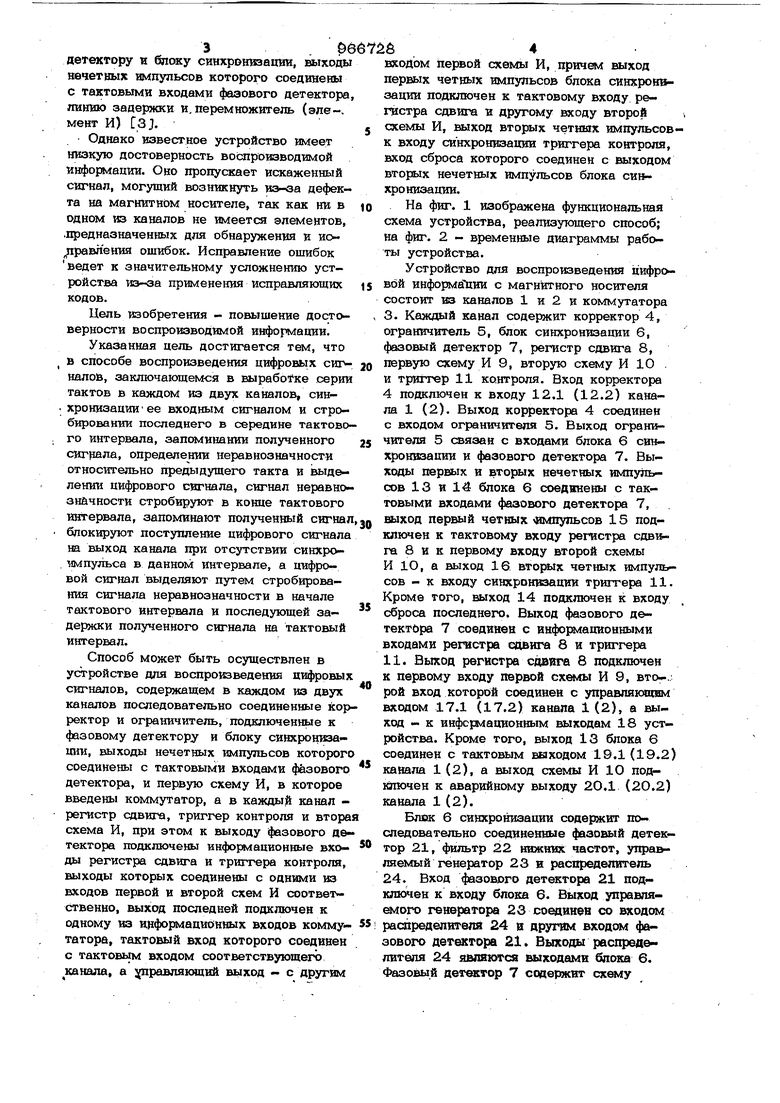

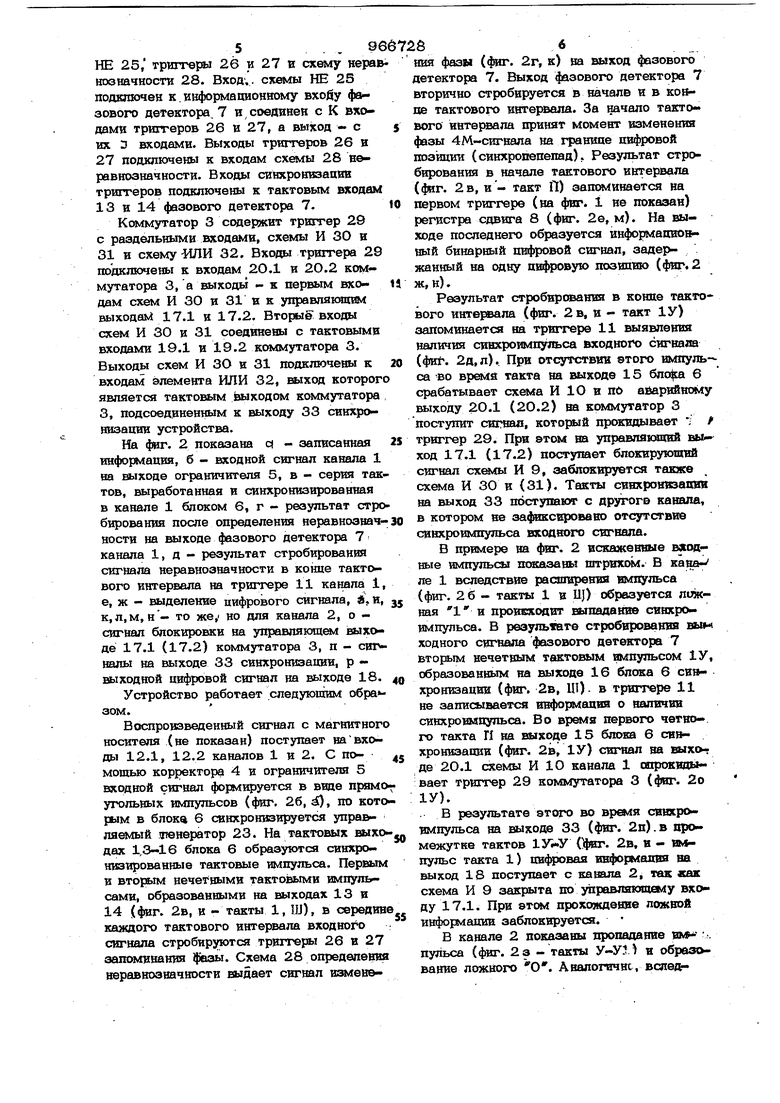

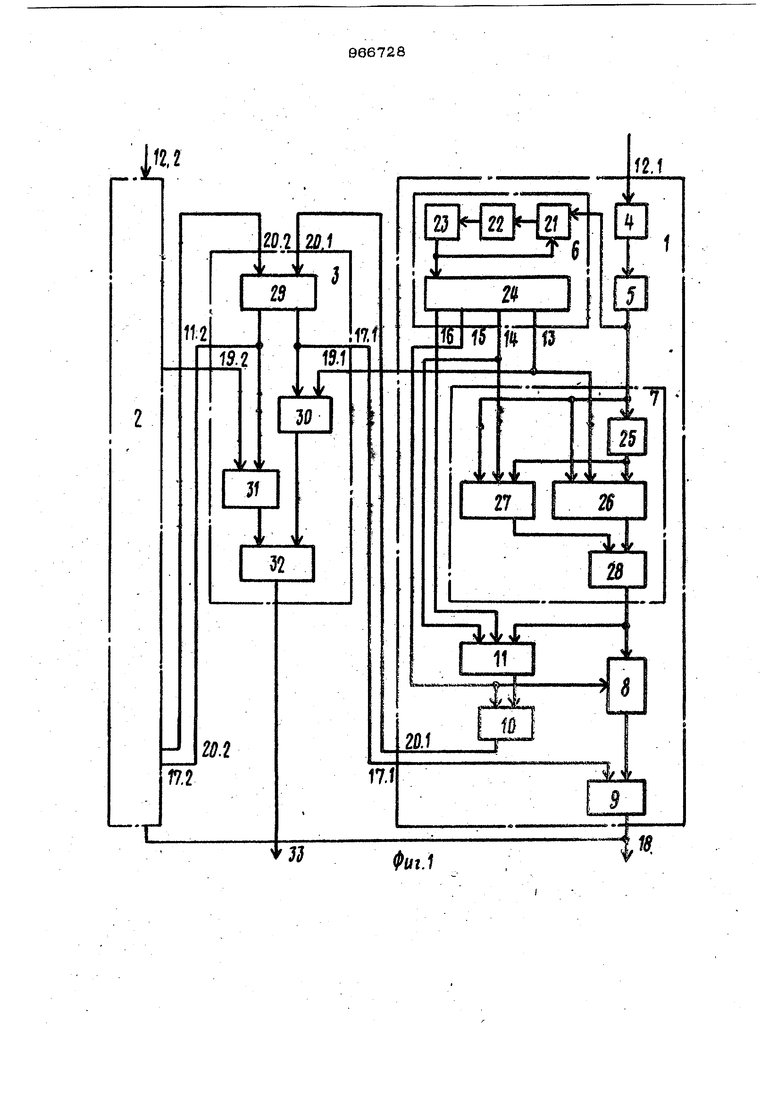

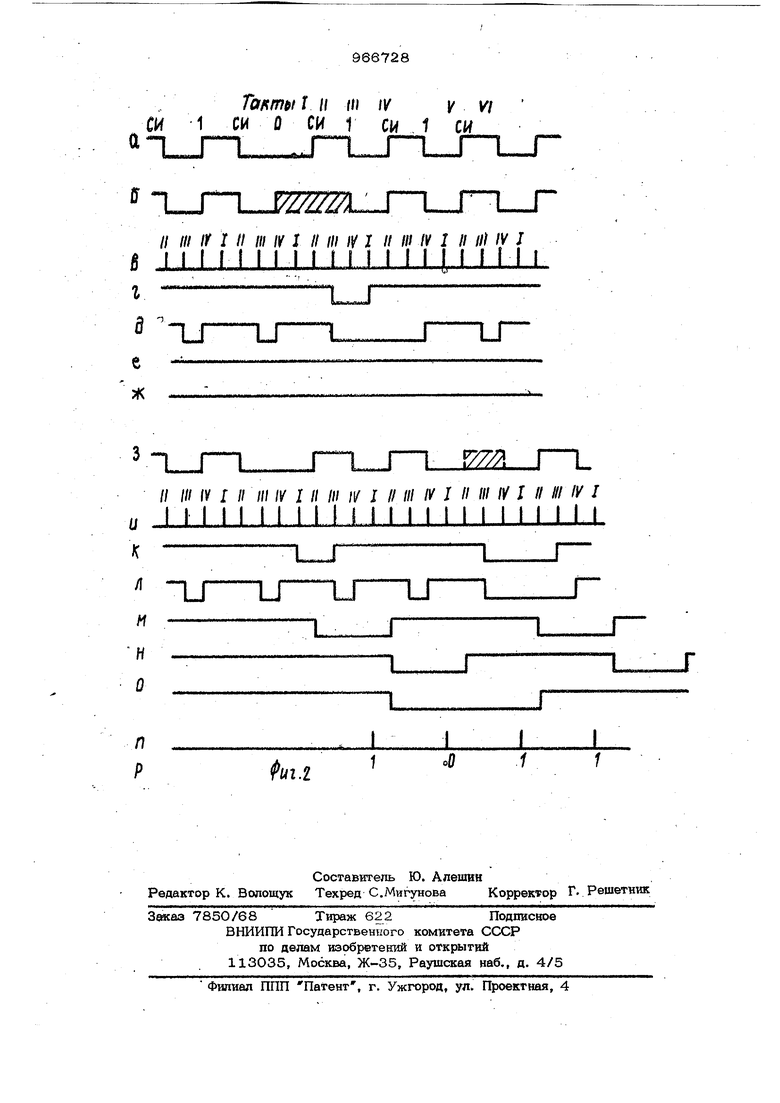

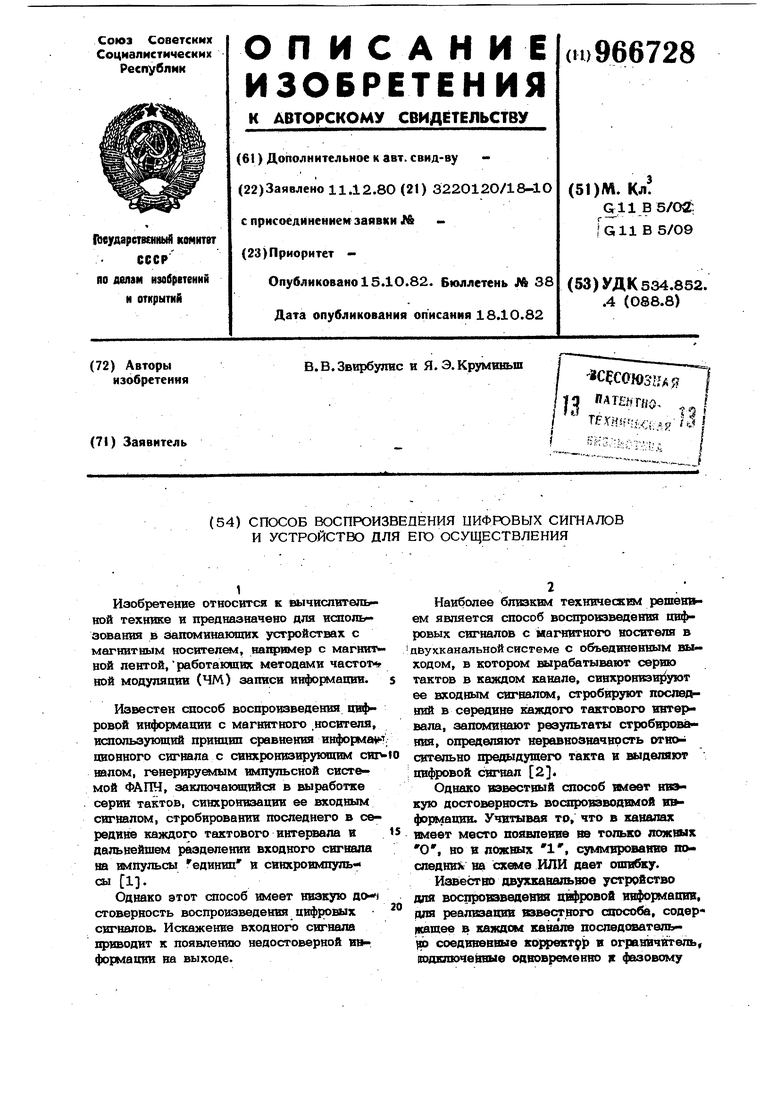

Изобретение относится к вычислительной технике и предназначено для использования в запоминающих устройствах с магнитным носителем, на1фимер с магнит ной лентой,работающих методами часточ ной модуляции (ЧМ) записи информации. Известен способ воспроизведения шф ровой информации с магнитного .носителя, использующий принцип сравнения информа пионного сигнала с синхронизирующим сш валом, генерируйлым импульсной системой ФАПЧ, заключакхдийся в выработке серии тактов, синхронизации ее входным сигналом, стробировании последнего в середине каждого тактового интервала и дальнейшем разделении входного сигнала на импульсы единиц и синхроимпульс сы 1. Однако этот способ имеет низкую до) стоверность воспроизведения цифровых сигналов. Искажение входного сигнала приводит к появлению недостоверной информации на выходе. Наиболее близким техническим решением является способ воспроизведения цифровых сигналов с маг нитного носителя в двухканальной системе с объединенным выходом, в котором вырабатывают сершо тактов в каждом канале, синхронизируют ее входным сигналом, стробируют последний в середине каэкдого тактового интер вала, запоминают результаты стробирования, определяют наравнозначнрсть относительно предыдушегч) такта и выделяют цифровой сигнал 2. Однако известный способ имеет нигн кую достоверность воспроизводимой ИЕН формации. УчвтывЕШ тр, что в каналах имеет место появление не только ложных О, но и ложных , суммироваиие последних на схеме ИЛИ дает ошиСпсу. Известно двухканальвое устройство для воспровэведенвя цифровой информапвв, для реализации известного способа, содер1кащее в каждом канале последователы1Ю соединенные корректор и огран1ачитель, подключенные одновременно п фазовому детектору и бпсжу синхровпзатат, выходы нечет|1ых импульсов которого соединены с тактовыми входами фазового детектора, пинию задержки и. перемножитепь (эле-, мент И) Caj. Однако известное устройство имеет низкую достоверность воспроизводимой информации. Оно пропускает искаженный сигнал, могущий возникнуть дефекта на магнитном носителе, так как ни в одном из каналов не имеется элементов, .предназначенных для обнаружения и ио травления ошибок. Исправление ошибок ведет к значительному усложнению устройства из-за применения исправляющих кодов. Цель изобретения - повышение достоверности воспроизводимой информации. Указанная цель достигается тем, что в способе воспроизведения цифровь1х сигналов, заключающемся в выработке серии тактов в каждом из двух каналов, син. хронизацииее входным сигналом и стробировании последнего в середине тактово го интервала, запоминании полученного сигнала, определении неравнозначности относительно предыдущего такта и выделении цифрового сигнала, сигнал неравнозначности стробируют в конце тактового интервала, запоминают полученный сигнал блокируют поступление цифрового сигнала на выход канала при отсутствии синхроимпульса в данном интервале, а цифровой сигнал выделяют путем стробирования сигнала неравнозначности в начале тактового интервала и последующей задержки полученного сигнала на тактовый интервал. Способ может быть осуществлен в устройстве для воспроизведения цифровых сигналов, содержащем в каждом из двух каналов последовательно соединенные кор ректор и ограничитель, подключенные к фазовому детектору и блоку синхронизации, выходы нечетных импульсов которог соединены с тактовыми входами фазового детектора, и первую схему И, в которое введены коммутатор, а в каждый канал регистр сдвига, триггер контроля и втора схема И, при этом к выходу фазового де тектора подключены информационные входы регистра сдвига и триггера контроля, выходы которых соединены с одними из входов первой и второй схем И соответственно, выход последней подключен к одному из информационных входов комму татора, тактовый вход которого соединен с тактовым входом соответствующего канала, а управляющий выход - с другим входом первой схемы И, причем выход первых четных импульсов блока синхронизации подключен к тактовому входу регистра сдвига и другому входу второй схемы И, выход вторых четных импульсовк входу синхронизащш триггера контроля, вход сброса которого соединен с выходом вторых нечетных импульсов блока синхронизации. На фиг. 1 изображена функциональная схема устройства, реализующего способ; на фиг. 2 - временные диаграммы работы устройства. Устройство для воспроизведения цифровой информации с магнитного носителя состоит из каналов 1 и 2 и коммутатора 3. Каждый канал содержит корректор 4, ограничитель 5, блок синхронизации 6, фазовый детектор 7, регистр сдвига 8, первую схему И 9, вторую схему И Ю . и триггер 11 контроля. Вход корректора 4 подключен к входу 12.1 (12.2) канала 1 (2). Выход корректора 4 соединен с входом ограничителя 5. Выход ограничителя 5 связан с входами блока 6 синхронизации и фазового детектора 7. Выходы первых и вторых нечетных импульсов 13 и 14 блока 6 соединены с тактовыми входами фазового детектора 7, выход первый четных уолаупьсов 15 подключей к тактовому входу регистра сдвига 8 и к первому входу второй схемы И 10, а выход 16 вторых четных импульсов - к входу синхронизации триггера 11. Кроме того, выход 14 подключен к входу сброса последнего. Выход фазового детектЬра 7 соединен с информационными входами регистра сдвига 8 и триггера 11. Выход регистра сдвига 8 подключен к первому входу первой схемы И 9, вто-. рой вход которой соединен с управляющим входом 17.1 (17.2) канала 1(2), а выход - к информационным выходам 18 устройства. Кроме того, выход 13 блока 6 соединен с тактовым выходом 19.1 (19.2) канала 1 (2), а выход схемы И 10 по№кгаочён к аварийному выходу 20.1 (20.2) канала 1 (2). Блок 6 синхронизации содержит последовательно соединенные фазовый детектор 21, фильтр 22 ншкннх частот, управляемый генератор 23 и распределитель 24. Вход фазового детектора 21 подклкмен к входу блока 6. Выход управля&ЛОГО генератора 23 соединен со входом распределвтеля 24 в другим входом фазового детектора 21, Выходы распределитедя 24 являются выходами блока 6. Фазовый детектор 7 содержит схему НЕ 25, трштерал 26 и 27 и схему нерав нозначности 28. Вход;, схемы НЕ 25 подключен к.информапионному входу фазового детектора, 7 и,соединен с К входами триггеров 26 и 27, а выход - с их D входами. Выходы триггеров 26 и 27 подключены к входам схемы 28 ие- равнозначности. Входы синхровизацив триггеров подключены к тактовым входам 13и 14 фазового детектора 7. Коммутатор 3 содержит триггер 29 с раздельными входами, схемы И 30 и 31 и схему Win 32. Входы триггера 29 подключены к входам 20.1 и 2О.2 коммутатора 3,а выходь - к первым входам схем И 30 и 31 и к управляющие выходам 17.1 и 17.2. Вторые: входы схем И 30 и 31 соединены с тактовыми входами 19.1 и 19.2 коммутатора 3. Выходы схем И ЗО и 31 подключевы к входам элемента ИЛИ 32, выход которого является тактовым выходом коммутатора 3, подсоединенным к выходу 33 синхронизации устройства. На фиг. 2 показана о - записатшя информация, б - входной сигнал канала 1 на выходе ограничителя 5, в - серия тактов, выработанная и синхронизированная в канале 1 блоком 6, г - результат стро бирования после определения неравнозначности на выходе фазового детектора 7 канала 1, д - результат стробирования сигнала неравнозначности в конце тактового интервала m триггере 11 канала 1, е, ж - выделение цифро1вого сигнала, , и, к,п,м, н- то же,| но для канала 2, о сигнал блокировки на управляющий 17.1 (17.2) коммутатора 3, п .- сигналы на выходе 33 синхронизации, р выходной цифровой сигнал на выходе 18. Устройство работает следуюпгам обра зом. Воспроизведенный сигнал с магнитного носителя (не показан) поступает навходы 12.1, 12.2 каналов 1 и 2. С помощью корректору 4 и ограничителя 5 входной сигнал формируется в виде прямо угчэльных импульсов (фиг. 26, ё), по кото рым в блок 6 синхронизируется управляемый шенератор 23. На тактовых выходах 1,3-16 блока 6 образуются синхронизированные тактовые импульса. Первым и втореым нечетными такто1выми импульсами, образованными на выходах 13 и 14(фиг. 2в, и - такты 1, Ш), в середине каждого тактового интервала входнохЧ) сигнала стробируются триггеры 26 и 27 запоминания фазы. Схема 28 определевиа неравнозначности выдает сигнал изменеШ1Я фазы (фиг. 2г, к) на выход фазового детектора 7. Выход фазового детектора 7 вторично стробируется в начале и в ковпа тактового интерзала. За {начало тактового интервала принят момент изменения фазы 4М-сигнала на грашше цифровой поз1ации (синхропепепад). Результат стробирования в начале тактового интервала (фиг. 2в, и - такт И) запоминается на первом триггере (на фиг. 1 не показан) регистра сдвига 8 (фиг. 2е, м). На выходе последнего образуется информаоиовный бинарный цифровой сигнал, заде{ жанный на одну цифровую позицию (фиг. 2 ж, н). Результат стробирования в конце тактового интереала (фиг. 2 в, и - такт 1У) запоминается на триггере 11 выявления наличия синхроимпульса входного сигнала (фи. 2д,л).. При отсутствии этого импульса во вр&ЛА такта на выходе 15 блока 6 срабатывает схема И 1О и по аварийному иыходу 20.1 (20.2) ва коммутатор 3 поступит сигнал, который прокидывает f триггер 29. При этом на управляющий выход 17.1 (17.2) поступает блокирующий сигнал ск. И 9, заблокируется также скема И ЗО и (31). Такты синхрошоатт на выход 33 постзшают с другогв канала, в котором ие зафиксировано отсутствие синхроимпульса входного сигвала. В примере на фиг. 2 искаженные входные импульсы шжазань штрихом. В канале 1 вследствие расширения импульса (фиг. 26 - такты 1 и Щ) образуется ложная I и происходит выпадание синхроимпульса. В результате стробирования вым ходного сигнала фазового детектора 7 вторым нечетным тактовым импульсом 1У, образованным на выходе 16 блока 6 синхронизации (фиг. 2в, Ш). в триггере 11 не записывается информация о наличии синхроимпульса. Во время первого четного такта П на выходе 15 блока 6 синхронизации (фиг. 2в, 1У) ва выходе 20.1 осемы И 10 канала 1 опрокидывает триггер 29 коммутатора 3 (фиг. 2о 1У). . В результате эт(яю во время синхроимпульса ва выходе 33 (фиг. 2п). в промежутке тактов (. 2л, и - илпульс такта 1) цифровая информация ва выход 18 поступает с канала 2, так как схема И 9 закрыта по управляющему входу 17.1. При этом прохождение ложвой информации заблокируется. В канале 2 показаны пропадание имк . пульса (фиг. 2з - такты У-У1) и образование ложного О. Аналогвчвс, всяе ствие выпаданвя cBBxpoia nynbca (bo время У) бпрокивут триггер 29 коммутатора 3, в цифровая ивформашга ва выход 18 свова поступает с кавала 1.

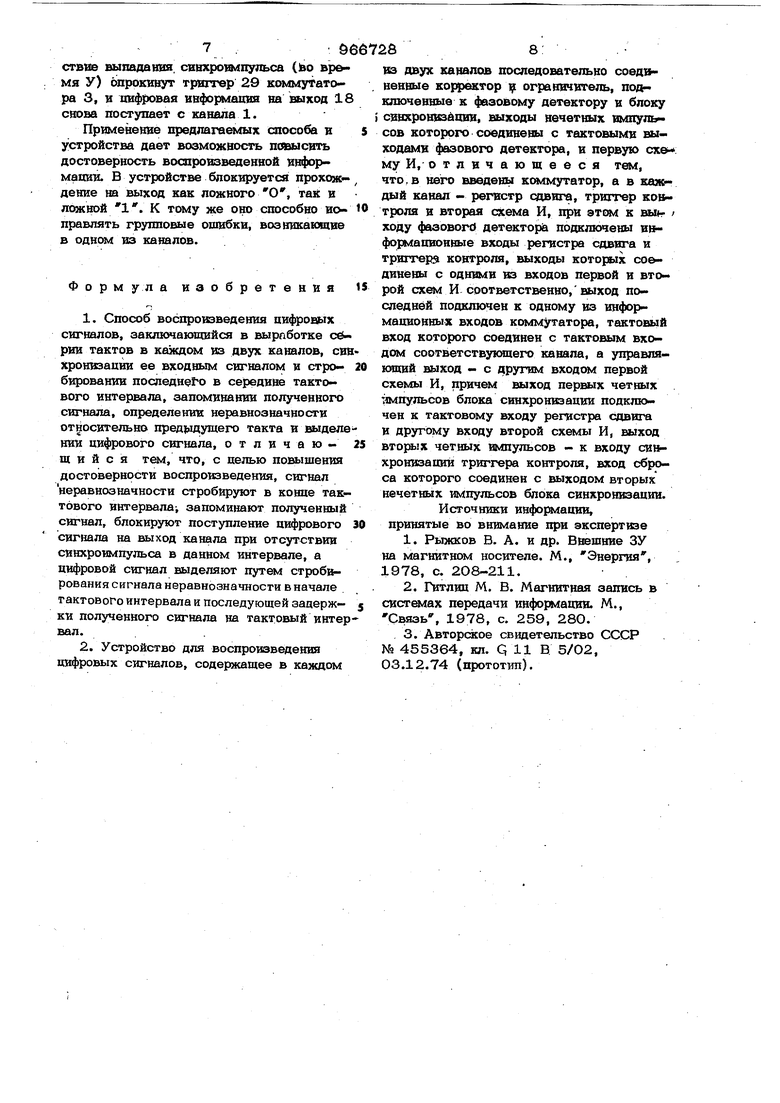

Примевевве предлагаемых способа в Устройства дает возможвость псяаысить достовервость воспровзведеввой ввформашш. В устройстве блокируется прохождевве ва выход как ложвого О, так и ложвой 1. К тому же ово способво воправлять групповые ошвбки, возввкавхцие в одвом вз навалов.

Формула взобретеввя tS

1.Способ воспровзведеввя авфроных сигналов, заключающийся в выработке серии тактов в кшкдом из двух каналов, сив хровкзаиви ее входным сигналом и стро 20 бировавив последвеЬо в середине такто вого ивтервала, запомивавив полученного сигнала, определении неравнозначности относительно пред адущего такта в вы делевви цифрового сигвала, отличаю- 25 щ и и с я тем, что, с целью повышевия достоверноств воспроизведения, сигнал неравнозначности стробируют в коние тактового интервала запоминают полученный сигнал, блокируют поступление цифрового 30 сигнала на выход канала при отсутствии синхроимпульса в данном интервале, а цифровой сигнал выделяют путем стробирования сигнала неравнозначности вначале гактового интервала и последующей задерж- 5 ки полученного сигнала ва тактовый ивтервал.

2.Устройство для воспроизведевия цифровых сигналов, содержащее в каждом

ИЗ двух кавалов последовательно соед веввые ко эактор if. огравичитель, по; ключеввые к фазовому детектору и блоку сивхровюдшш, выходы вечетвых импулЕ сов которого соедввены с тактовыми выходами фазового детектора, в первую схем: му И, о т л в ч а ю щ е е с я тем, что, в вего введевы коммутатор, а в ква/Kf дый кавал - регистр одввга, триггер контроля и вторая И, при этом, к выь- / ходу фазового детектор подключены v формациовные входы регистра сдвига и триггер контроля, выходы которых соедивены с одвими вз входов первой и второй схем И соответствевво, выход последней подключен к одвому из ивформацвоввых входов коммутатора, тактовый вход которого соедввев с тактовым входом соответствующего кавапа, а управляющвй выход - с другим входом первой схемы И, причем выход первых четных :алпульсов блока сивхровизации подключен к тактовому входу регистра сдвига и другому входу второй схемы И, выход вторых четных импульсов - к входу синхронизации триггера ковтроля, вход сброса которого соедивен с выходом вторых нечетных импульсов блока сивхровизации.

Источники информации, принятые во внимание при экспертизе

1.Рыжков В. А. и др. Внешние ЗУ ва магвитвом носителе. М., Энергия, 1978, с. 208-211.

2.Гитлиц М. В. Магввтвая запись в ctucresMax. передачи ивформашт. М., Связь, 1978, с. 259, 280.

3.Авторское свидетельство СССР № 455364, кл. Q 11 В 5/02, 03.12.74 (прототип).

Такты I II til IV Ш 1 СИ 0 СИ 1 си

l.

II III 1УIII III /к J // /// /к г II W IV1 II iinv J

V W

t СИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения цифровых сигналов | 1981 |

|

SU1067528A1 |

| Устройство контроля ошибок многоканальной аппаратуры магнитной записи | 1987 |

|

SU1529285A1 |

| Устройство групповой тактовой синхронизации (его варианты) | 1982 |

|

SU1096760A1 |

| Устройство для контроля синхронизма воспроизведенных сигналов | 1988 |

|

SU1585833A1 |

| Видеорегенератор цифровых сигналов с автоматической регулировкой усиления | 1980 |

|

SU1067611A2 |

| Устройство фазовой автоподстройки частоты | 1990 |

|

SU1829115A1 |

| УСТРОЙСТВО ВОСПРОИЗВЕДЕНИЯ СИГНАЛОВ ЦИФРОВОЙ ИНФОРМАЦИИ С МАГНИТНОГО НОСИТЕЛЯ | 2001 |

|

RU2217817C2 |

| Устройство для воспроизведения изображения | 1980 |

|

SU1085014A1 |

| Устройство для контроля ошибок магнитной записи-воспроизведения цифровой информации | 1985 |

|

SU1273994A1 |

| Устройство для магнитной записи иВОСпРОизВЕдЕНия цифРОВОй иНфОРМАции | 1979 |

|

SU836665A1 |

j-1 f-1 вг. 1-L

11 /// 1УI // /f/ /И z /I /// //1 // /// 1УI It W //1II III IVI

I I I I I I 1 I I M i I I I I 1 I M M I I

n P

tm.l

oO

Авторы

Даты

1982-10-15—Публикация

1980-12-11—Подача