Изобретение относится к радиотехнике и связи и может быть использовано в измерительной технике.

Целью изобретения является повышение точности умножения частоты.

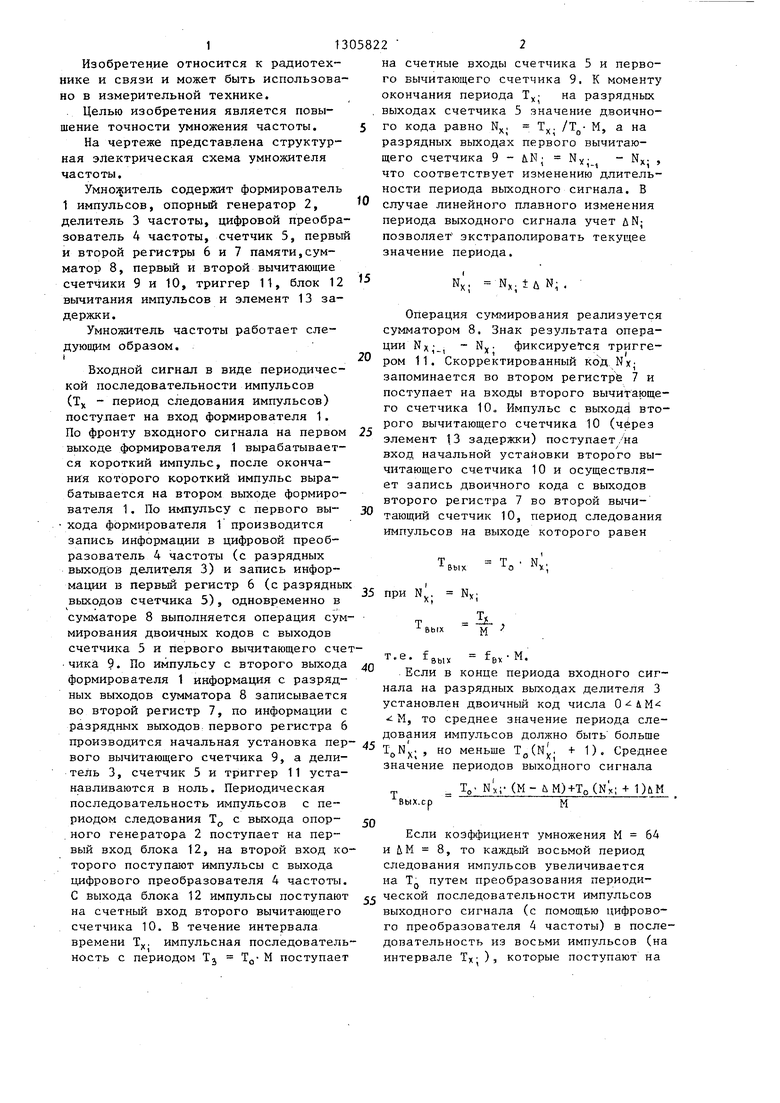

На чертеже представлена структурная электрическая схема умножителя частоты.

Умноз итель содержит формирователь 1 импульсов, опорный генератор 2, делитель 3 частоты, цифровой преобразователь 4 частоты, счетчик 5, первый и второй регистры 6 и 7 памяти,сумматор 8, первый и второй вычитающие счетчики 9 и 10, триггер 11, блок 12 вычитания импульсов и элемент 13 задержки.

Умножитель частоты работает следующим образом.

25

30

Входной сигнал в виде периодической последовательности импульсов (Ту - период следования импульсов) поступает на вход формирователя 1. По фронту входного сигнала на первом выходе формирователя 1 вырабатывается короткий импульс, после окончания которого короткий импульс вырабатывается на втором выходе формирователя 1. По импульсу с первого вы- хода формирователя 1 производится запись информации в цифровой преобразователь 4 частоты (с разрядных выходов делителя 3) и запись информации в первьш регистр 6 (с разрядных выходов счетчика 5), одновременно в сумматоре 8 выполняется операция суммирования двоичных кодов с выходов счетчика 5 и первого вычитающего счет- чика 9. По импульсу с второго выхода 0 формирователя 1 информация с разрядных выходов сумматора 8 записывается во второй регистр 7, по информации с разрядных выходов первого регистра 6

ром 11. Скорректированный код Nx запоминается во втором регистрй 7

и

поступает на входы второго вычитающего счетчика 10.. Импульс с выход4 второго вычитающего счетчика 10 (через элемент 13 задержки) поступает/на вход начальной установки второго вычитающего счетчика 10 и осуществляет запись двоичного кода с выходов второго регистра 7 во второй вычитающий счетчик 10, период следования импульсов на выходе которого равен

вых

т

-L г

N

;;

35 при N. N

i

v;

БЫХ

liМ

т.е. f

вых

f.

М.

Если в конце периода входного сигнала на разрядных выходах делителя 3 установлен двоичный код числа М, то среднее значение периода следования импульсов должно бытьбольше производится начальная установка пер- je „. . „ ,„, ,.

п « T.N... , но меньше T..(N.,, + 1).Среднее

вого вычитающего счетчика 9, а дели- ох. о у. /t- м

теЛь 3, счетчик 5 и триггер 11 устанавливаются в ноль. Периодическая последовательность импульсов с пе л.

значение периодов выходного сигнала

Вых.с

Р

TO- NX;- (М- M)To(N y; + 1)M М

50

риодом следования Т с выхода опорного генератора 2 поступает на первый вход блока 12, на второй вход которого поступают импульсы с выхода цифрового преобразователя 4 частоты.

С выхода блока 12 импульсы поступают ческой последовательности импульсов на счетный вход второго вычитающего счетчика 10. В течение интервала

Если коэффициент умножения М 6 и UM 8, то каждый восьмой период следования импульсов увеличивается на Тд путем преобразования периодивыходного сигнала (с помощью цифров го преобразователя 4 частоты) в посл довательность из восьми импульсов ( интервале )., которые поступают н

времени Т.,. импульсная последовательность с периодом Tj TQ- М поступает

на счетные входы счетчика 5 и первого вычитающего счетчика 9, К моменту окончания периода Т на разрядньк выходах счетчика 5 значение двоичного кода равно N, Т. М, а на разрядных выходах первого вычитающего счетчика 9 - U.N Nv - N. ,

« ,-, А, J

ЧТО соответствует изменению длительности периода вьпсодного сигнала. В случае линейного плавного изменения периода выходного сигнала учет дЫ; позволяет экстраполировать текущее значение периода.

15

N

х;

NX.IU N

Операция суммирования реализуется сумматором 8, Знак результата операции NX,, - N . фиксируемся тригге1 1 Л J j

ром 11. Скорректированный код Nx запоминается во втором регистрй 7

и

поступает на входы второго вычитающего счетчика 10.. Импульс с выход4 второго вычитающего счетчика 10 (через элемент 13 задержки) поступает/на вход начальной установки второго вычитающего счетчика 10 и осуществляет запись двоичного кода с выходов второго регистра 7 во второй вычитающий счетчик 10, период следования импульсов на выходе которого равен

т

-L г

N

;;

0

35 при N. N

i

v;

БЫХ

liМ

т.е. f

вых

f.

М.

Если в конце периода входного сигнала на разрядных выходах делителя 3 установлен двоичный код числа М, то среднее значение периода слеT.N... , но меньше T..(N.,, + 1).Средне

ох. о у. /t- м

л.

значение периодов выходного сигнала

Вых.с

Р

TO- NX;- (М- M)To(N y; + 1)M М

50

ческой последовательности импульсов

Если коэффициент умножения М 64 и UM 8, то каждый восьмой период следования импульсов увеличивается на Тд путем преобразования периодической последовательности импульсов

выходного сигнала (с помощью цифрового преобразователя 4 частоты) в последовательность из восьми импульсов (на интервале )., которые поступают на

второй вход блока 12 и вычитают из периодической последовательности импульсов опорного генератора 2 каждый восьмой импульс. Таким образом осуществляется коррекция статической погрешности.

Формула изобретения

Умножитель частоты, содержащий последовательно соединенные опорный генератор, делитель частоты и цифровой преобразователь частоты, последовательно соединенные счетчик,первый регистр памяти и первый вычитающий счетчик, последовательно соединенные второй регистр памяти и второй вычитающий счетчик, формирователь импульсов, триггер, блок вычитания импульсов и элемент задержки,о т- личающийся тем, что, с ;целью повышения точности умножения частоты, в него введен сумматор,входы первой группы входов которого соединены с соответствующими разрядными выходами счетчика, а входы второй группы входов сумматора соединены с соответствзтощими разрядными выходами первого вычитающего счетчика, выходы сумматора соединены с соответствующими информационными входами второго 30 вычитающего счетчика, выход которого регистра памяти, вход управления сум- является выходом умножителя частоты.

Редактор О. Юрковецкая Заказ 1463/53

Составитель Ю. Максимов

Техред А.Кравчук Корректор А.Зимокосов

Тираж 902Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4

матора, вход управления цифрового преобразователя частоты и вход записи первого регистра памяти объединены и соединены с первым выходом формирователя импульсов, второй выход которого соединен с установочными входами делителя частоты и счетчика, с первым установочным входом триггера, с входом начальной установки первого

(Вычитающего счетчика и с входом записи второго.регистра памяти, знаковый вход сумматора соединен с выходом триггера, второй установочный вход которого соединен с выходом первого вычитающего счетчика, счетный вход которого объединен со счетным входом счетчика и соединен с выходом делителя частоты, счетный вход второго вычитающего счетчика соединен с

выходом блока вычитания импульсов, первый вход которого соединен с выходом опорного генератора, а второй вход блока вычитания импульсов соединен с выходом цифрового преобразователя частоты, счетный вход которого соединен с выходом второго вычитающего счетчика и входом элемента задержки, выход которого соединен с входом начальной установки второго

| название | год | авторы | номер документа |

|---|---|---|---|

| Экстраполирующий умножитель частоты | 1987 |

|

SU1497706A1 |

| Следящий частотомер | 1983 |

|

SU1210104A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1163322A1 |

| Цифровой умножитель частоты | 1985 |

|

SU1314435A1 |

| Преобразователь двоичного кода в код с произвольным весом младшего разряда | 1985 |

|

SU1325708A1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| Цифровой следящий электропривод | 1985 |

|

SU1308982A1 |

| ЦИФРОВОЙ ЧАСТОТОМЕР | 1996 |

|

RU2097774C1 |

| Дискретный умножитель частоты | 1985 |

|

SU1337988A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1992 |

|

RU2042269C1 |

Изобретение относится к радиотехнике. Цель изобретения - повышение точности умножения частоты.Умножитель содержит формирователь 1 импульсов, опорный г-р 2,. делитель 3частоты, цифровой преобразователь 4частоты, счетчик 5, два регистра 6 и 7 памяти, сумматор 8, два вычитающих счетчика 9 и 10, триггер 11,блок вычитания импульсов 12 и эл-т задержки 13. Цель достигается за счет осуществления коррекции статической погрешности путем введения сумматора 8, выполняющего операцию суммирования двоичных кодов с выходов счетчиков 5и 9. 1 ил. i сл 00 сл оо ГС го ,

| Умножитель частоты следования импульсов | 1984 |

|

SU1185561A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU966848A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-04-23—Публикация

1985-04-01—Подача