I

Изобретение относится к автоматике и вычислительной технике, может быть ис- , пользовано дпя воспроизведения значения угла вращения инерционного объекта или для воспроизведения других плавно изме- . НЯЮШИ.ХСЯ процессов, информация о которых передается методом приращений) в системах с цифровой обработкой информа. ции.

Известны интеграторы азимутньк импульсов, содержащие корректор частоты, корректор фазы и реверсивный счетчик, причем корректор частоты выполняет функции следящего умножителя частотьц Информация в виде приращений (азимутных им ,5 пульсов) поступает на вход корректора частоты через неравноотстоящие моменты времени. На выходе корректора частоты скорость изменения инерционного процесса восстанавливается в частотной форме им- м пульсами повыщенной частоты. Процесс ввьпройзводится интегрирующим реверсивный счетчик), двоичный параллельный код которого определяет процесс

во времени. Фазовая коррекция используется для компенсации ошибки, вызванной дискретностью изменения частоты на Bbtходе частотного корректора |1 .

Однако известные ит-еграторы обладают низкой точностью, узким частотным диапазоном, т.е. не позволяют воспроизводить с достаточной точностью процессы, имеющие широкие диапазоны скоростей изменения.

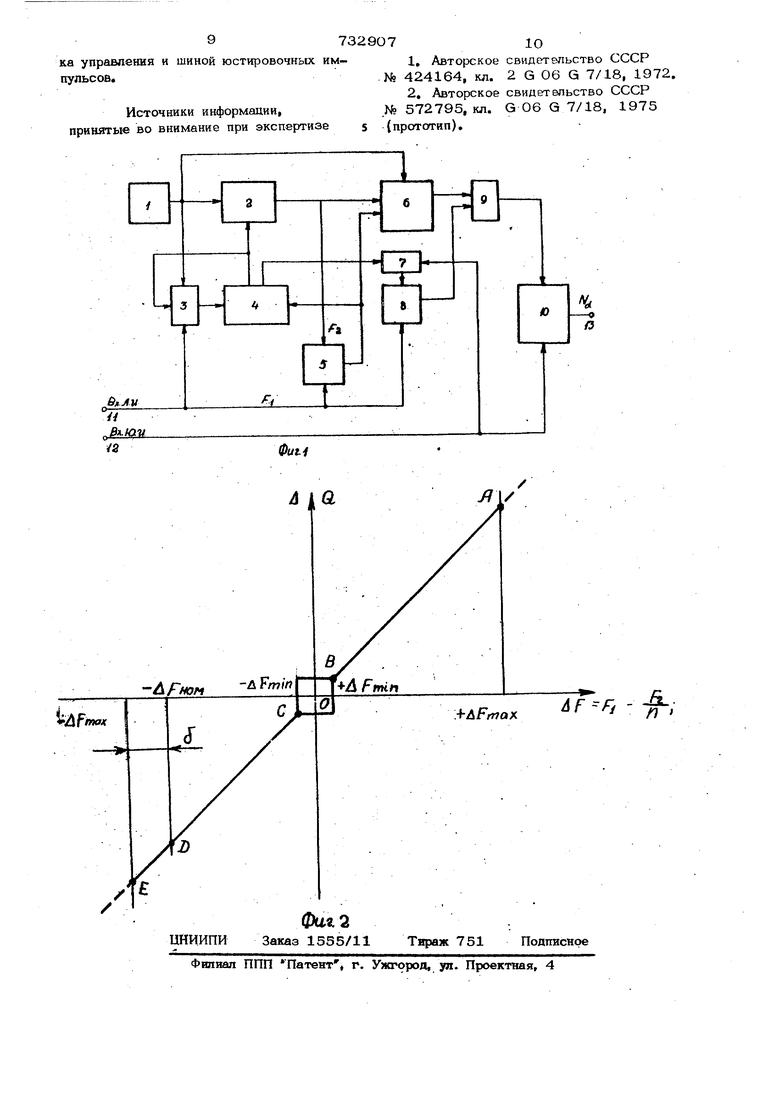

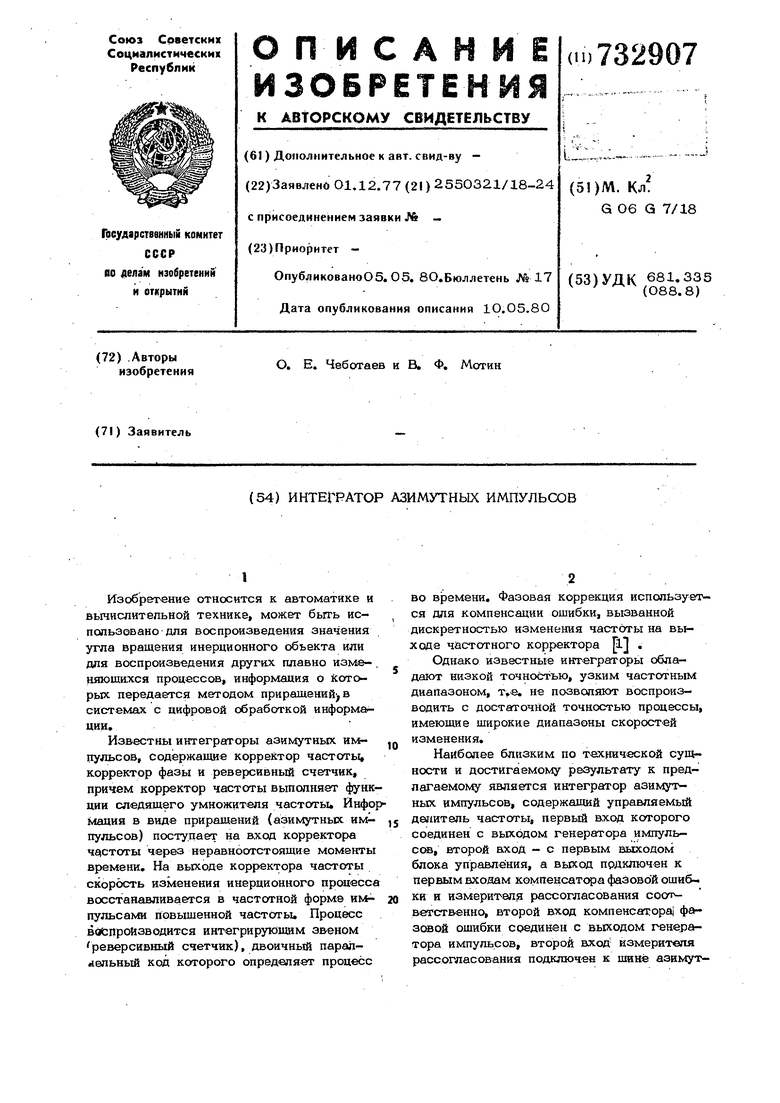

Наиболее близким по технической сущности и достигаемому результату к предлагаемо1уог является интегратор азимутных импульсов, содержащий управляемый делитель частоты, первый вход которого соединен с выходом генератора импульссж, второй вход - с первым выходом блока управления, а выход прдключен к первым входам компенсатора фазовой ошибки и измерителя рассогласования соот ветственно, второй вход компенсатора фазовой ошибки соединен с выходом генератора импульсов, второй вход измерителя рассогласования подключен к щинё азимут37ных импульсов а выход измерителя рассогласования соединен с третьим кходом компенсатора фазовой ошибки и первым входом блока управления, второй аход ко торого соединен с выходом блока коррек ции:,аходы которого подключены к вььходу генератора импульсов и первому выходу блока управления и шине азимуТньгх импульсов, первый аход реверсивног счетчика соединен с выходом компенсатора .фазовой ошибки, а второй вход - с шиной юстировочных импульсов J2 . В интеграторе осуществляется умножение- входных азимутных импульсов на целое, наперед заданное число таким образом, что на выходе управляемого делит ля частоты, формируются импульсы повыше1шой частоты- равномерно расположенные внутри- дискрета входных ажму-г импульсов. Импульсы повышенной частоты подсчитываются счетчиком, выходные разряды которого образуют па ралЛельный двоичный цифровой код При изменении периода азимутных импульсов изменение частоты импульсов повышенной частоты осуществляе- ся изменением коэффициента деления ( ) управляемого делителя частоты через блок управления и блок крррекции по результатам подсчет количества импульсов повышенной частоты за. период между соседними входными азиг тными импульсами в.измерителе рассогласования и с учетом частоты азимутньхх импульсов. Интегратор аз мутньк импульсов с таким управлением хорошо отслеживает изменение частоты азимутньк импульсов в широком диапа- зоне частот с сохранением точности вос произведения угла. Компенсатор фазовой ошибки устраняет ошибку на фазе добавлением или вычитанием из выходной последовательности импульсов повышенной частоты требуемого .количества импульсо Недостаток такого устройства - нали чие ложнь х показаний (двоичный параллельный код угла реверсивного счетчика при остановке врашения. То- есть при остановке Вращения антенны {отсутствие азимутных импульсов в канале связи) с выхода управляемого делителя частоты (корректора частоты) поступают иМпульсы повышенной частоты с частотой частота импульсов повышенной частоты на выходе управляемого- делителя частоты j.y- частота импульсов генератора импульсов, VTl- разрядность управляемого делителя частоты, , - минимально возможное ЧйСЛО на выходе блока управления (в пришдипе N tviivi может . достигать ANy),.|y,0). Следовательно, принципиапьно не может иметь нулевое значение Использование же управляемого делителя частоты с VW- сО нецелесообразно с точки зрения аппаратурной реализации интегратора. Дёль изобретения - повышение точности интегратора за счет исключения лож- ньйс показаний при отсутствии приращений. Поставленная ц-ель достигается тем, что в интегратор азимутных импульсов введены триггер элемент ИЛИ и элемент И, первый аход которого соединен с : выходом компенсатора фазовой (шпбкя, второй - с выходом триггера, а выход с вторым аходом реверсивного счетчика, первый и второй аходы триггера подключены соответственно к шине азимутных импульсов и выходу элемента ИЛИ, пер- вьй и второй аходы которого соединены соответственно со вторым выходом блока управления и шиной юстировочных имПульсов. На фиг. 1 представлена структурная., схема интегратора азимутньгХ импульсов; на фиг, 2 - передаточная характеристика блока управления. Интегратор азимутных импульсов содержит генератор 1 и-мпульсов управляемый делитель 2 частоты, блок 3 Коррек ции, блок 4 управления, измеритель 5 рассогласования, компенсатор 6 фазовой ошибки, элемент ИЛИ 7, триггер 8, элемент И 9, реверсивный счетчик 1О, . шину И азимутных импульсов, шину 12 юстировочных импульсов, выход 13 интегратора. Д0 - изменение двоичного кода М на первом выходе блока 4 управления в зависимости от Д,Р (изменения частоты азимутных импульсой), талгл жах максимально возможйопе изменение часто- Ты азимутных импульсов, на которое реагирует измеритель 5 рассогласования и блок 4 управления, ,,;, - зона нечувствительности (искусственно создаваемая с пелью исключения возможности автоколебаний в системе), г - частота входных азимутных ИМПуЛЕзСОВ, F- - частота импульсов повышенной частоты на выхо де управляемого делител 2 частоты, ft - коэффициент умножения (в установившемся режи ме ). -др - номинальное значение отклонения частоты при котором выдается сигнал со второго выхода блока 4 уп равления (сигнализирующий о прекращении поступления азимутных импульсов на вхо измерителя 5 рассогласован S - ширина зоны реагирования на отклонение частоты бопь ше номинального Ар /АРцо(А Управляемый делитель 2 частоты первым входом соединен с выходом генератора 1 импульсов, вторым - с первым I выходом блока 4 управления, а выходом iподключен к первым нходам компенсатора |6 фазовой ошибки и измерителя 5 рассог ласования соответственно, вторые аходы которых соединены с выходом генератора 1 импульсов, и шиной 11 азимутных импульсов соответственно, третий вход компенсатора 6 фазовой ошибки подклю чен к выходу измерителя 5 рассогласования и первому входу блока 4 управле|ния, второй вход которого соединен с выводом блока 3 коррекции, первый, второй и третий аходы которого подключены к выходу генер гора 1 импульсов, перво му выходу блока 4 управления и шине 11 азимутньгх импульсов соотв«тственно первый аход реверсивного счетчика 1О соединен с шиной 12 юстировочных импульсов, первый аход элемента И 9 соединен с выходом компенсатора 6 фазовой ошибки, второй - с выходом триггера 8, а выход - со вторым входом реверсивного счетчика 10, первый и второй входы Триггера 8 подключены к шине 11 азиму ных импульсов и выходу элемента ИЛИ 7 соответственно, первый и второй аходы которого соединены со вторым выходом блока 4 управления и шиной 12 юстиро-, вочных импульсов соответственно, выход 13 реверсивного счетчика 10 является вькодом устройства. Интегратор азимутньгх импульсов работает следуюш.им образом. При передаче угла враш.ения (инерционного процесса) методом приращений. по каналу связи передается последовательность азимутных импульсов, следующих через равные угловые интервалы, и юстировочный импульс. Интегратор осуществляет экстраполяцию точного углового положения вала на интервале азимутных импульсов, используя инерционные свойства вращающегося объекта. Азимутные импульсы умножаются на целое, наперед заданное число, таким образом, что на выхода управляемого делителя 2 частоты формируются импульсы повышенной частоты, равномерно расположенные внутри дискрета азимутных им1пульсов. Импульсы повышенной частоты через компенсатор 6 фазовой ошибки под- считьшаются реверсивным счетчиком 1О, выходньге разряды которого образуют параллельный двоичный код угла поворота Ьбьекта. При изменении периода азимутйых импульсов изменяется количество импульсов повышенной частоты с выхода управляемого делителя 2 частоты, что приводит к динамической ошибке внутри дискрета входных импульсов. Требуемое в этом случае изменение частоты импульсов повышенной частоты осуществляется изменением коэффициента деления управляемого делителя 2 частоты через блок 4 управления и блок 3 коррекции по результатам не только подсчета количества импульсов повьииенной частоты за период между соседними нходньми азимутными импульсами в измерителе 5 рассогласования, но и с учетом частоты азимутных импульсов. За счет такого управления сохраняется точность воспроизведения угла в широком диапазоне аходных частот азимутйьгх импульсов. Импульсы повышен,ной частоты интегрируются реверсивным счетчиком 1О, запускающим каждым юстировочным импульсом. Инерционные свой) ства вращающегося объекта (изменяющегося процесса) позвол5пот повысить разрешающую способность интегратора путем умножения частоты азимутныхимпульсов. Замкнутый : контур, состояШий из генератора 1 импульс ов управляемого делителя 2частоты, измерителя 5 рассогласования, блока 4 управления и блока 3 коррекции осуществляет слежение за частотой азимутных импульсов и ее кратное ум773ножение. Изменение частоты импульсов повышенной частоты достигается изменением коэффициента депенйя ( С ) управляемого делителя 2 частоты таким образом АН что - -const. Для достижений данной пропорции блок 4 управления и блок 3 коррекции изменяют Д. Ц. пропорцирнально ) поэтому данный замк С (где qнутый контур хорошо отслеживает изменение частоты азимутньк импульсов в широком диапазоне частот с сохранением точ ности воспроизведения угла. При сравнительно низкой частоте азимутных импульсов управляющее воздействие изменяется набольшуювеличину, позволяющую более эффективно компенсировать ошибку по час тоте. При высокой частоте азймутньк импульсов управляющее Воздействие изменяется на меньшую.величину, чем достигается меньшаея динамическая ошибка. Для устранения ошибки по фазе обусловленной дискретностью изменения коэффициента деления { Ц, ), управляемого делителя 2 частоты, в интеграторе применен компен-; сатор 6 фазовой ошибки, осуществляющий сброс ошибки добавлением или вычита- кием из выходной последовательности импульсов повышенной частоты {р2 ) требуе мого количества импульсов. При остановке вращения (отсутствии ,прйращений) ЛР приобретает отрицательный знак.; так как и достигает /avF/ - /uF oivv/i при котором вырабатыгвается со второго выхода блока 4 управления сигнал через элемент ИЛИ 7 на сброс триггера 8, запрещающего через элемент И 9 прохождение импульсов повышенной частоты на счетный в.ход реверсивного счетчика 10, При этом двоич ньй параллельный код угла поворота равен NO(. действит-, NotAeMCTB«Tt-fii.j3a счет инерционности са-г мого интегратора, причемNj.|,( В принципе возможно учесть -JccfN при счн тьшанни действительных показаний реверсивного счетчика 10 Триггер 8 сбрасывается такжб через элемент-ИЛИ 7 каж дым юстировочным импульсом. Триггер 8 в исходное состойние устанавливаетсякакшым азимутным импульсом по вгс.оду IJL. При установке триппера 8 .в единичное состояние на элемент И. 9 поступает разрешающий йотенциал и -импульсы повышенной частоты беспрепятственно прохо дят на счетный вход реверсивного счетчика Ю.. 7 Предложенный интегратор азимутных импульсов выгодно отличается благодаря п овьшденным качеством воспроизведения углового положения (инерционного процесса) вследствие исключения ложньсх показаний, при остановке «зрашения (отсутствии приращений). Искажениеже действительных показаний по отношению к инерционному процессу может быть учтено ((Ун ), так как практически имеет одно и. то же значение. То есть при торможении вращения и остановке вращающегося обьекта представляется возможным вычислить его действительное положение (например антенны), В результате наличия указанньхх достоинств предлагаемого интегратора раст ширяются сфера его испопьзования и функциональные возможности. ормула изобретени Интегратор азимутных импульсов, содержащий управляемый делитель частоты первый вход которого соединен с выходом генератора импульсов, второй вход с первым выходом блока управления, а выход подключен к первым входам компенсатора фазовой ошибки и измерителя рас.согласования соответственно, второй аход. компенсатора фазовой ошибки соединен с выходом генератора импульсов, второй аход измерителя рассогласования подключен к шине азимутных импульсов, а выход измерителя рассогласования соединен с третьим входом компенсатора фа- : зовой ошибки и первым входом блока управленйя, второй аход которого соединен с выходом блока коррекции, входы которого, подключены соответственно к вьрсоду генератора импульсов, первому выходу блока управления и шине азимутных импульсов, первый аход реверсивного счетчика соединен с шиной юстировочных и.мпульсов, отличающийся тем, что, с целью повышения точности интегратора за счет исключения ложных показаний при отсутствии приращений) интегратор содержит триггер, элемент ИЛИ и элемент И, первый вход которого соединен с выходом компенсатора фазовой ошибки второй - с выходом триггера, а выход с BTopijiM входом реверсивного счетчика, первый и второй входы триггера подключены соогветственно к шине азимутвьк импульсов и выходу элемента ИЛИ, первый и второй аходы которого соединены соотв-етственно со вторым выходом бло

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегратор азимутных импульсов | 1977 |

|

SU691877A2 |

| Интегратор азимутных импульсов | 1977 |

|

SU736123A2 |

| Интегратор азимутных импульсов | 1976 |

|

SU646348A2 |

| Интегратор азимутных импульсов | 1975 |

|

SU572795A1 |

| Интегратор импульсов | 1978 |

|

SU750508A1 |

| Устройство для интегрирования частотно-импульсных сигналов | 1984 |

|

SU1160444A1 |

| Преобразователь угла поворота вала в код | 1976 |

|

SU661589A1 |

| ИНТЕГРАТОР АЗИМУТНЫХ И/\\ПУЛЬСОВ | 1972 |

|

SU424164A1 |

| Интегратор импульсов | 1977 |

|

SU714414A1 |

| Следящий умножитель частоты | 1977 |

|

SU732866A1 |

Авторы

Даты

1980-05-05—Публикация

1977-12-01—Подача