которого соединен с первым входом третьего элемента И, с первь№1 входом четвертого элемента И и с третьим выходом распределителя импульсов, четвертый выход которого соединен с первым входом пятого элемента И, вто рой вход которого соединен с вторым входом третьего элемента И, с вторым входом четвертого элемента И и с вторым выходом второго регистра, третий выход которого соединен с третьим входом четвертого элемента И и стретьим входом третьего элемента И, выход которого является первым выходо.м устройства, выход первого элемента И соединен с входом третьего регнстра f выход которого соединен с четвертым входом третьего И и с третьим входом второго элемента И, выход которого соединен с первым входом первого счетчика, выход которого соединен с четвертым входом четвертого элемента И, выход которого является вторым выходом устройства, введены второй счетчик, второй дешифратор, элемент памяти, четвертый регистр, шестой, седьмой, восьмой и девятый элементы И, группа элементов И и элемент ИЛИ, выход которого соединен с вторым входом первого счетчика выход которого соединен с первым входом седьмого элемента И, выход которого-является третьим выходом устройства, третий и четвертый выходы второго регистра соединены с первым и вторым входами шестого элемента И, выход которого соединен с первым входом второго счетчика, выход которого соединен с входом второго дешифратора выходы которого соединены с первыми входами элементов И группы, вторые входы которых соединены с четвертым входом третьего элемента И, третий и четвертый выходы распределителя импульсов соединены соответственно с третьим входом шестого элемента И и с первым входом девятого элемента И, выход которого соединен с вторым входом второго счетчика,.с первым входом восьмого элемента И и с первым входом элемента ИЛИ, второй вход которого соединен с выходом пято,ро элемента И, один из выходов второго дешифратора соединен с вторым входом седьмого элемента .И и с входом элемента памяти, выход которого соединен с вторым входом девятого; Элемента И, выходы элементов И группы соедйнены с входами четвертого регистра, выход которого соединен с вторым входом восьмого элемента-и, выход которого является четвертым выходом устройства.

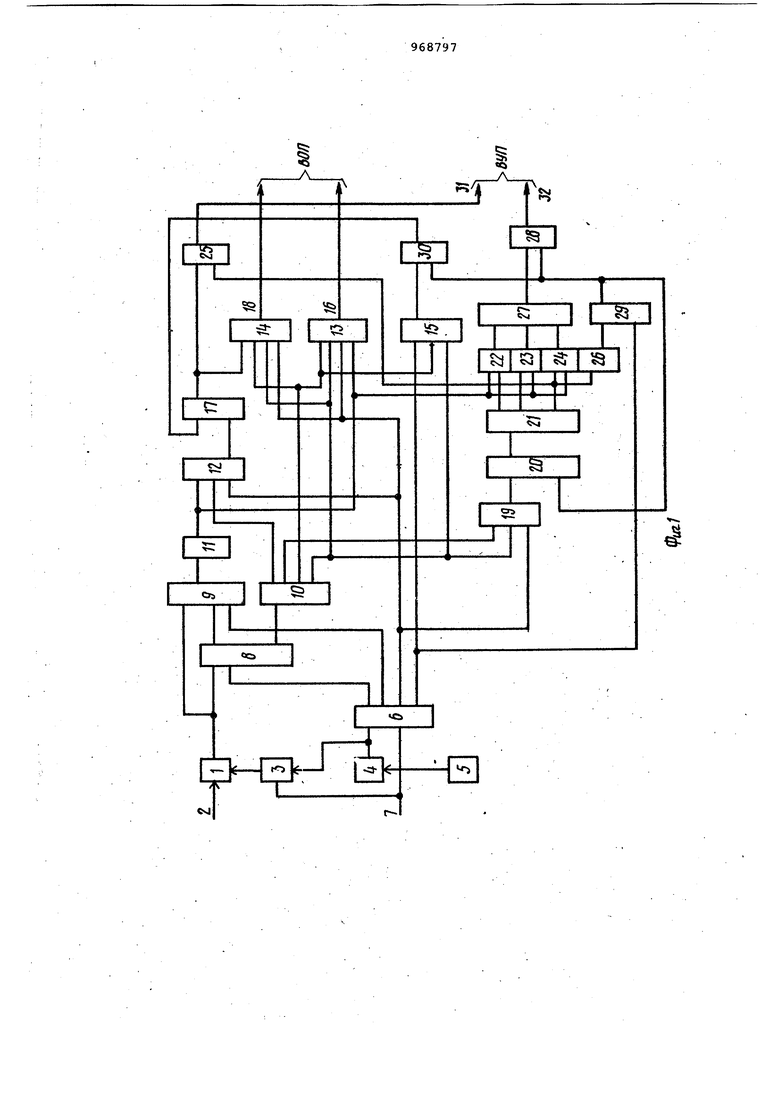

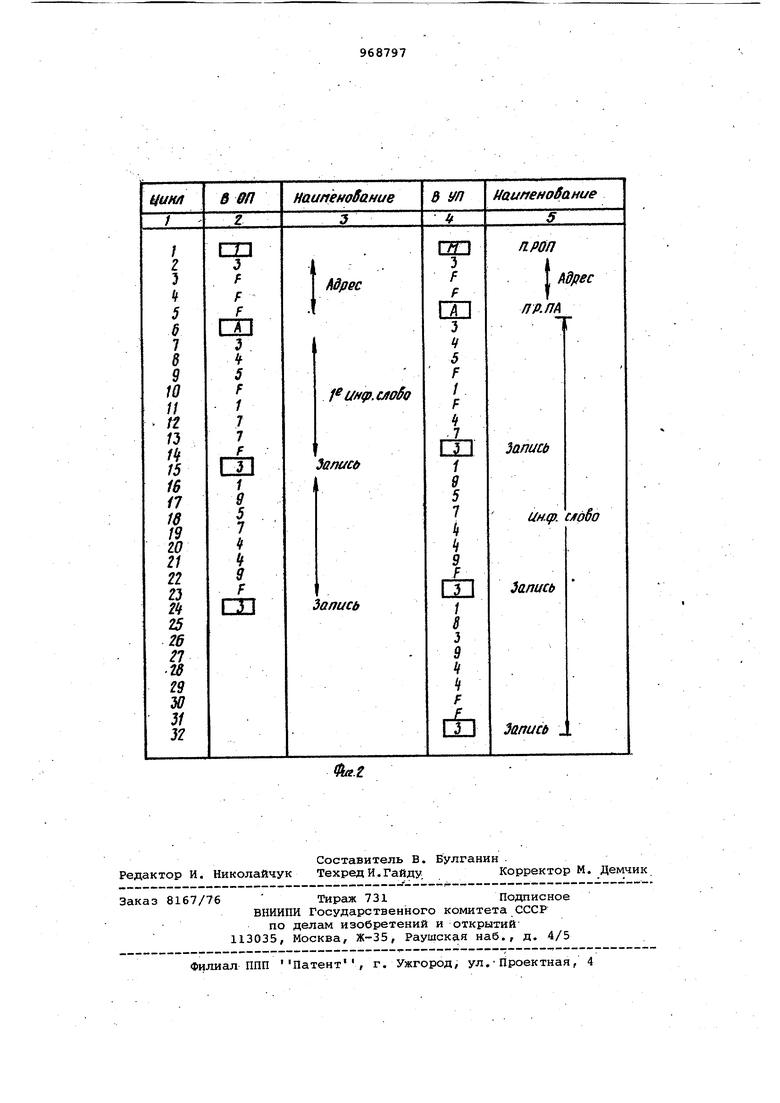

На фиг. 1 представлена структурная схема устройства; на фиг. 2 пример ввода информации.

Устройство содержит первый регистр 1, первый вход 2 устройства, генератор 3 одиночных импульсов делитель 4 Частоты, генератор 5 импульсов, распределитель 6 импульсов, второй вход 7 устройства, первый дешифратор 8, первый элемент И 9, второй 10 и третий 11 регистры, второй 12, третий 13, четвертый 14 и пятый 15 элементы И, первый выход 16 устройства, первый счетчик 17, второй выход 18 устройства, шестой элемент И 19, второй счетчик 20, второй дешифратор 21, группу элементов И 22-24, седьмой элемент И 25, .элемент 26 памяти, четвертый регистр 27, восьмой 28 и девятый 29 элементы И, элемент ИЛИ 30, третий 31 и четвертый 32 выходы устройства.

В таблице на фиг. 2 в графе 1 указывается номер такта, в графе 2 признаки и адрес информации, вводимой в оперативную память, в графе 3 - наименование цикла по первому выходу устройства, в графе 4 - признаки и адрес информации, вводимой в управляющую память, в графе 5 - наименование цикла«по второму выходу устройства.

Устройство работает следующим образом.

Первый такт служит для ввода символа П, являющегося признаком оперативной памяти. Такты с второго по пятый служат для ввода адреса оперативной памяти, в шестом такте вводится признак передачи адреса, обозначенный в графе 2 символом А. В тактах с седьмого по четырнадцатый и с шестнадцатого до двадцать третий вводятся первое и второе информационное слово. В пятнадцатом и двадцать четвертом тактах вводятся признаки записи,, обозначенные в графе 2 символом 3. Информация вводится адресно-групповЕЛм способом, когда перед первым словом информации указывается начальный адрес массива. Адреса последующих вводимых слов определяются модификацией начального йдрёса в первом такте.

В каждом такте символ поступает с первого входа 2 устройства на первый регистр 1.Одновременно по второму входу 7 устройства на генератор 3 одиночных импульсов и распределитель б импульсов поступает синхроимпульс.На вход генератора 3 одиночных импульсов с выхода делителя 4 частоты поступает тактирующая серия импульсов, вырабатываемая генератором 5 импульсов. После записи символа на первый регистр 1 запускается распределитель 6 импульсов(Отрабатывающий пять тактов. По первому такту первый дешифратор 8 анализирует состояние первого регистра 1. Если это состояние соответствует одному из символов служебной информацй г, то соответствующий разряд второго регистра 10 устанавливается в единичное -состояние. Если вводится

символ адресного или числового сло.ва то Четыре младших разряда первого ре гистра 1 по второму такту через первый элемент И 9 поступают на третий регистр 11, который выполнен сдвигающим на четыре позиции в сторону младших разрядов. Второй, третий и. четвертый такты осуществляют ввод адресного слова. При этом первый дешифратор 8 устанавливает признак отсутствия служебной информации. В шестом такте устанавливается, в единичное состояние разряд второго регистра 10. В пятом такте никаких передач не производится. В шестом такте на регистр 1 поступает символ передачи адреса. При этом первый дешифратор 8 анализирует состояние первого регистра 1 и, устанавливает второй разряд второго регистра 10 в единичное состояние. Далее второй элемент И 12 перезаписывает dдресное слово, сформированное в третьем регистре 11 в первый счетчик 17. В последующих восьми тактах производится ввод информационного слова, которое фо15мируется на третьем регистре 11. В пятнадцатом такте вводится признак записи. При этом первый дешифратор 8 производит -анализ содержимого первого регистра 1. Четвертый разряд второго регистра 10 устанавливается в единичное состояние. В этом такте производится также передача адресного и информационного слова в оперативную память через четвертый и третий элементы И 13 и 14, на первый и второй выходы 16 и 18 устрой-, ства. Далее пятый элемент И 15 вырабатывает сигнал модификации адреса, который через элемент ИЛИ 30 посту-пает на второй вход первого счетчика 17.

Рассмотрим ввод информации в управляющую память. На фиг. 2 представлен массив информации, вводимой в управляющую память. Ввиду того, что управляющая память имеет разрядность в три раза большую, чем оперативная память, информационное слово вводится по частям, каждая из которых сопровождается одним и тем же признаком записи; Ввод части осуществляется в той же последовательности, как и при вводе в оперативную память. При этом в первом такте ввода вводится признак .управ ляющей памяти, и первый дешифратор 8 анализирует состояние первого регистра 1 и устанавливает в единичное состояние четвертый разряд второго .регистра 10.В последующих тринадцати тактах вводится адресное слово и первая часть информационного слов а.. Порядок работы в этих циклах такой же,как и при вводе в оперативную память.В четырнадцатом такте вводится признак записи. При этом первый дешифратор 8

анализирует состояние первого регистра 1 и третий разряд второго регистра 10 устанавливается в единичное состояние. Сигнал с выхода шестого элемента И 19 установит в единичное 5 состояние второй счетчик 20. Второй дешифратор 21 анализирует состояние второго счетчика 20 и вырабатывает сигнал, поступающий с первого его выхода на группу элементов И 22, на

0 информационный вход которой поступает содержимое третьего регистра 11 и запоминается на четвертом регистре 27.

В последующих восьми тактах про5 извьдится ввод второй части слова управляющей памяти, которая запоминается на третьем регистре 11. При вводе второго признака запис1г содержимое второго счетчика 20 увеличиQ вается на единицу, при этом сигнал с второго выхода второго дешифратора 21 управляет передачей информации с третьего регистра 11 через группу элементов И 23 на четвертый регистр

с 27. Затем производится ввод третьей части слова управляющей памяти, которая запоминается третьим регистром 11. С вводом третьего признака записи содержимое второго счетчика 20 увеличится еще на единицу, сигнал о третьего

выхода второго дешифратора 21 устанавливает в единичное состояние элемент 26 памяти и управляет передачей содержимого третьего регистра 11 через группу элементов И 24 на четвертый регистр 27, разрядность которого в три раза больше разрядности третьего регистра 11. Девятый элемент И 29 вырабатывает сигнал модификации адреса первого счетчика 17 и производит

0 передачу информационного слова через восьмой элемент И 28 в управляющую память посредством четвертого выхода

32 устройства. На этом ввод одного информационного слова в управляющую

5 память заканчивается

Данное устройство позволяет осуществить ввод информации как в оперативную память, так и в управляющую память, что расширяет функциональные возможности и увеличивает быстродей0

ствие устройства.

Формула изобретения

55

Устройство для ввода информации, содержащее генератор импульсов, выход которого соединен с входом делителя частоты, выход которого соединен с первым входом генератора одиночных

60 импульсов и с первым входом распределителя импульсов, второй вхбд которого является первым входом устройства и соединен с вторым входом генератора одиночных- импульсов, выход

65 которого соединен с первым входом

первого регистра, второй вход которого является вторым входом устройства, выход первого регистра соединен с первым входом первого элемента И и с первым входом первого дешифратора, второй вход которого соединен с первым выходом распределителя импульсов, второй выход которого соединен с вторым входом первого элемента И, третий вход которого соединен с первым выходом первого дешифратора, второй выход которого соединен с входом второго регистра, первый выход которого соединен с первым входом второго элемента И, второй вход которого соединен с первым входом третьего элемента И, с первым входом четвертого элемента И и с третьим выходом распределителя импульсов, четвертый выход которого соединен с первым, входом пятого элемента И, второй вход которого соединен с вторым входом третьего элемента И, с ВТОЕЖ1М входом четвертого элемента И и с вторым выходом второго регистра, третий выход которого соединен с третьим входом четвертого ; элемента И и с третьим входом третьего элемента И, выход которого является первым выходом устройства, выход первого элемента И соединен с входом третьего регистра, выход которого соединен с четвертым входом третьего элемента И и с третьим входом второго элемента И, выход которого соединен с первым.входом первого счетчика, выход которого соединен с четвертым входом четвертого элемента И, выход которого является вторым выходом устройства, отличающеес я тем, что, с целью увеличения быстродействия устройства, в него введены второй счетчик, второй дешифратор, элемент памяти, четвертый регистр, шестой, седьмой, восьмой и девятый элементы И, группа элементов и и элемент ИЛИ, выход которого i соединен с вторым входом первого счетчика, выход которого соединен с первым входом седьмого элемента И, выход которого является третьим выходом устройства, третий и четвертый выходы второго регистра соединены с первым и вторым входами шестого элемента И, выход которого соединен с рервым входом второго счетчика,выход соторого соединен с входом второго децифратора,выходы которого соединены с гервыми входами элементов И группы, вторые входы которых соединены с четвертым входом третьего элемента И, 5 третий и четвертый выходы распределителя импульсов соединены соответственно с третьим входом шестого элемента И и с первым входом девятого элемента И, выход которого соединен с вторым входом второго счетчика, с первым входом восьмого элемента И и с первым входом элемента ИЛИ, второй вход которого соединен с выходом пятого элемента И, один из выходов второго дешифратора соединен с вторым входом седьмого элемента И и с входом элемента памяти, выход которого, соединен с вторым входрм девятого элемента И, выходы элементов И группы соединены с входами четверто.го регистра, выход которого соединен с вторым входом восьмого элемента И, выход которого является четвертым выходом устройства.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 726522, кл. G 06 F 3/02, 1978.

2.Отчет по НИР Таганрогского радиотехнического института;им.. В.Д.Калмыкова Цифровая интегрирующая машина для оценки эффективности радиотехнических систем . Гос. регистрационный № 6991822, г. Таганрог, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для индикации | 1982 |

|

SU1160466A1 |

| Устройство для ввода информации | 1983 |

|

SU1108428A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для вывода информации | 1983 |

|

SU1124278A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1982 |

|

SU1108451A1 |

| Устройство для аппаратурной трансляции | 1984 |

|

SU1164736A1 |

| Устройство для формирования управляющей информации при обработке данных сейсмических колебаний | 1981 |

|

SU1000766A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Селекторный канал | 1974 |

|

SU525081A1 |

| Устройство управления | 1984 |

|

SU1171790A1 |

Авторы

Даты

1982-10-23—Публикация

1981-05-08—Подача