вый и второй выходы которого соеди}-1ены с вгоры - входами элементов И четвертой и пятой групп, третий второго делтфратора соединен с первь21и входами элементов И шестой н восьмой групп и входом элемента памяти, выход которого соединен с вторьм входом третьего элемента И, вход сброса первого счетчик 1, первые входы элементов И девятой группы и первый вход первого элемента ИЛИ соединены с выходом третьего элемента И, второй вход первого элемента соедииеп с выходом второго элемента И, счетный вход второго счетчика соединен с выходами элементов И второй группы, а вход сброса соединен с выходом первого элемента ИЛИ, второго счетчика соединен с четвертыми входами элементов И седьмой группы и вторыми входами элементов И восьмой группы, выходы элементов И седьмой группы являются выходами второй группы устройства, выходы элементов И восьмой 1руппы являются выхсдами третьей группы устройства, выходы элс;ментов И четвертой, пятой и шестой групп соединены с входами четверioio pen-tCTpa, выход которого соединен с вторыьш входами элементов И де зятой группы, выходы которой являются выходами четве 1той группы устройства, о т л и ч а ю щ е е с я тем, что с цел}з1о увеличения быстродействия, устройство содержит второй и третий элеме1 Т1)1 ИЛИ, четвертый и пятый элементы И, первый второй и третий выходы второго дешифратора соединены с ne 3BbiM, BTopiHM и третьим входами второго элемента ИЛИ, ыход которого соединен с первым входом четвертого элемента И, вторые вхад1 1 четвертого и питого элементов И соединены с пят)1м выходом распределителя импульсо;., первый вход пятого элемента И сс.единен с первым выходом второго регистра, четвертого и пятого э,;и;менгов И соединены с входами третьего э.пеметгга ИЛИ, выход которого соедине с входом сброса трс/гьего регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1981 |

|

SU968797A1 |

| Устройство для индикации | 1982 |

|

SU1160466A1 |

| Устройство для ввода информации | 1983 |

|

SU1109727A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для планирования радиолиний спутниковой связи | 1990 |

|

SU1691851A1 |

| Устройство для вывода информации | 1983 |

|

SU1124278A1 |

| Устройство для диагностики каналов ввода-вывода | 1977 |

|

SU669921A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1982 |

|

SU1108451A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ, содержащее генератор импульсов, первый, второй, третий и четвертый регистры, генератор одиночных импульсов, распределитель импульсов, первый и второй дешифраторы, с первой по девятую группы элементов И, первый, второй и третий элементы И, первый и второй счетчик, элемент памяти и первый элемент ИЛИ, информационные входы первого регистра являются входами группы устройства, управляющий вход первого регистра соединен с выходом генератора одиночных импульсов, первый вход которого и первый вход распределителя импульсов являются входом устройства, второй вход генератора одиночных импульсов и второй вход р;спределите.т1Я импульсов соединены с выходом делителя частоты, вход делителя частоты соединен с выходом генератора импульсов, выходы первого регис-.тра соединены с входами первого дсмлифратора, первы и второй выходы которого соединены с первыми и нторыми рходами )лемснтов И nepFJOi групп,1, а третий выход соединен : ш-риым ))хо;г,()м иторо го регистра, второй вход которого соединен с первым выходом распределителя импульсов, второй вьосод которого соединен с третьими входами элементов И первой группы, выходы элементов И первой группы соединены с входами группы третьего регистра, выход которого соединен с первыми входами элементов И второй, третий, четвертой, пятой и шестой групп, третий выход распределителя импульсов соединен с первым входом первого элемента И, вторыми входами элементов И третьей группы, первыми входами элементов И седьмой группы и вторыми входами элементов И второй группы, третьи входы элементов И второй группы соединены с пер(Л вым выходом второго регистра, втоС рой выход второго регистра соединен с третьими входами элементов И третьей группы, вторыми входами элементов И седьмой группы, вторым входом первого элемента И и первым входом второго элемента И, третий выход второго регистра соединен с вторым входом второго элемента И, четвертыми входами элементов И третьей группьЕ и третьими входами элементов И седьмой группы, четвертый выход распределителя импульсов соедин

Изобретение относится к области автоматики и вычислительной техники и может бычь использовано в сиедиализирован 1ьгх дифровых машинах.

Известно устройство для ввода iniформадии, содержащее первый регистр, генератор одиночных импульсов, делитель частоты, дешифратор, первую четвертую группы элементов И, второй и третий регистр, счетчик, элемент И Устройство обеспечивает как 5учной, так и автоматический ввод, 1-1нформации 111.

Однако устройство позволяет загружать только оперативную память и не может произвести загрузку управляющв памяти.

Наиболее близким к данному является устройство для ввода информации, содержащее генератор импульсов, первый - четвертый регистры, генератор одиночных импульсов, распределитель импульсов, первый и второй дешифраторы, с первой по девятую группы элементов И, перв,1Й - третий элемен И, первый и второй счетчик, эл(г-:е1гг памяти и первый элемент ИЛИ, И1и|л)рмадион1-1ые вхо,аы первого регистра являются }1ходами группы устройства, упраБля1С1 л;ий вход первого регистра соединен с выходом гене ратора о,:1иночиых импупьсов, первый вход кото1)ого и первый вход распределителя импульсов являются входом устро1Чства,

в,горой вход генератора одиночных импульсов и второй вход распределите.;;я импульсов соединены с выходом лелите.ия частоты, )зход до.пителя часточы соединен с выходом генератора

импульсов, выходы первого регистра соединены с входами первого дешифрато)5а, первый и второй выход ; которого соединены с первыми и вторыми вход,ама элементов 11 первой rjiynnbi, а

третий выход - с первым входом второго регистра, второй вход которого соединен с всрвым выходом распредеоп теля И1 пульсов, BTOpoil выход которого соединен с третьими входами элеменТО , И первой Группы, яыход.| э:ементов И первой группы (-(лпноны с входами группы третьего регистра, выход которого соединен с первыми входами элементов И второй - шестой групп, третий выход распределителя импульсов соединен с первым входом первого элемента И, вторыми входами элементов И третьей группы, первыми входами элементов И седьмой группы и вторыми входами элементов И второй группы, третьи входы элементов И второй группы соединены с первым входом второго регистра, второй выход второго регистра соединен с третьими входами элементов И третьей группы, вторыми входами элементов И седьмой группы, вторым входом первого элемента И и первым входом второго элемента И, третий выход второго регистра соединен с вторым входом второго элемента И, четвертыми входами элементов И третьей группы и третьими входами элементов И седьмой группы, четвертый выход распределителя импульсов соединен с третьим входом второго элемента И, четвертый выход второго регистра соединен с третьим входом первого элемента И, выходы элементов И третьей группы являются выходами первой группы устройства, выход первого элемента И соединен со счетным входом первого счетчика, выходы которого соединены с входами второго дешифратора, первый и второй выход которого соединены с вторыми входами элементов И четвертой и пятой групп, третий выход второго дешифратора соединен с первыми входами элементов И шестой и восьмой групп и входами элемента памяти, выход которого соединен с вторым входом третьего элемента И, вход сброса первого счетчика, первые входы элементов И девятой группы и первый вход первого элемента ИЛИ соединены с выходом третьего элемента И, второй вход первого элемента ИЛИ соединен с выходом второго элемента И, счетньй вход второго счетчика соединен с выходами элеме1гтов И второй группы, а вход сброса - с выходом первого элемет)та ЯЛИ, выход второго счетчика соединен с четвертьми входами элементов И седьмой группы и вторыми входами элементов И восьмой группы, выходы элементов И седьмой группы Иявляются выходами второй группы устройства, выходы элементов И восьмой группы - выходами третьей группы устройства, пыход1 1 элементов

И четвертой - шестой групп соединены с входами четвертого регистра, выход которого соединен с вторыми входами элементов И девятой группы, выходы которой являются выходами четвертой группы устройства С 21.

Недостатком ивестного устройства является невысокое быстродействие при загрузке управляющей памяти.

Цель изобретения - повышение быстродействия при загрузке управляющей памяти, осуществляемой по частям, если эти части содержат нулевую информа1ц-1ю.

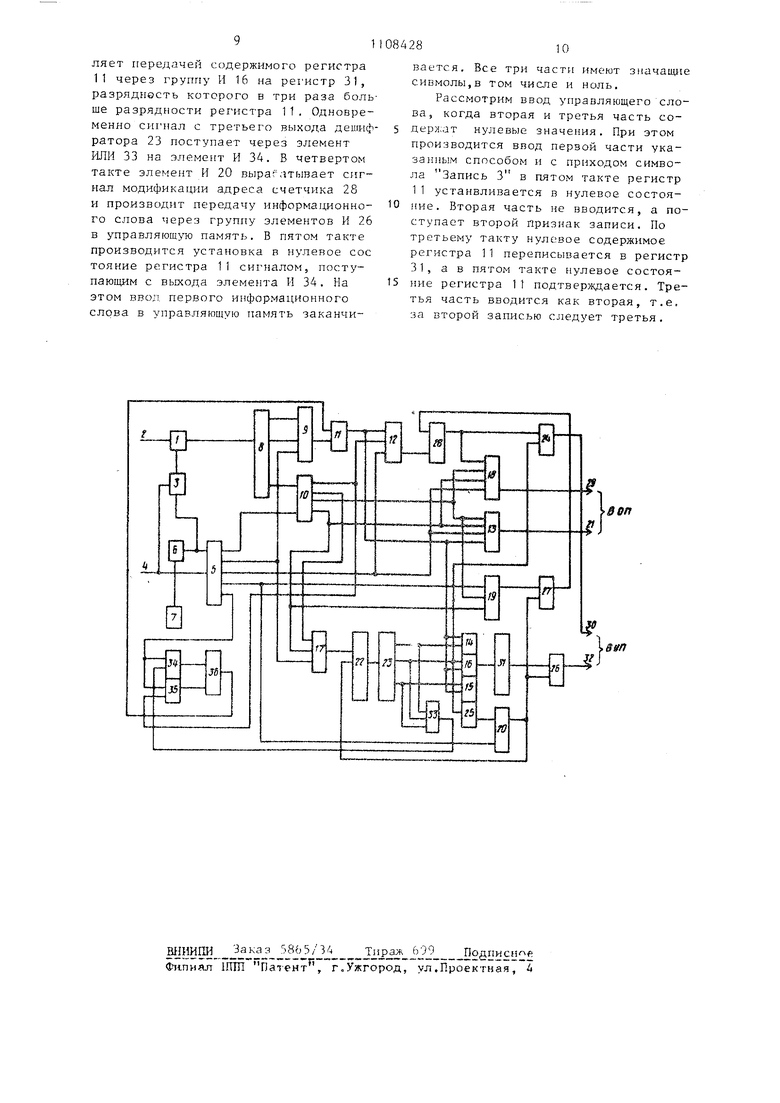

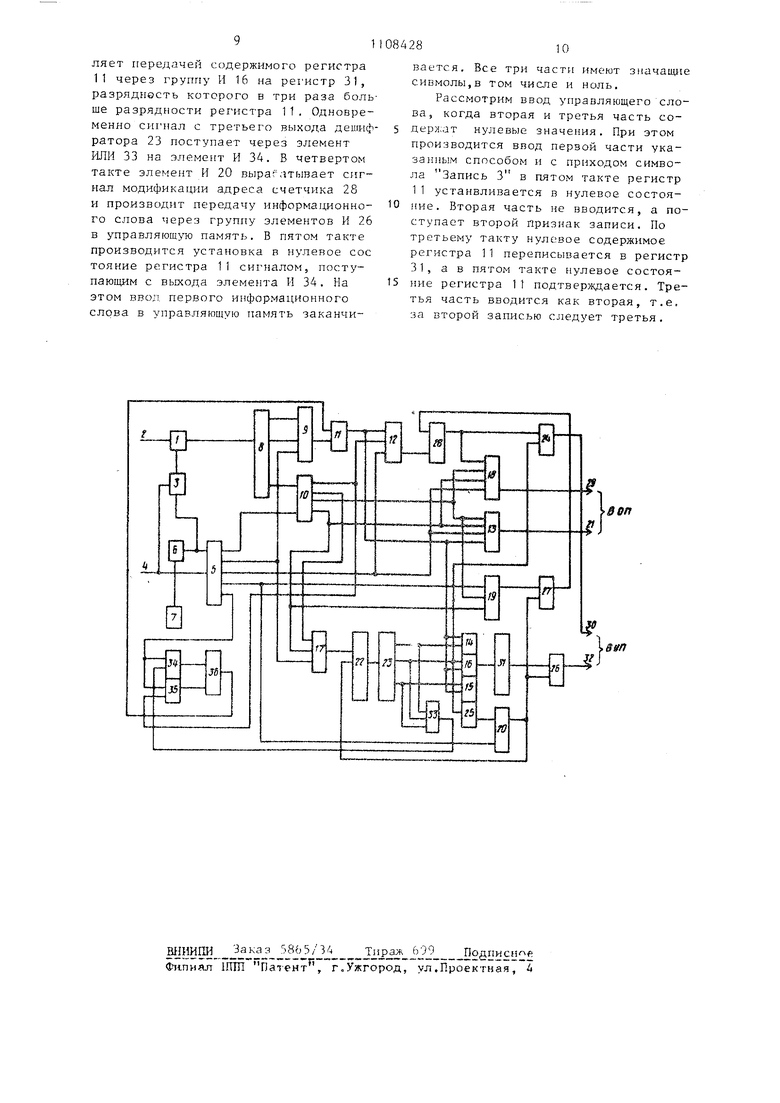

Поставленная цель достигается тем, что в устройство для ввода информации, содержащее генератор импульсов, первый, второй, третий и четвертый регистры, генератор одиночных импульсов, распределитель импульсов, первый и второй дешифраторы, с первой по девятую группы элементов И, первый, второй и третий элементы И, первый и второй счетчик, элемент памяти и первый элемент ИЛИ, информационные входы первого регистра являются входами группы устройства, управляющий вход первого регистра соединен с выходом генератора одиночных импульсов, первый вход которого и первый вход распределителя импульсов являются входом устройства, второй вход генератора одиночных импульсов и второй вход распределителя импульсов соединены с выходом делителя частоты, вход делителя частоты соединен с выходом генератора импульсов, выходы первого регистра соединены с входами первого дешифратора, первый и второй выходы которого соединены с первыми и вторыми входами элементов И первой группы, а третий выход соединен с первым входом второго регистра, второй вход которого соединен с первым выходом распределителя импульсов, второй выход которого соединен с третьими входами элементов И первой группы, выходы элементов И первой группы соединены с входами группы третьего регистра, выход которого соединен с первыми входами элементов И второй, третьей, четвертой, пятой и шестой групп, третий выход распределителя импульсов соединен с первым входом первого элемента И, вторыми входами элементов И третьей группы, первыми входами элементов И седьмой группы и вторыми входами элементов И второй группы, третьи входы элементов И вто рой группы соединены с первым выходом второго регистра, второй выход второго регистра соединен с третьими входами элементов И третьей группы, вторыми входами элементов И седьмой группы, вторым входом первого элемента И и первым входом второго элемента И, третий выход второго регист ра соединен с вторым входом второго элемента И, четвертыми входами элементов И третьей группы, и третьими входами элементов И седьмой группы, четвертый выход распределителя импул сов соединен с третьим входом второго элемента И и первым входом третье го элемента И, четвертый выход второ го регистра соединен с третьим входом первого элемента -И, выходы элементов И третьей группы являются выходами первой группы устройства, выход первого элемента И соединен со счетным входом первого счетчика, выходы которого соединены с входами второго дешифратора, первый и второй выходы которого соединены с вторыми входами элементов И четвертой и пятой групп, третий выход второго дешифратора соединен с первыми входами элементов И шестой и восьмой групп и входом элемента памяти, выход кото рого соединен с вторым входом третье го элемента И, вход сброса первого .счетчика, первые входы элементов И девятой группы и первый вход первого элемента ИЛИ соединены с выходом третьего элемента И, второй вход пер вого элемента ИЛИ соединен с выходом второго элемента И, счетный вход вто рого счетчика соединен с выходами элементов И второй группы, а вход сброса соединен с выходом первого элемента ИЛИ, выход второго счетчика соединен с четвертыми входами эле ментов И седьмой группы, вторыми вхо дами элементов И восьмой группы, выходы элементов И седьмой группы явля ются выходами второй группы устройст ва, выходы элементов И восьмой группы являются выходами третьей группы устройства, элементов И четвертой, пятой и шестой групп соедине ны с входами четвертого регистра, выход которого соединен с вторыми входами элементов И девятой группы, выходь которой являются выходами чет вертой группы устройства, дополнительно введены нторой и третий элементы ИЛИ, четвертый н пятый элементы И, первый, второй и тр(тий выходы второго дешифратора соединены с первым, вторым и третьим входами второго элемента ИЛИ, выход которого соединен с первым входом четвертого элемента И, вторые входы четвертого и пятого элементов И соединены с пятым выходом распределителя импульсов, первый вход пятого элемента И соединен с первым выходом второго регистра, выходы четвертого и пятого элементов И соединены с входами третьего элемента ИЛИ,вь1ход которого соединен с входом сброса третьего регистра. На чертеже представлена структурная схема устройства. Устройство содержит первый регистр 1, шину данных устройства 2, генератор одиночных импульсов 3, синхровход устройства 4, распределитель импульсов 5, делитель частоты 6, генератор импульсов 7, первый деишфраT(jp 8, первую группу элементов И 9, второй 10 и третий 11 регистры, вторую 12, третью 13, четвертую 14, пятую 15 и шестую 16 группу элементов И, первый элемент И 17, седьмую группу эл ементов И 18, второй 19 и третий 20 элементы И, выходные шины 21 в оперативную память, первый счетчик 22, второй дешифратор 23, восьмую группу элементов И 24, элемент памяти 25, девятую группу элементов И 26, первый элемент ИЛИ 27, второй счетчик 28, выходные шины 29 в оперативную память, выходные шины 30 в управляюшую память, четвертый регистр 31, выходные шины 32 в управляющую память, второй элемент ИЛИ 33, четвертый 34 и пятый 35 элементы И, третий элемент ИЛИ 36. Устройство работает следующем образом. Ввод информации производится с клавиатуры либо автоматически посимвольно . Ввод в оперативную память. В первом Цикле с первой группы входов 2 на регистр 1 поступает признак оперативной памяти. Одновременно на генератор 3 и распределитель импульсов 5 с первого входа устройства 4 поступает синхроимпульс. Импульс с выхода генератора 3 разрешает запись в регистр 1. По первому такту распределителя импульсов 5 дешифратор 8 анализирует состояние ретистра 1 и устамавлирает первый разряд регистра К)

в единичное состояние. В остальных тактах перного дакла ничего не происходит. Во итором - пятом циклах осуществляется ввод адресного слова. В каждом цикле цо первому такту дешифратор 8 вырабатывает сигнал отсутствия информации, разрешающий перезапись четырех младших разрядов из регистра 1 в регистр 11 по второму такту. В шестом цикле на регистр 1 поступает признак передачи адреса. Б первом такте второй разряд регистра 10 устанавливается в единичное состояние. Передача четырех младших разрядов регистра 1 через группу элементов И 9 в младшие разряды регистра 11 производится во втором такте каждого цикла, ввода адресного или информационного слова при наличии сигнала отсутствия служебной информац11и, поступающего с выхода дешифратора 8 на второй вход группы элементов И 9. Регистр 11 выполнен сдвигаюш 1м в сторону старших разрядов на четыре позиции. В третьем такте шестого цикла группа элементов И 12 переписывает сформированное в предыдущих циклах адресное слово из регистра 11 в счетчик 28. В четвертом такте шестого цикла второй разряд регистра 10 устанавливается в нулевое состояние. В поаггедуюи1их восьми циклах производится ввод информационного слова. В пятнаццлтом цикле вводится признак записи. В первом такте пятнадцатого цикла депшфратор 8 производит анализ содерж1 мого регистра 11 и т;н;тий разряд регистра 10 устанавливается в единичное состояние. В третьем такте производится передача адресного и информационного слова через группу элементов И 18,13 через выходные шины устройства в оперативную память. В четвертом такте элемент И 19 формирует сигнал модифика ;пи адреса, который через элемент И 26 поступает на второй вх(.;д счетчика 28. После этого третий разряд регистра 10 устанавливается в нулевое состояние. Ввод адресного и первого информационного слова заKOHUMi. В нсплецуюших Д(;вяти циклах вводится иторос информационное слово и т .,ч..

Ввод в упра яллк1|цую память. Управляющая ггамят). имсгт разрядность в тр раза бо;1Ь 1)ун )агинной, П( упр.шляюииб i..iioHv гиодится и

каждая из которых сопровождается при наком записи, В первом слове все три части полноразрядные, во втором слове полноразрядная только первая, часть, вторая и третья нулевые. Ввод каждой части первого слова осуществляется в той же последоБательности, что и при вводе в оперативную память В первом цикле вводится признак управляющей памяти, в первом такте дешифратор 8 анализирует состояние регистра 1 и устанавливает в единичное состояние четвертый разряд регистра 10. В последующих двенадцати циклах вводится адресное слово и первая часть информационного слова. Порядок работы в этих циклах такой же, как и при вводе в оперативную память. В четырнадцатом цикле вводится признак записи. В первом также дешифратор 8 анализирует состояние регистра 1 и устанавливает в единичное состояние третий разряд регистра 10. В третьем такте сигнал с выхода элемента И 1 7 устанавливает в единичное, состояние счетчик 22. Дешифратор 23 анализирует состояние счетчика 22 и вырабатывает сигнал, поступающий с его первого выхода на группу элементов И 14, на информационный вход которой поступает со;.1,ержимое регистра 11 и запоминается регистром 31. В пятом такте элемент И 34 вырабатывает сигнал, который поступает через элемент ИЛИ 36 на вход сброса регистра 1 1 и устанавливает его в нулевое состояние.

В последующих восьми циклах производится ввод второй части слова управляющей памяти. При вводе второго признака записи состояние счетчика 22 увеличивается на единицу. При этом сигнал с второго выхода дешифратора 23 управляет передачей информации с регистра 11 через группу элементов И 15 на регистр 31 . Сигнал с выхода дешифратора 23 через элемент ИЛИ 33 поступает на элемент И 34, который по пятому такту устанавливает в нулевое состояние регистр 11. С двадцать четвертого по тридцать первый цикл производится ввод третьей части, которая запоминается регистром 11. С приходом третьего признака записи содержимое счетчика 22 увеличивается на единицу. Сигнал с третьего выходы дешифратора 23 устанавливает в единичное состояние элемент памяти 25 и упрлвляет передачей содержимого регистра 11 через группу И 16 на регистр 31, разрядность которого в три раза больше разрядности регистра 11. Одновременно с третьего выхода дешифратора 23 поступает через элемент ИЛИ 33 на элемент И 34. В четвертом такте элемент И 20 выраг лт(згаает сигнал модификации адреса счетчика 28 и производит передачу информационного слова через группу элементов И 26 в управляющую память. В пятом такте производится установка в нулевое сое тояние регистра 11 сигналом, поступающим с выхода элемента И 34. На этом ввол первого информационного слова в управляющую память заканчивается. Все три части имеют значащие сивмолы,в том числе и ноль.

Рассмотрим ввод управляющего слова , когда вторая и третья часть содерл,ат нулевые значения. При этом производится ввод первой части указа способом и с приходом символа Запись 3 Б пятом такте регистр 11 устанвливается в нулевое состояние. Вторая часть не вводится, а поступает второй признак записи. По третьему такту нулевое содержимое регистра 11 переписывается в регистр 31, а в пятом такте нулевое состояние регистра 11 подтверждается. Третья часть вводится как вторая, т.е. за второй записью следует третья.

@еп

ввп

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для ввода информации | 1981 |

|

SU968797A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-15—Публикация

1983-04-07—Подача