(54) УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В КВАДРАТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения в степень | 1976 |

|

SU656056A1 |

| Квадратор | 1986 |

|

SU1322273A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1003078A1 |

| Устройство для возведения в квадрат импульсных сигналов | 1981 |

|

SU1057943A1 |

| Устройство для возведения в квадрат комплексных чисел | 1980 |

|

SU879584A1 |

| Устройство для возведения в квадрат | 1975 |

|

SU606156A1 |

| Вычислительное устройство | 1983 |

|

SU1130862A1 |

| Устройство для возведения в квадрат и извлечения квадратного корня | 1982 |

|

SU1141406A1 |

| Устройство для возведения в степень | 1976 |

|

SU888106A1 |

| Устройство для вычисления квадрата числа | 1983 |

|

SU1115051A1 |

1

Устройство относится к автоматике и вычислительной технике и может быть использовано при реализации технических средств дискретной автоматики, а также в цифровых вычислительных машинах, арифметических устройствах блочного типа и специализированных вычислителях, построенных на интегральных микросхемах.

Известно устройство для возведения в квадрат, содержащее группу элементов И, п-разрядный входной регистр, разрядными входами соединенный с шинами входного кода 1 .

Недостатком устройства является его сложность.

Наиболее близким техническим решением к предлагаемому является устройство, содержащее группу элементов И, сумматор, элемент НЕ, регистр результата, регистр основания и вспомогательный регистр, разрядными входами подключенный к регистру основания 2.

Недостатки устройства заключаются в малом быстродействии при выполнении операции возведения в квадрат и невозможности возведения в квадрат чисел, представленных параллельным кодом.

Цель изобретения - повыщение быстродействия.

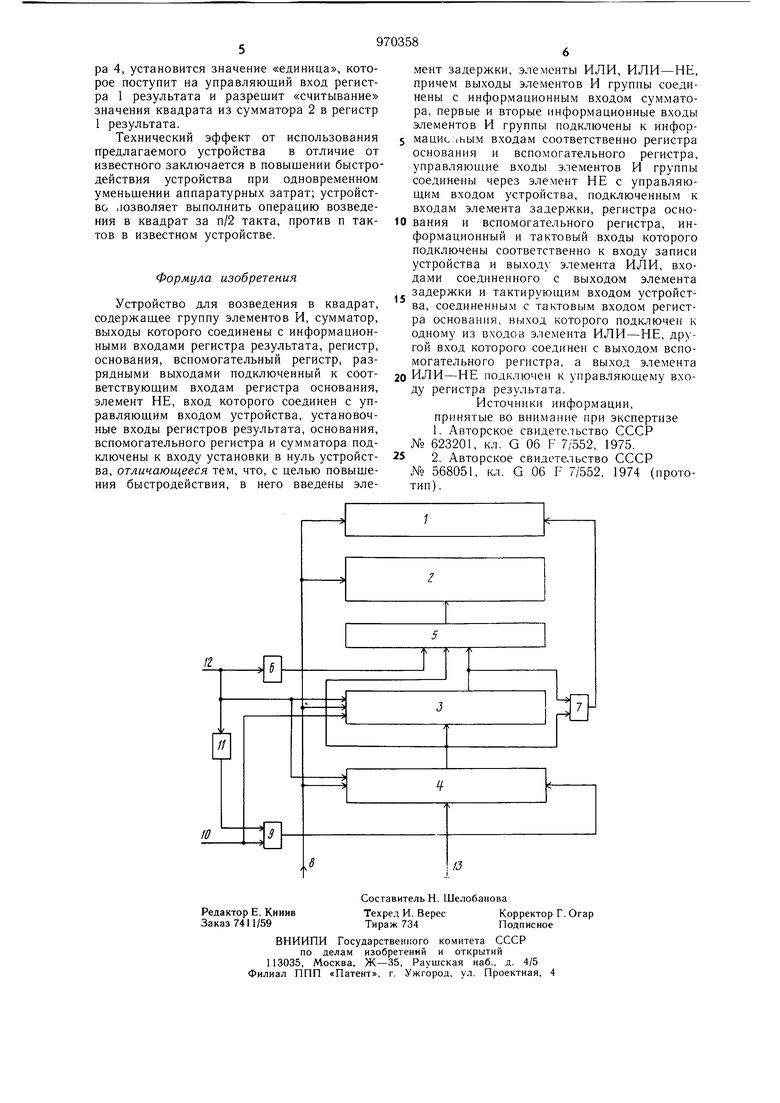

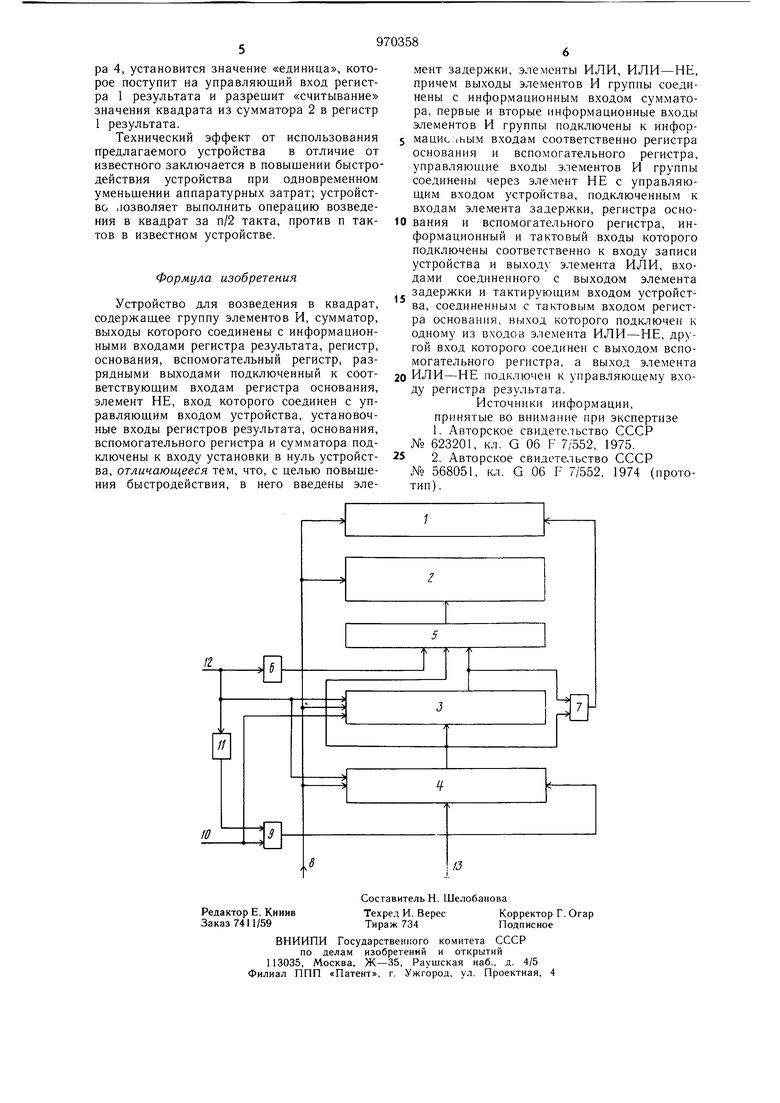

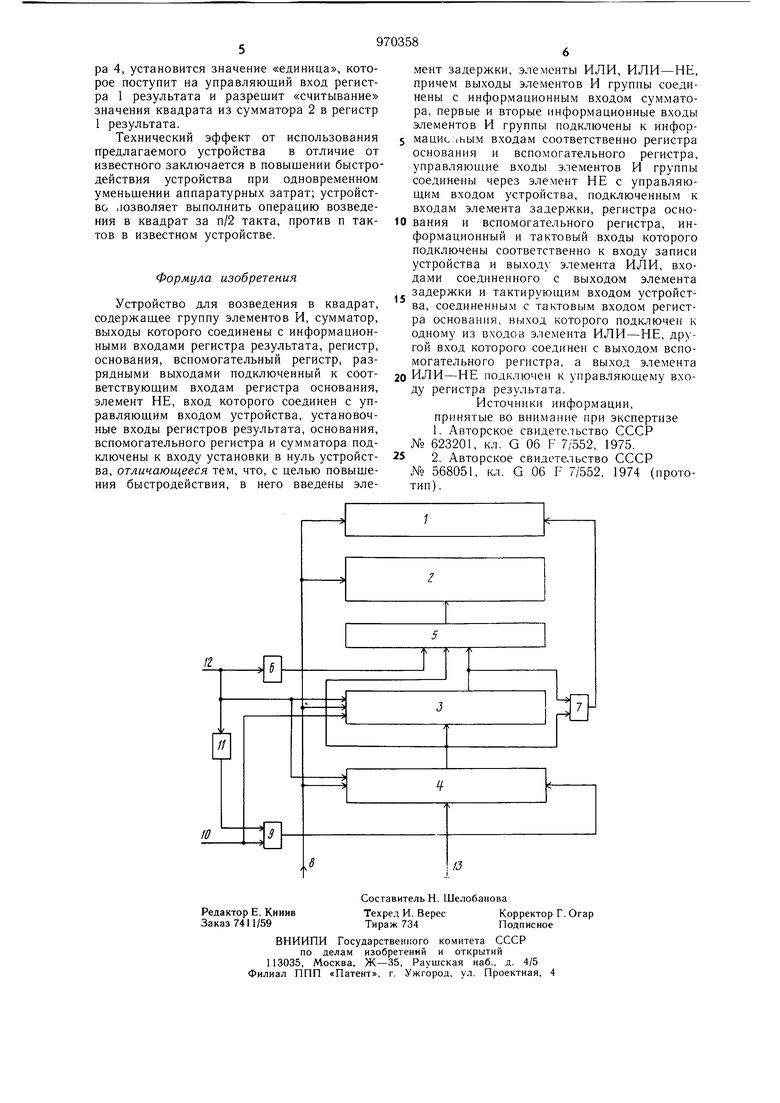

Поставленная цель достигается тем, что в устройство для возведения в квадрат, содержащее группу элементов И, сумматор, выходы которого соединены с информационными входами регистра результата, регистр основания, вспомогательный регистр, разрядными выходами подключенный к соответствующим входам регистра основания, элемент НЕ, вход которого соединен с управляющим входом устройства, установочные входы регистров результата, основания, вспомогательного регистра и сумматора подключены к входу установки в нуль устройства, введены элемент задержки, элементы ИЛИ, ИЛИНЕ, причем выходы элементов И группы соединены с информационным входом сумматора, первые и вторые информационные входы элементов И группы подключены к информационным входам соответственно регистра основания и вспомогательного регистра, управляющие входы элементов И группы соединены через элемент НЕ с управляющим входом устройства, подключенным к входам элемента задержки, регистра основания и вспомогательного регистра, информационный и тактовый входы которого подключены соответственно к входу записи устройства и выходу элемента ИЛИ, входами соединенного с выходом элемента задержки и тактирующим входом устройства, соединенным с тактовым входом регистра основания, выход которого подключен к одному из входов элемента ИЛИ-НЕ, другой вход которого соединен с выходом вспомогательного регистра, а выход элемента ИЛИ-НЕ подключен к управляющему входу регистра результата. На чертеже представлена блок-схема предлагаемого устройства. Устройство для возведения в квадрат содержит (2п-разрядные) регистр 1 результата и сумматор 2, (п-разрядные) регистр 3 основания и вспомогательный регистр 4, группу 5 элементов И, содержащую 2п элементов И, соединенных таким образом, что один из входов 2i-ro и (2i - 1)-го элементов И соединен с i-м входом регистра 3 основания, а i-ый выход вспомогательного регистра 4 подключен к одному из входов 2i-ro (2i + 1)-го элементов И группы 5 элементов И, элемент 6 НЕ, выходом соединенный с управляющими входами 2i-bix элементов И группы 5, элемент 7 ИЛИ-НЕ, шина 8 установки в «нуль. Вход 8 установки в «нуль подключен к установочным входам регистра 3 основания вспомогательного регистра 4, сумматора 2 и регистра 1 результата, управляющий вход которого соединен с выходом элемента 7 ИЛИ-НЕ, входами соединенного с 1-го по п/2-й выход вспомогательного регистра 4 и с (п/2+1)-го по п-й выход регистра 3 основания. Элемент 9 ИЛИ, выход которого подключен к тактовому входу вспомогательного регистра 4, тактовый вход 10 устройства, соединенный с первым входом элемента 9 ИЛИ, и тактовым входом регистра 3 основания. Элемент 11 задержки подключен к управляющему входу 12 устройства и входу элемента 6 НЕ и управляющим входам регистра 3 основания и вспомогательного регистра 4. Выход элемента 11 задержки соединен со вторым входом элемента 9 ИЛИ. Вход 13 записи соединен с информационными входами вспомогательного регистра 4. Вычисление квадрата числа сводится к выполнению операции суммирования над следующими выражениями in-in-iO i-i...ij-igij-yO n-n-i inin-2-1 n-in-2 -j j-i 0 in-2 0 -n-Sl in-n-i-M-i j-0 ij-0-1i -O n/2-f,-0 in/24° «/г где ii,,-.-n-значения разрядов основания; l,2,...,n -номер соответствующего разряда. Из анализа выражений видно, что, начиная со второго выражения, каждое последующее выражение получается путем встречного сдвига значения основания, записанного в двух регистрах на один разряд. Таким образом, через п/2 тактов суммирования логическое произведение соответствующих разрядов будет всегда равно нулю. Устройство работает следующим образом. Перед началом работы устройства на вход 8 установки в «ноль подается сигнал логической единицы, устанавливающей регистры 3 и 1 основания и результата, сумматор 2 и вспомогательный регистр 4 в «нуль. По входу 13 записи на информационные входы вспомогательного регистра 4 поступает значение основания, которое по сигналу логической единицы на управляющем входе 12 устройства записывается в соответствующие разряды регистра, а с его выходов - в разряды регистра 3 основания. Группа 5 элементов И выполняет операцию логического умножения над значениями соответствующих разрядов вспомогательного регистра 4 и регистра 3 основания, результат которой поступает на входы накапливающего сумматора 2. Длительность управляющего сигнала должна быть не больше времени, определяемого инерцией регистра 3 основания, вспомогательного регистра 4, группы 5 элементов И и сумматора 2. Через время задержки элемента 11 задержки значение «единица через элемент 9 ИЛИ поступает на тактовый вход вспомогательного регистра 4; значение операнда сдвигается на один такт влево, и произведение с выходов группы 5 элементов И поступает на входы сумматора 2, где суммируется со значением, находящимся на сумматоре. Через время, определяемое инерционностью сумматора 2, на тактовый вход 10 устройства подается последовательность тактовых импульсов. С приходом каждого импульса, значение, записанное в регистре 3 основания, сдвигается на один разряд вправо, а значение, записанное во вспомогательном регистре 4 - на один разряд влево. Группа 5 элементов И выполняет поразрядное умножение новых значений операндов, результат которого поступает на сумматор 2, где суммируется со значением, находящимся в нем после предыдущих циклов суммирования. После выполнения п/2 тактов сдвига во всех разрядах с (n/2-f 1)-го по п-й разряд регистра 3 основания и с 1-го по п/2-й разряд вспомогательного регистра 4 будут находиться нули. В результате на выходе элемента 7 ИЛИ-НЕ, входами подключенного к соответствующим разрядам регистра 3 основания и вспомогательного регистpa 4, установится значение «единица, которое поступит на управляющий вход регистра 1 результата и разрешит «считывание значения квадрата из суммато-ра 2 в регистр 1 результата.

Технический эффект от использования предлагаемого устройства в отличие от известного заключается в повышении быстродействия устройства при одновременном уменьшении аппаратурных затрат; устройство позволяет выполнить операцию возведения в квадрат за п/2 такта, против п тактов в известном устройстве.

Формула изобретения

Устройство для возведения в квадрат, содержащее группу элементов И, сумматор, выходы которого соединены с информационными входами регистра результата, регистр, основания, вспомогательный регистр, разрядными выходами подключенный к соответствующим входам регистра основания, элемент НЕ, вход которого соединен с управляющим входом устройства, установочные входы регистров результата, основания, вспомогательного регистра и сумматора подключены к входу установки в нуль устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены эле/2

6

мент задержки, элементы ИЛИ, ИЛИ-НЕ, причем выходы элементов И группы соединены с информационным входом сумматора, первые и вторые информационные входы элементов И группы подключены к информацисльым входам соответственно регистра основания и вспомогательного регистра, управляющие входы элементов И группы соединены через элемент НЕ с управляющим входом устройства, подключенным к входам элемента задержки, регистра основания и вспомогательного регистра, информационный и тактовый входы которого подключены соответственно к входу записи устройства и выходу элемента ИЛИ, входами соединенного с выходом элемента задержки и тактирующим входом устройства, соединенным с тактовым входом регистра основания, выход которого подключен к одному из входов элемента ИЛИ-НЕ, другой вход которого соединен с выходом вспомогательного регистра, а выход элемента

0 ИЛИ-НЕ подключен к управляющему входу регистра результата.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР jVo 623201, кл. G 06 F 7/552, 1975.

N° 568051, кл. G 06 F 7/552, 1974 (прототип).

Авторы

Даты

1982-10-30—Публикация

1981-02-16—Подача