113

Изобретение относится к вычислительной технике и предназначено для формирования суммы квадратов трех величин.

Цель изобретения - расширение клас са решаемых задач за счет возможности формирования суммы квадратов трех величин .

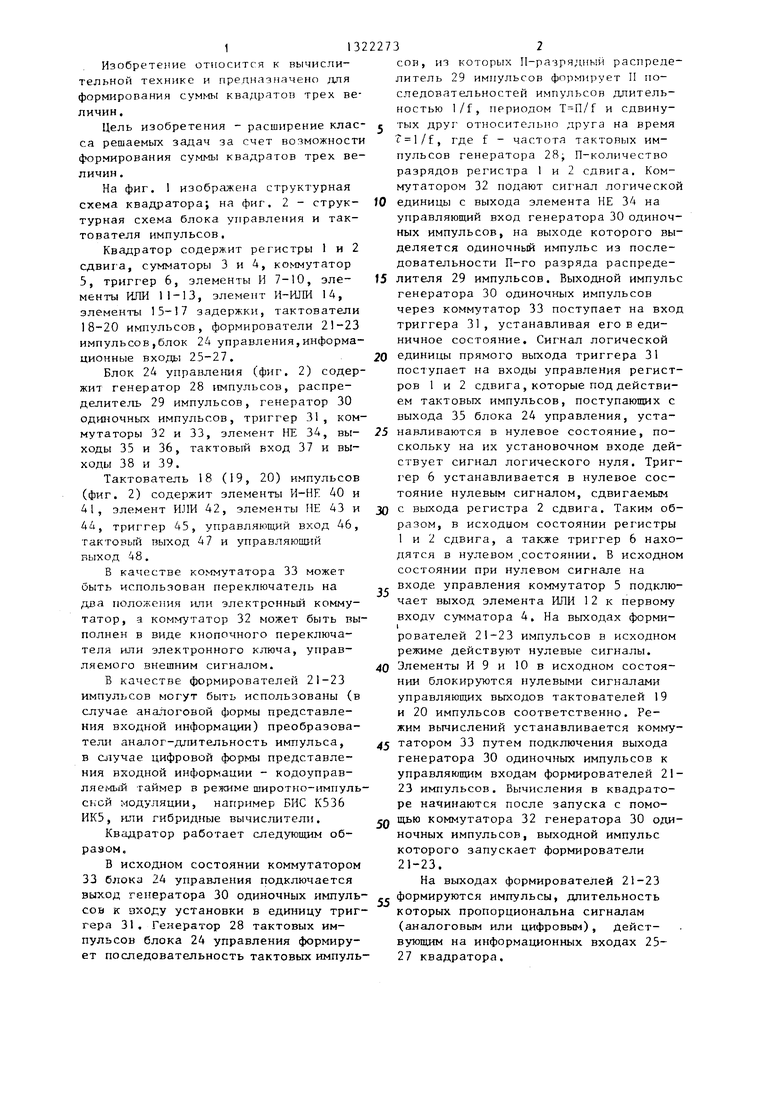

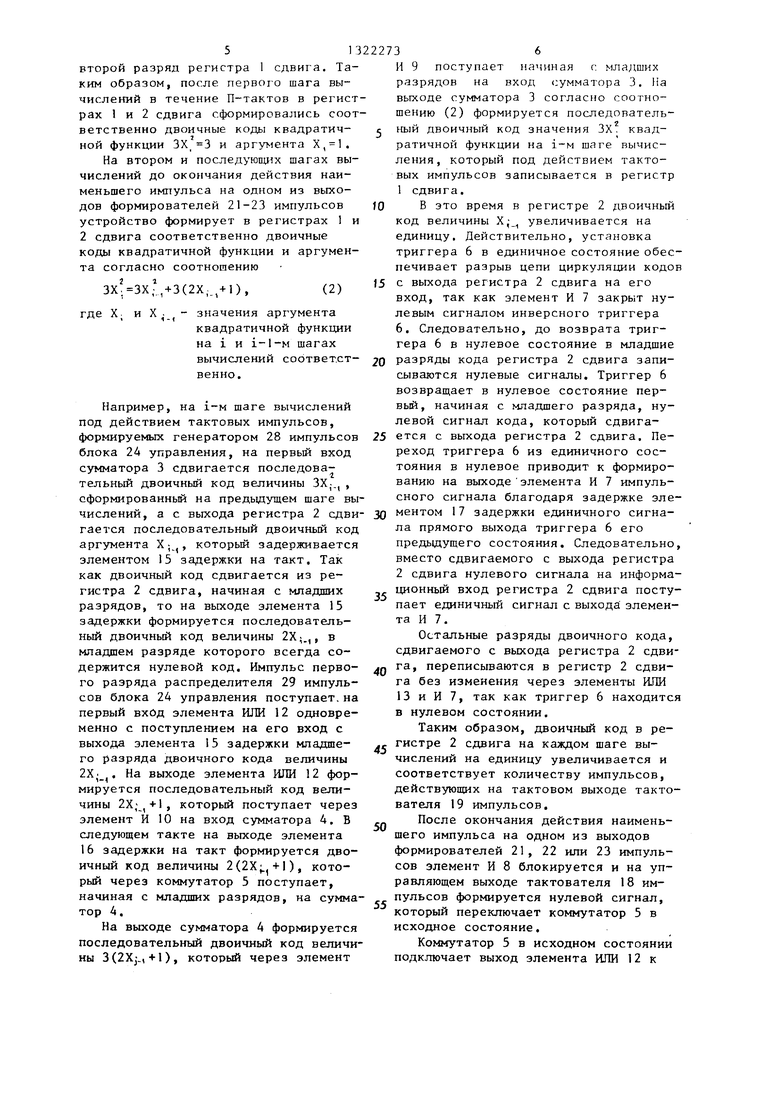

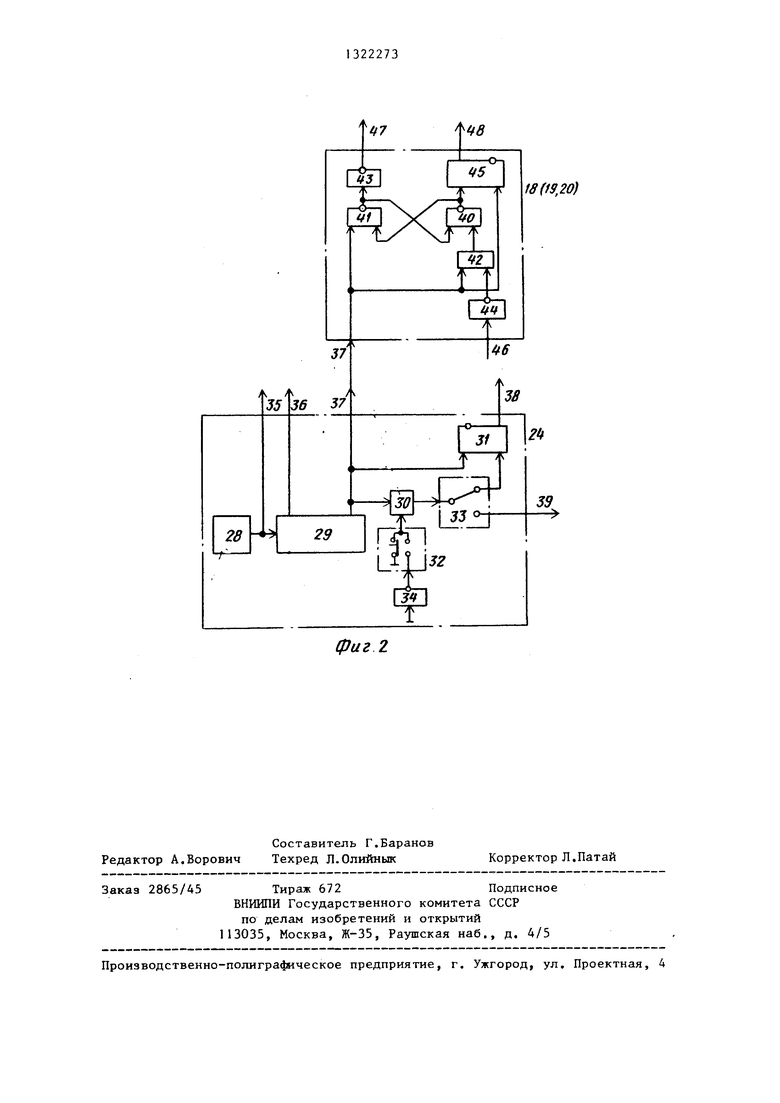

На фиг. 1 изображена структурная схема квадратора; на фиг. 2 - струк- турная схема блока управления и так- тователя импульсов.

Квадратор содержит регистры 1 и 2 сдвиг а, сумматоры 3 и 4, коммутатор 5, триггер 6, элементы И 7-10, эле- менты ИЛИ 11-13, элемент И-ИЛИ 14, элемен1Ъ1 15-17 задержки, тактователи 18-20 импульсов, формирователи 21-23 импульсов,блок 24 управления,информационные входы 25-27.

Блок 24 управления (фиг. 2) содержит генератор 28 импульсов, распределитель 29 импульсов, генератор 30 одиночных импульсов, триггер 31, коммутаторы 32 и 33, элемент НЕ 34, вы- ходы 35 и 36, тактовый вход 37 и выходы 38 и 39.

Тактователь 18 (19, 20) импульсов (фиг. 2) содержит элементы И-НЕ 40 и 41, элемент ИЛИ 42, элементы НЕ 43 и 44, триггер 45, управляющий вход 46, тактовый выход 47 и управляющ 1й выход 48.

В качестве коммутатора 33 может быть использован переключатель на два положения или электронный коммутатор, а коммутатор 32 может быть выполнен в виде кнопочного переключателя или электронного ключа, управляемого внешним сигналом.

В качестве формирователей 21-23 импульсов могут быть использованы (в случае аналоговой формы представления входной информации) преобразователи аналог-длительность импульса, в случае цифровой формы представления входной информации - кодоуправ- ляемьш таймер в режиме широтно-импуль сксй модуляции, например БИС КЗ36 ИК5, или гибридные вычислители.

Квадратор работает следующим образом.

В исходном состоянии коммутатором 33 блока 24 управления подключается выход генератора 30 одиночных импульсов к аходу установки в единицу триггера 31, Генератор 28 тактовых импульсов блока 24 управления формирует последовательность тактовых импуль

5 0

5

О

с Q

Q

5

32

сов, из которых П-разрядный распределитель 29 импульсов формирует П последовательностей импульсов длительностью 1/f, гтериодом и сдвинутых друг относительно друга на время /, где f - частота тактовых импульсов генератора 2В; П-количество разрядов регистра 1 и 2 сдвига. Коммутатором 32 подают сигнал логической единицы с выхода элемента НЕ 34 на управляющий вход генератора 30 одиночных импульсов, на выходе которого выделяется одиночный импульс из последовательности П-го разряда распределителя 29 импульсов. Выходной импульс генератора 30 одиночных импульсов через коммутатор 33 поступает на вход триггера 31, устанавливая его в единичное состояние. Сигнал логической единицы прямого выхода триггера 31 поступает на входы управления регистров 1 и 2 сдвига,которые под действием тактовых импульсов, поступающих с выхода 35 блока 24 управления, устанавливаются в нулевое состояние, поскольку на их установочном входе действует сигнал логического нуля. Триг- 1 ер 6 устанавливается в нулевое состояние нулевым сигналом, сдвигаемым с выхода регистра 2 сдвига. Таким образом, в исходном состоянии регистры 1 и 2 сдвига, а также триггер 6 находятся в нулевом ,состоянии. В исходном состоянии при нулевом сигнале на входе управления коммутатор 5 подключает выход элемента ИЛИ 12 к первому

входу сумматора 4. На выходах форми- I

рователей 21-23 импульсов в исходном режиме действуют нулевые сигналы. Элементы И 9 и 10 в исходном состоянии блокируются нулевыми сигналами управляющих выходов тактователей 19 и 20 импульсов соответственно. Режим вычислений устанавливается коммутатором 33 путем подключения выхода генератора 30 одиночных импульсов к управляющим входам формирователей 21- 23 импульсов. Вычисления в квадраторе начинаются после запуска с помощью коммутатора 32 генератора 30 одиночных импульсов, выходной импульс которого запускает формирователи 21-23.

На выходах формирователей 21-23 формируются импульсы, длительность которых пропорциональна сигналам (аналоговым или цифровым), Действующим на информационных входах 25- 27 квадратора.

Если длительность выходных им- пульсоп формирователей 21-23 различна, то наибольший по длительности импульс выделяется на выходе элемента ИЛИ 11, а импульс наименьшей длитель- ности - на выходе элемента И 8, под действием которого тактователь 18 импульсов формирует из последовательности импульсов П-го разряда распределителя 29 импульсов строб пачки импульсов, количество которых пропорционально наименьшей величине, действующей на одном из информационных входов 25-27 квадратора. Строб, дей- ствуюп1ий на управляющем выходе такто- вателя 18 импульсов, переключает коммутатор 5 в состояние, в котором выход элемента 16 задержки на такт подключается к первому входу сумматора 4.

Под действием наибольшего импульса, поступающего с выхода элемента

ИЛИ 11, тактователь 19 импульсов формирует из последовательности импульсов П-го разряда распределителя 29 импульсов блока 24 управления пачку импульсов, количество которых пропорционально наибольшей величине, действующей на одном из информационных входов 25-27 квадратора, и строб пачки импульсов квадратора наибольшей величины. Строб, действующий на управляющем выходе тактователя 19 импулы сов, открывает элемент И 9, а пачка импульсов, действующая на его тактовом выходе поступает на вход установки в единицу триггера 6.

Элемент И-ИЛИ I4 вьщеляет из выходных сигналов формирователей 21-23 импульс, длительность которого больше наименьшего, но меньше наибольшего импульса. При любой комбинации импульсов, когда на выходах формирователей 21-23 импульсов действуют одновременно не менее двух импульсов, на выходе элемента И-ИЛИ действует единичный сигнал.

В течение первого такта выходной сигнал первого разряда распределителя 29 импульсов блока управления поступает через элементы ИЛИ 12 и И 10 на вход сумматора 4, с выхода которого этот импульс через элемент И 9 и сумматор 3 под действием тактовых импульсов записывается в первый разряд регистра 1 сдвига. В следующем такте выходной импульс элемента ИЛИ I2 дей50

Если процесс формирования импульсов наименьшей и средней длительности завершился, то на выходе элемента И-ИЛИ 14 формируется нулевой сигнал.

Тактователь 20 импульсов, управляемый выходным сигналом элемента И-ИЛИ, формирует на управляющем выходе строб пачки импульсов, количество ко-55 ствует на выходе элемента 16 задерж- торых пропорционально средней вели- ки и через коммутатор 5, сумматор 4, чине, действующей на одном из инфор- элемент И 9 и сумматор 3 записывается

мационных входов 25-27 квадратора.

34

Обозначим величины, действующие на информационных входах 25-27 соответственно через X, У и Z. Допустим, что . В этом случае алгоритм работы устройства описывается следующим соотношением:

x +y%z 3 Z: (2i-t-l)-t-2

2-1i o

+ Z: (2i+l).

-a

ч (

Устройство реализует этот алгоритм следующим образом. Первый импульс пачки, действующей на тактовом выходе тактователя 19, устанавливает в единичное состояние триггер 6 в П-м такте (соответствующем сдвигу П-х разрядов кодов с выходов регистров 1 и 2 сдвига). Установка триггера 6 в единичное состояние приводит к формированию на его инверсном выходе нулевого сигнала, блокирующего элемент И 7, а на прямом выходе - единичного сигнала, который спустя время задержки элементом 17 задержки на такт начнет действовать через элемент ИЛИ 13 на втором входе элемента И 7, Под действием тактовых импульсов с выхода регистра 2 сдвига в первом такте сдвигается младший разряд начального нулевого кода, сигнал которого поступает на инверсный вход сброса триггера 6 и устанавливает его в нулевое состояние, В нулевом состоянии на инверсном выходе триггера 6 фор- мируется единичный сигнал, который снимает блокировку элемента И 7, Благодаря задержке элементом 17 задержки на такт сигнала прямого выхода триггера 6 на выходе элемента И 7 формируется импульсный сигнал, который в первом такте под действием тактовых импульсов записывается в качестве младшего разряда кода в регистр 2 сдвига.

В течение первого такта выходной сигнал первого разряда распределителя 29 импульсов блока управления поступает через элементы ИЛИ 12 и И 10 на вход сумматора 4, с выхода которого этот импульс через элемент И 9 и сумматор 3 под действием тактовых импульсов записывается в первый разряд регистра 1 сдвига. В следующем такте выходной импульс элемента ИЛИ I2 дей

ствует на выходе элемента 16 задерж- ки и через коммутатор 5, сумматор 4, элемент И 9 и сумматор 3 записывается

под действием тактовых импульсов во

второй разряд регистра 1 сдвига. Таким образом, после первого шага вычислений в течение П-тактов в регистрах 1 и 2 сдвига сформировались соответственно двоичные коды квадратичной функции и аргумента Х,1.

На втором и последующих шагах вычислений до окончания действия наименьшего импульса на одном из выходов формирователей 21-23 импульсов устройство формирует в регистрах 1 и 2 сдвига соответственно двоичные коды квадратичной функции и аргумента согласно соотношению

, + 3(2Х,,н-1), (2)

где X; и X - значения аргумента

квадратичной функции на i и i-1-м шагах вычислений соответственно.

Например, на i-м шаге вычислений под действием тактовых импульсов, формируемых генератором 28 импульсов блока 24 управления, на первый вход сумматора 3 сдвигается последовательный двоичный код величины ЗХ,-,, , сформированньй на предыдущем шаге вычислений, а с выхода регистра 2 сдви гается последовательный двоичный код аргумента X ;, который задерживается элементом 15 задержки на такт. Так как двоичный код сдвигается из регистра 2 сдвига, начиная с младших разрядов, то на выходе элемента 15 задержки формируется последовательный двоичный код величины 2Х.,, в младшем разряде которого всегда содержится нулевой код. Импульс первого разряда распределителя 29 импульсов блока 24 управления поступает.на первый вход элемента ИЛИ 12 одновременно с поступлением на его вход с выхода элемента 15 задержки младшего разряда двоичного кода величины 2Х;,. На выходе элемента ШШ 12 формируется последовательный код величины , который поступает через элемент И 10 на вход сумматора 4. В следующем такте на выходе элемента 16 задержки на такт формируется двоичный код величины 2(2Х;.+), который через коммутатор 5 поступает, начиная с младших разрядов, на сумма тор 4.

На выходе сумматора 4 формируется последовательный двоичный код величи ны 3(2Xj.,+1), который через элемент

fO

15

20

25

30

35

40

45

50

55

И 9 поступает начиная с младших разрядов на вход :умматора 3. На выходе сумматора 3 согласно соотношению (2) формируется последовательный двоичный код значения ЗХ квадратичной функции на i-M шаге вычисления, который под действием тактовых импульсов записывается в регистр

1сдвига.

В это время в регистре 2 двоичный код величины Х; увеличивается на единицу. Действительно, установка триггера 6 в единичное состояние обеспечивает разрыв цепи циркуляции кодов с выхода регистра 2 сдвига на его вход, так как элемент И 7 закрыт нулевым сигналом инверсного триггера 6. Следовательно, до возврата триггера 6 в нулевое состояние в младшие разряды кода регистра 2 сдвига записываются нулевые сигналы. Триггер 6 возвращает в нулевое состояние пер- вьй, начиная с младшего разряда, нулевой сигнал кода, который сдвигается с выхода регистра 2 сдвига. Переход триггера 6 из единичного состояния в нулевое приводит к формированию на выходе элемента И 7 импульсного сигнала благодаря задержке элементом 17 задержки единичного сигнала прямого выхода триггера 6 его предыдущего состояния. Следовательно, вместо сдвигаемого с выхода регистра

2сдвига нулевого сигнала на информационный вход регистра 2 сдвига поступает единичный сигнал с выхода элемента И 7.

Остальные разряды двоичного кода, сдвигаемого с выхода регистра 2 сдвига, переписываются в регистр 2 сдвига без изменения через элементы ШШ 13 и И 7, так как триггер 6 находится в нулевом состоянии.

Таким образом, двоичный код в регистре 2 сдвига на каждом шаге вычислений на единицу увеличивается и соответствует количеству импульсов, действующих на тактовом выходе такто- вателя 19 импульсов.

После окончания действия наименьшего импульса на одном из выходов формирователей 21, 22 или 23 импульсов элемент И 8 блокируется и на управляющем выходе тактователя 18 импульсов формируется нулевой сигнал, который переключает коммутатор 5 в исходное состояние.

Коммутатор 5 в исходном состоянии подключает выход элемента ИЛИ 12 к

713

первому входу су(-1матора 4, другой вход которого чppe. элемент Н 10 также подключен к пыходу элемента 1ШИ 12

На интервале времени от момента окончания наименьшего до момента окончания среднего импульса на выходах формирователей 21-23 импульсов устройство реализует следующее соотношение :

,, (Х +2yJ ) +2 (2У + 1 ) , (3)

где X - наименьшая входная величина,

У - средняя входная величина. К моменту окончания наименьшего импульса на j-м шаге вычислений в регистре 1 сдвига формируется согласно соотношению (2) двоичный код величины ., а в регистре 2 сдвига - двоичный код наименьшей величины , который с помощью элемента 15 задержки удваивается. На вькоде элемента ИЛИ 12 формируется двоичный код величины 2yj+l, так как в младший разряд записывается импульс первого разряда распределителя 29 импульсов блока 24 управления. Последовательный двоичный код величины 2У:+1 с выхода элемента ИЛИ 12 поступает через коммутатор 5 и элемент И 10 соответственно на первый и второй входы сумматора 4, на выходе которого формируется двоичньй код величины 2(2yj +

+ 1).

На первый и второй входы сумматора 3 поступают двоичный код величины

2 2

X +2У;, сдвигаемый под действием тактовых импульсов с выхода регистра 1 сдвига, и двоичный код величины 2(2У.+1), действующий на выходе сумматора 4 через элемент И 9. Результат суммирования, соответствующий соотношению (3), записывается под действием тактовых импульсов в регистр 1 сдвига.

В это же время на (j+l)M шаге вычислений двоичный код в регистре 2 сдвига за время П-тактов в процессе циркуляции через элементы ИЛИ 13 и И 7 увеличивается на единицу младшего разряда описанным образом.

На всех последующих шагах вычисления выполняются аналогично до момента окончания на К-м шаге среднего импульса входной величины У. К этому моменту времени Б регистре 1 сдвига сформировался согласно соотношению

л 2

(3) двоичный код величины X +2У x +y +Z, а в регистре 2 сдвига - двоичный код средней величины .

22738

После окончания действия среднего импульса входной величины У на управляющем выходе тактователя 20 импульсов формируется нулевой сигнал, KOTopbrfi блокирует элемент И 10.

В этом случае устройство реализует следующее соотношение:

X У +Z, (X +У +Z) + (), (4)

где Х,У HZ- соответственно наименьшая, средняя и наибольшая входные величины. Действительно, на (K-t-l)-M шаге двоичный код величины Z, сдвигаемый под действием тактовых импульсов из регистра 2 сдвига, удваивается с помощью элемента 15 задержки на такт. На выходе элемента ИЛИ 12 формируется двоичный код величины , который через коммутатор 5, сумматор 4 и элемент И 9 поступает на вход сумматора 3, на другой вход которого с выхода регистра 1 сдвигается двоичный код величины X +У +7

Результат суммирования, соответ- ствуюш}1Й соотношению (4), записывается под действием тактовых импульсов в регистр 1 сдвига.

Одновременно на (К+1)-м шаге вы- чиспений, как было ранее описано, двоичный код в регистре 2 сдвига увеличивается на единицу младшего разряда.

Вычисления на всех последующих шагах выполняются аналогично до момен- та окончания наибольшего импульса входном величины Z. После окончания наибольшего импульса на выходе элемента ИЛИ 11 устанавливается нулевой сигнал, который формирует на выходах тактователя 19 импульсов нулевые сигналы, блокирующие триггер 6 и элемент И 9,

Процесс вычисления суммы квадратов трех величин завершается, а в ре- гистре 1 сдвига запоминается динамическим способом результат вычислений путем циркуляции двоичного кода величины -t-Z через сумматор 3 с выхода регистра 1 сдвига на его ин- формациониый вход под действием тактовых импульсов.

В регистре 2 сдвига запоминается динамическим способом, путем циркуляции кода через элементы ИЛИ 13 и И 7, двоичный код наибольшей входной величины Z .

Тактователь 18 (19, 20) импульсов (фиг. 2) работает следующим образом. На тактовый вход 37 поступает после

донательность импульсов, а на управляющий вход 46 - сигнал управления.

В случае отсутствия сигна.па управления на входе 46, на выходе элемента НЕ 44 устанавливается сигнал логи- ческой единицы, поступающий через элемент ИЛИ 42 на один из входов элемента И-НЕ 40. Во время паузы между импульсами на входе 37 на выходе элемента И-НЕ 41 формируется сигнал логи- ческой единицы, который совместно с единичным сигналом выхода элемента ИЛИ 42 устанавливает на выходе элемента И-НЕ 40 сигнал логического нуля, блокирующий элемент И-НЕ 41 во время действия импульсов на входе 37. Сигнал логической единицы выхода элемент И-НЕ 41 поддерживает сигнал логического нуля на выходе элемента НЕ 43. Триггер 45 находится в нулевом состоянии, в которое его устанавливают импульсы, действующие на входе 37.

В случае действия единичного сигнала на входе 46 управления на выходе элемента НЕ 44 устанавливается сигнал логического нуля. Во время паузы между импульсами на входе 37 на выходе элемента ИЛИ 42 устанавливается сигнал логического нуля, формирующий на выходе элемента И-НЕ 40 единичный сигнал, который пропускает последовательность импульсов входа 37 через элементы И-НЕ 41 и НЕ 43 на тактовый выход 47 тактователя импульсов. В этом режиме во время действия импульса на входе 37 нулевой сигнал на выходе элемента И-НЕ 41 блокирует элемент И-НЕ 40, на выходе которого поддерживается сигнал логической единицы.

Единичный сигнал выхода элемента И-НЕ 40 устанавливает триггер 45 в единичное состояние, в котором он находится до тех пор, пока на управляющем входе 46 действует единичный сигнал. После окончания действия управляющего сигнала на входе 46 триггер 45 сбрасывается в нулевое состояние импульсом, действующим на входе 37. На прямом выходе триггера 45 формируется сигнал строба, поступающий на управляющий выход 48 тактователя импульсов.

Предлагаемое устройство, кроме

формирования суммы квадратов трех ве- входом коммутатора, управляющий вход личин, может использоваться в режи- которого соединен с управляющим вы- ме формирования суммы квадратов двух величин или в режиме формирования

ходом первого тактователя импульсов,- выход второго регистра сдвига соединен с входом первого элемента задержквадратичной функции. Когда входные

7310

сигналы действуют только на двух информационных входах устройства, а на третий информационный вход поступает нулевой сигнал, устройство формирует сумму квадратов двух величин. Если только на один информационный вход поступает входной сигнал, а на двух других входах устройства действуют нулевые сигналы, то устройство формирует квадратичную функцию.

Формула изобретения

Квадратор, содержащий два регист- ра сдвига, первый сумматор, коммутатор, триггер, три элемента И, три элемента ИЛИ, три элемента задержки, два формирователя импульсов, два тактователя импульсов, блок управления, первый выход которого соединен с входами синхронизации первого и второго регистров сдвига, второй выход - с входами управления сдвигом первого и второго регистров сдвига, установочные входы которых подключены к входу логического нуля квадратора, а информационные входы первого и второго регистров сдвига соединены с выходами первого сумматора и первого элемента И соответственно, третий вькод блока управления соединен с тактовыми входами первого и второго тактователей импульсов, управляющие входы которых подключены соответственно к выходам второго элемента И и первого элемента ШШ, четвертый выход блока управления соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом первого элемента задержки, пятый выход блока управления подключен к управляющим входам первого и второго формирователей импульсов, информационные входы которых являются соответственно входами первого и второго аргументов квадратора, выход первого регистра сдвига соединен с первым входом первого сумматора, второй вход которого соединен с выходом третьего элемента И, выход второго элемента ИЛИ соединен непосредственно с первым информационным входом коммутатора и через второй элемент задержки - с вторым информационным

входом коммутатора, управляющий вход которого соединен с управляющим вы-

ходом первого тактователя импульсов,- выход второго регистра сдвига соединен с входом первого элемента задержки, г первым входом третьего элемента ИЛИ и с входом установки в О триггера, инверсный выход которого соединен с первым входом первого элемента И, прямой выход триггера соединен через третий элемент задержки с вторым входом третьего элемента ИЛИ, выход которого подключен к второму входу первого элемента И, вход установки в 1 триггера соединен с тактовым выходом второго тактователя импульсов, управляющий выход которого соединен с первым входом третьего элемента И, выходы первого и второго формирователей импульсов соединены соответственно с первыми и вторыми входами первого элемента ИЛИ и второго элемента И, отличающий- с я тем, что, с целью расширения класса решаемых задач за счет возможности формирования суммы квадратов трех величин, в него введены второй сумматор, третий формирователь импульсов и третий тактователь импульсов, четвертый элемент И и элемент И-ИЛИ, причем второй вход третьего элемента И соединен с выходом второго сумматора, первый и второй входы которого соединены с выходами коммутатора и

четвертого элемента И соответственно, первый и второй входы которого подключены соответственно к управляющему выходу третьего формирователя импульсов и выходу второго элемента ПТИ, тактовый и управляющий входы третьего тактователя импульсов соединены с третьим выходом блока управления и выходом элемента И-ИЛИ соответственно, пятый выход блока управления соединен с управляющим входом третьего формирователя импульсов, информационный вход которого является входом третьего аргумента квадратора,

выход первого формирователя импульсов соединен с первыми входами первой и второй групп входов элемента И-Ш1И, вторые входы первой и второй групп входом которого подключены к выходам

соответственно второго и третьего формирователей импульсов, первый и второй входы третьей группы входов элемента И-ИЛИ соединены с выходами соответственно второго и третьего

формирователей импульсов, третьи входы первого элемента ИЛИ и второго элемента И соединены с выходом третьего формирователя импульсов .

18(19,20)

фиг 2

Редактор А.Ворович

Составитель Г.Баранов Техред Л.Олийнык

2865/45

Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор Л.Патай

| название | год | авторы | номер документа |

|---|---|---|---|

| Квадратор | 1985 |

|

SU1258826A2 |

| Квадратор | 1987 |

|

SU1501049A1 |

| Устройство для вычисления суммы квадратов трех величин | 1988 |

|

SU1580356A1 |

| Квадратор | 1983 |

|

SU1180885A1 |

| Устройство для контроля экспоненциальных процессов | 1987 |

|

SU1500997A1 |

| Устройство для вычисления полинома второй степени | 1983 |

|

SU1109743A1 |

| Устройство для вычисления полинома второй степени | 1982 |

|

SU1026140A1 |

| Интегро-дифференциальный вычислитель | 1980 |

|

SU955051A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

Изобретение относится к вычислительной технике и предназначено как для возведения в квадрат, так и пля формирования суммы квадратов трех величин, представленных в цифровой или аналоговой форме. Цель изобретения - расширение класса решаемых задач за счет возможности формирования суммы квадратов трех величин. Указанная цель достигается за счет того, что в устройство, содержащее регистры 1, 2 сдвига, сумматор 3, триггер 6, коммутатор 5, элементы И 7-10, элементы ИЛИ 11-13, элементы 15-17 задержки, тактователи 18, 19 импульсов, формирователи импульсов 21, 22, блок управления 24, введены сумматор 4, элемент И-ИЛИ 14, формирователь 23 импульсов и тактователь 20 импульсов. 2 ил. С (Л

| Устройство для вычисления суммы квадратов к чисел | 1977 |

|

SU717759A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Квадратор | 1983 |

|

SU1180885A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-07—Публикация

1986-01-07—Подача