97

второго ключа соединен с единичным выходом триггера управления ключами, вход второго ключа соединен с выходом циФроаналогового преобразователя, управляющий вход которого связан с третьим вь ходом распределителя тактовых импульсов, а информационный вход - с информационными выходами блока памяти и регистров максиггума и минимума, информационные входы регистров максимума и М11нимума подсоединены к информационному выходу блока памяти, информационные выходы блока памяти и регистров максимума и . минимума подключены к информационному выходу устройства, входы управления выдачей кода регистров максимума и минимума соединены с первым и вторым выходами первого дешифратрра соответственно, входы управления занесением кода регистров максимума и миниг-гума связаны с первым и вторым выходами второго дешифратора соответственно, управляющий вход; Пу.ск

блока памяти соединен с выходом пусковых импульсов блока изменения режимов работы, управляющий вход разрешения выдачи кода блока памяти подключен к четвертому выходу распределителя тактовых импульсов, выходы сдвигового регистра соединены с входами третьего дешифратора, выход Готов код блока памяти подключен к соответствующему входу блока изменения режимов работы, установочные входы блока памяти, сдвигового регистра, цифроаналогового преобразователя, регистра максимума и регистра минимума подсоединены к установочному выходу блока изменения режимов работы, входная кодовая шина блока изменения режимов работы соединена с входной кодовой шиной режимов работы всего устройства, выходная шина кода признаков третьего дешифратора блока управления соединена с выходной шиной кода признаков всего устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| Анализатор спектра | 1984 |

|

SU1237987A1 |

| Устройство для кодирования аналоговых сигналов | 1989 |

|

SU1624696A1 |

| Многоканальный анализатор электрофизиологических сигналов | 1991 |

|

SU1806603A1 |

| Устройство приема телеметрической информации | 1989 |

|

SU1735883A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162247C2 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ НАГРУЖЕНИЕМ ПРИ ПРОГРАММНЫХ ИСПЫТАНИЯХ МЕХАНИЧЕСКИХ КОНСТРУКЦИЙ НА УСТАЛОСТНУЮ ПРОЧНОСТЬ | 2007 |

|

RU2365965C2 |

| Измеритель аналоговых сигналов | 1988 |

|

SU1599869A1 |

| Устройство для регистрации цифровой информации | 1986 |

|

SU1386915A2 |

УСТРОЙСТВО ДЛЯ ПОИСКА ЭКСТРЕМУМОВ СИГНАЛА, содержащее блок сравнения, регистр максимума, регистр минимума, блок памяти, генератор импульсов и двухразрядный сдвиговый регистр, причем к второму -входу блока сравнения подсоединен уравновешивающий выход блока памяти, выходы блока сравнения соединены с первыми входами блока памяти и с входами сдвигового регистра, выход генератора импульсов соединен с вторым входом блока памяти, отличающееся тем, что, с целью расширения функциональных возможностей устройства, в него введены два ключа, цифроаналоговый преобразователь и блок управления, который состоит из первого, второго и третьего дешифраторов, триггера управления ключами, распределителя тактовых и№пульсов, генератора тактовых импульсов, блока изменения режимов работы, счетчика пусковых импульсов, причем выходы сдвигового регистра подсоединены к входам первого, второго и третьего дешифраторов, а выходы блока сравнения подключены к входам второго и третьего Дешифраторов, первый и второй выходы распределитеВСЕ ОКЗНДЯ I 1и;;„НЕ ;;дя СлБЛИО; г,./ л ля тактовых импульсов подключены соответственно к первому и второму синхронизирующим входам сдвигового регистра, третий выход распределителя тактовых импульсов соединен с входом первого дешифратора и единичным входом триггера управления ключами, четвертый выход распределителя тактовых импульсов соединен с входами второго и третьего дешифраторов и с нулевым входом триггера управления ключами, пятый выход распределителя тактовых импульсов соединен с входом блока изменения режимов работы, установочный вход триггера управления ключами соединен с установочным выходом блока измене(Л ния режимов работы, выход генерато-ра тактовых импульсов подетючен к входам распределителя тактовых импульсов и блока изменения режимов работы, первый управляющий выход блока изменения режимов работы соединен с входом второго дешифратора, второй со to управлякяций выход блока изменения режимов работы соединен с соответствунщим входом распределителя тактоCD li СО вых, импульсов, выход пусковых импульсов блока изменения режимов работы соединен со счетным входом счетчика пусковых импульсов, первый выход которого соединен с входом второго дешифратора, а второй выход - с V входами второго и третьего дешифраторов, вход первого ключа соединен с источником входного сигнала, выходы первого и второго ключей соединены с первым входом блока сравнения, управляющий вход первого ключа соединен с нулевым выходом триггера уп(равления ключами, управляющий

Изобретение относился к цифровой измерительной технике и аналого-цифровой вычислительной технике и предназначено для поиска локальных и глобальных экстремумов, а также наименьших и наибольших значений сигнала.

Известно устройство для определения экстремальных значений сигнала, которое содержит линию задержки, ключи5 генератор импульсов, формирователи импульсов, схемы совпадения, и служит для определения величины и положения экстремумов.

Недостатком этого устройства является то, что оно может определять только локальный экстремум.

Наиболее близким техническим решением к предлагаемому является устройство, содержащее блок сравнения, регистр максимума, регистр минимума, блок памяти, генератор импульсов и двухразрядный сдвиговый регистр, причем к второму входу блока сравнения подсоединен уравновешивающий выход блока памяти,, выходы блока сравнения соединены с первыми входами блока памяти, и с входами сдвигового регистра, выход генератора импульсов

соединен с вторым входом блока памяти.

С целью расширения функциональных возможностей устройства, в него введены два ключа, цифроаналоговый преобразователь и блок управления, который состоит из первого, второго и третьего дешифраторов, триггера управления ключами, распределителя

тактовых импульсов, генератора тактовых импульсов, блока изменения режима рабЬты, счетчика пусковых имо

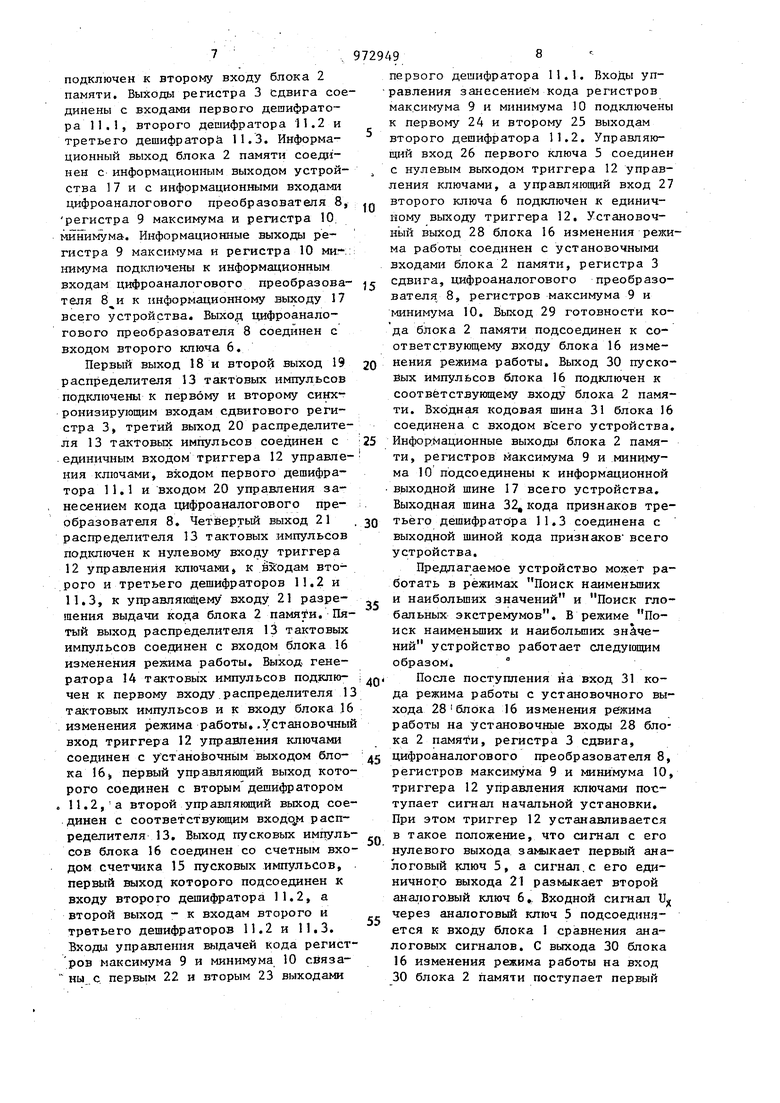

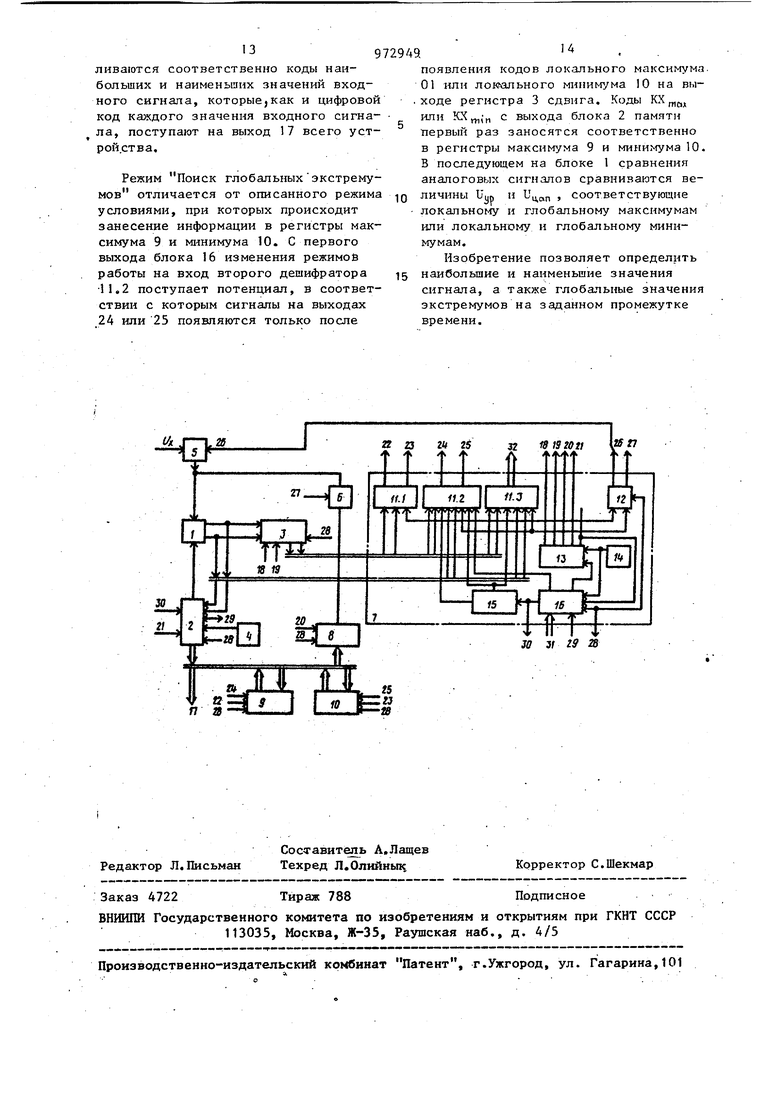

пульсов, причем к второму входу блока сравнения подсоединен уравновешивающий выход блока памяти, выход блока сравнения соединен с первым входом блока памяти и с входом сдвигового регистра, выход генератора импульсов соединен с вторым входом блока памяти, выходы сдвигового регистра подсоединены к входам перво.го, второго и третьего дешифраторов, а выходы блока сравнения подключены к входам второго и третьего дешифраторов, первый и второй выходы распределителя тактовых импульсов подключены соответственно к первому и второму синхронизирующим входам сдвигового регистра, третий выход распределителя тактовых импульсов соединен с входом первого дешифратора и единичным -.входом триггера управления : ключами, четвертый выход распределителя тактовых импульсов соединен с входами второго и третьего дешифраторов и с нулевым входом триггера управления ключами, пятый выход распределителя тактовых импульсов соеди ней с входом блока изменения .режима работы, установочный вход триггера управления ключами соединен с установочным выходом блока изменения режима работы, выход генератора тактовых импульсов подключен к входам распределителя тактовых импульсов и блока изменения реткима работы, пер вьш управляклций выход блока изменения режима работы соединен с входом второго дешифратора, второ управляющий выход блока изменени режимов работы соединенс соответствующим входом распределителя тактовых импульсов, выход пусковых импульсов блока изменения режимов работы соединен со счетным входом счетчика пусковых импульсов, первый выход коTopoFO соединен с входом второго дешифратора, а второй выход соединен с входами второго и третьего дешифра торов, вход первого ключа соединен с источником входного сигнала, выходы первого и второго ключей соединены с первым входом блока сравнения, управляющий вход первого ключа соединен, с нулевым выходом триггера управления ключами, управляющий вход вто го ключа соединен с единичным выходом триггера управления ключами, вход второго ключа соединен с выходом цифроаналогового преобразователя, управляющий вход которого связан с третьим выходом распределителя тактовых импульсов, а информационный вход - с информационными выходами блока памяти и регистров максимума и минимума, информационные входы регистров максимума и минимума подсоединены к информационному выходу блока памяти, информационные выходы блока памяти и регистров максимума и минимума подключены к информационному выходу устройства, входы управлен1м выдачей кода регистров макси; мума и минимума соединен) с первым и вторым выходами первого дешифрато ра соответственно, входы управлеиия занесением кода регистров максимума н минимума связаны с первым и BTOPLIM выходами второго дешифратора соответственно, управляющий вход Пуск блока памяти соединен с выходом пусковых импульсов блока изменения режи; мов работы, управляющий вход разрешения выдачи кода блока памяти подключен к четвертому выходу распределителя тактовых импульсов, выходы сдвигового регистра соединены с входами третьего дешифратора, выход Готов код блока памяти подключен к соответствующему входу блака изменения-фежима работы, установочные входы, блока памяти, сдвигового регистра, цифроаналогового преобразователя, регистров максимума и минимума подсоединены к установочному выходу блока изменения режима работы, входная кодовая шина блока изменения режима работы соединена с входной кодовой шиной режима работы всего устройства, выходная шина кода признаков третьего дешифратора блока управления соединена с шиной выходного кода признаков всего устройства. Структурная схема предлагаемого устройства изображена на чертеже. Она состоит из блока 1 сравнения (аналоговых сигналов), блока 2 памяти, двухразрядного сдвигового регистра 3, генератора 4 импульсов, двух аналоговых ключей 5 и 6, блока 7 управления, цифроаналогового преобразователя 8, регистра 9 мшссимума, регистра 10 минимума. Блок 7 управлейия состоит из первого дешифратора 11.1, второго дешифратора 11,2, третьего дешифратора 11,3, триггера 12 управления ключами, распределителя 13 тактовых импульсов, генератора 14 тактовых импульсов, счетчика 15 пусковых импульсов, блока 16 изменения режима работы, Вход первого ключа 5 соединен с источником входного сигнала Uj, выход первого ключа 5 соединен с выходом второго ключа бис первы входом блока 1 сравнения, второй вход блока I сравнения соединен с уравновешивакнцим выходом блока 2 памяти. Выход блока 1 сравнения подсоединен к первому входу блока 2 памяти, к входу сдвигового регистра 3, к входам второго дешифратора 11,2 и третьего дешифратора П.З блока 7 управления,. Выход генератора 4 импульсов подключен к второму входу блока 2 памяти. Выходы регистра 3 сдвига сое динены с входами первого дешифратора 1 1 , 1 , второго дешифратора 11.2 и третьего дешифратор 11.3. Информационный выход блока 2 памяти co&miиен с информационным выходом устройства 17 и с информационными входами цифроаналогового преобразователя 8, регистра 9 максимума и регистра 10. минимума. Информационные выходы регистра 9 максиьгума и регистра 10 ми-; нимума подключены к информационным входам цифроаналогового преобразователя 8 и к информационному выходу 17 всего устройства. Выход цифроаналогового преобразователя 8 соединен с входом второго ключа 6. Первый выход 18 и второй выход 19 распределителя 13 тактовых импульсов подключены к первому и второму синхронизирующим входам сдвигового регистра 3, третий выход 20 распределителя 13 тактовых импульсов соединен с единичным входом триггера 12 управления ключами, входом первого дешифратора 11.1 и входом 20 управления занесением кода цифроаналогового преобразователя 8. Четзйертый выход 21 распределителя 13 тактовых импульсов подключен к нулевому входу триггера 12 управления ключами к входам второго и третьего дешифраторов 11.2 и 11.3, к управляющему входу 21 разрешения выдачи кода блока 2 памяти. Пя тый выход распределителя 13 тактовых импульсов соединен с входом блока 16 изменения режима работы. Выход генератора 14 тактовых импульсов подключен к первому входу.распределителя 1 тактовых импульсов и к входу блока .16 изменения режима работы,.Установочны вход триггера 12 управления ключами соединен с у станоёочным выходом блока 16 первый управляющий выход кото рого соединен с вторымдешифратором . П.2, а второй управляющий выход сое динен с соответствующим входом распределителя 13. Выход пусковьк импуль сов блока 16 соединен со счетным вхо дом счетчика 15 пусковых импульсов, первый выход которого подсоединен к входу второго дешифратора 11.2, а второй выход - к входам второго и третьего дешифраторов 11.2 и 11.3. Входы управления выдачей кода регист ров максимума 9 и минимума 10 связаны с. первым 22 и вторым 23 выходами 98 первого дешифратора 11.1. Входы управлеиия занесением кода регистров максимума 9 и минимума 10 подключены к первому 24 и второму 25 выходам второго дешифратора 11.2. Управляющий вход 26 первого ключа 5 соединен с нулевым выходом триггера 12 управления ключами, а управляющий вход 27 второго ключа 6 подключен к единичному выходу триггера 12. Установочный выход 28 блока 16 изменения режима работы соединен с установочными входами блока 2 памяти, регистра 3 сдвига, цифроаналогового преобразователя 8, регистров максимума 9 и минимума 10. Выход 29 готовности кода блока 2 памяти подсоединен к соответствующему входу блока 16 изменения режима работы. Выход 30 пусковых импульсов блока 16 подключен к соответствующему входу блока 2 памяти. Входная кодовая шина 31 блока 16 соединена с входом всего устройства. Инфор:мационные выходы блока 2 памяти, регистров максимума 9 и минимума 10 подсоединены к информационной выходной шине 17 всего устройства. Выходная шина 32, кода признаков третьего дешифратора 11.3 соединена с выходной шиной кода признаков всего устройства. Предлагаемое устройство может работать в режимах Поиск наименьших и наибольших значений и Поиск глобальньпс экстремумов. В режиме Поиск наименьших и наибольших значений устройство работает следующим образом.° После поступления на вхрд 31 кода режима работы с установочного выхода 28блока 16 изменения режима работы на установочные входы 28 блока 2 памяти, регистра 3 сдвига, цифроаналогового преобразователя 8, регистров максимума 9 и минимума 10, триггера 12 управления ключами поступает сигнал начальной установки. При этом триггер 12 устанавливается в такое положение, что сигнал с его нулевого выхода за14 1кает первый аналоговый ключ 5, а сигнал.с его единичного выхода 21 размыкает второй анао;1оговый ключ 6,, Входной сигнал Uj, через аналоговый ключ 5 подсоеднндется к входу блока 1 сравнения аналоговых сигналов. С выхода 30 блока 16 изменения режима работы на вход 30 блока 2 памяти поступает первый сигнал Пуск, По этому сигналу происходит процесс автокомпенсации входного сигнала Uy . Первый сигнал Пуск поступает также на вход счет,чика 15 пусковых импульсов, после чего на первом выходе счетчика 15 появляется разрешающий потенциал, поступающий на вход второго дешифратора 11.2, После окончания автокомпенсации на аналоговом выходе блока 2 памяти устанавливается уравновешивающий сигнал Unp., равный с точностью до дискретности автокомпенсации входному сигналу.,и)( , с выхода 29 блока 2 памяти сигнал готовности кода поступает на вход блока 16 изменения режима работы.Через определенный промежуток времени, определяемый кодом, поступающим на вход 31 блока 16, с второго выхода блока 16 на соответствукяций вход распределителя 13 тактовых импульсов поступает потен цйал, который разрешает импульсам генератора 14 тактовых импульсов проходить в распределитель 13. После поступления первого импульса от генератора 14 тактовых импульсов на первый вход распределителя 13 тактовых импульсов появляется сигнал на первом 1выходе 18 распределителя 13, после появления второго импульса появляется сигнал на втором выходе 19 распределителя 13 и т.д. По сигналу с первого выхода 18 распределителя 13 в регистре 3 сдвига информация с триггера первого раз ряда переносится в триггер второго . разряда. В этот момент времени входчНой аналоговый сигнал равен значению Uyi,которое через первый аналоговый ключ 5 поступает на один вход блока 1 сравнения аналоговых сигналов. На второй вход блока 1 сравнения поступает уравновешивающий сигнал Uyp. На выходе блока 1 сравнения имеется цифровой сигнал, который определяется знаком приращения Д и, jCsigti U j.) между аналоговыми сигналами Ux,., и Uyf). Если Uxj Uyp (signAU.), то на выходе блока сравнения 1, ес ли Vy, Uj.p (sign4U j 0), то на выходе блока сравнения О. По сигналу с выхода 19 распределителя 13 тактовых импульсов с выхода блока 1 сравнения значение sigiuSUj заносится в триггер первого разряда. По сигналу с выхода 20 распределителя 13 тактовых импульсов информадия из регистра 9 максимума или из ; регистра 10 минимума заносится в регистр цифроаналогового преобразователя 8. По этому же сигналу триггер .12 управления ключами перебрасывается по единичному входу. При этом первый аналоговый ключ 5 размыкается, а второй аналоговый ключ 6 замыкается, и аналоговый сигнал с выхода цифроаналогового преобразователя 8, соответствующий коду наибольшего значения сигнала или коду Наименьшего знaJчeния сигнала, хранящегбЬя в регистрах максимума 9 или 1иннмума 10, сравнивается в блоке 1 сравнения аналоговых сигналов с сигналом Uyp . На выходе блока 1 устар1авливается цифровой сигнал, который ависит от значения знака прираще-а ния (signAU,u.,n ) ме5хду сигналами Цдоп и USP . Если Uu,, (signAU4Hj,0), на выходе блока сравнения Г , если Ua,c..,p, (signAU,p), на выходе блока сравнения О. По следующему сигналу с выхода 21 распределителя 13 тактовых импульсов в регистры максимума 9 и минимума 10 заносится значение кода КХ , соот- . ветствунщее аналоговому сигналу Uj{, i. Триггер 12 управления ключами перебрасывается по нулевому входу, выходы триггера 26 и 27 воздействуют на управляющие входы ключей 5 и 6, и аналоговый ключ 5 sahbiKaeTCH, а аналоговый ключ 6 размыкается. Следующий пятый сигнал с выхода распределителя 13 тактовых импульсов поступает на вход блока 16 изменения , режима работы, с выхода 30 которого на вход блока 2 памяти поступает второй импульс Пуск. По этому сигналу происходит процесс автокомпенсации входного сигнала Uj(, . Второй сигнал Пуск поступает также на вход счетчика 15 пусковых импульсов, после чего на его первом выходе появляется запрещающий потенциал, а на втором разрешающий, сохраняющ11йся на все последующее время работы устройства и поступающий на соответствукяцие входы второго и третьего дешифраторов 11.2 и П.З. После окончания автокомпенсации на аналоговом выходе блока 2 памяти устанавливается уравновешивающий сигнал U,jp , равный с точностью до ;ц1скретности автокомпенсации входному, сигналу Цу. , с выхода 29 блока 2 памяти сигнал готовности кода поступает на вход блока 16 измененияре жима работы. Через определенный проме)хуток вре мени, определяемый кодом на входе 31 блока 16, с второго выхода блока 16 на соответствующий вход распределителя 13 тактовых импульсов /поступает потенциал, который разрешает им пульсам генератора 14 тшстовых импульсов проходить в распределитель 13 По сигналу с первого выхода 18 распределителя 13 в регистре 3 сдвига значение , , хранящееся в триггере первого разряда, переноситс в триггер второго разряда. В этот мо мент времени входной аналоговый сигнал равен значению U , Которое через первый аналоговый ключ 5 поступает на один вход блока 1 сравнения аналоговых сигналов. На второй вход блока 1 поступает уравновешивающий сигнал Uyp,, . На выходе блока 1 сравнения имеется цифровой сигнал, который определяется значением sign/lUjj По сигналу с выхода 19 распределителя 13 тактовых импульсов с выхода блока 1 сравнения значение siguAU j заносится в триггер первого разряда. Если в триггерах 3 сдвигового регистг 1, то значение аналогора хранятся вого сигнала UK находится на возрастающем входном сигнале, а если О, то на убывающем сигнале. Если в пер- О а во втовом разряде хранится - ром, то и, является максимумом t 11I сигнала, а если в первом разряде Г, О, то Uy является ниа во втором U , нимумом сигнапа. По сигналу с выхода 20 распреде.лителя 13 на выходе 22 первого дешифратора 11.1 появляется разрешающий импульс, по которому информация из регистра максимума 9 переносится в регистр цифроаналогового преобразователя 8, если в сдвиговом регистре 3 хранится код 11 или 01 Если же в сдвиговом регистре 3 храйится код 00 или 10, то в регистр цифроаналогового преобразователя 8 переносится информация из регистра минимума 10, По этому же сигналу информация с регистров 9 и 10 поступает на выход 17 всего устройства, а триггер 12 управ ления ключами перебрасывается по единичному входу. При этом аналоговый ключ 5 размыкается, а второй аналоговый ключ 6 замыкается и, аналоговый сигнал с выхода 912 цифроаналогового преобразова теля 8, соответствующий коду наибольшего значения сигнала МАХ или коду наименьшего значения сигнала ЖЫ, хранящ11кся соответственно в регистрах максимума 9 или минимума 10, сравнивается на блоке. 1 сравнения аналоговых сигналов с сигналом Uijp- . Если на выходе блока 1 устанавливается цифровой сигнал, который зависит от величины signAUgyj, Если в регистр цифроаналогового преобразователя В был записан код из регистра максимума 9 и ,)р , то по сигналу с выхода 21 распределителя 13 тактовых импульсов разрешшгацего импульса с выхода 24 второго дешифратора П.2 нет, и в регистре максимума 9 остается значение кода., бывшее в нем ранее,, если же , то в регистр максимума 9 по сигналу с выхода 21 распределителя 13 поступает с выхода 24 второго дешифратора разрешение на занесение кода КХ с выхода блока 2 -памяти. Этот же код поступает на выход 17 всего устройства. По сигналу с выхода 25 разрешается также выдача кода признаков ° выходу 26, Если в регистр цифроаналогового преобразователя 8 бьш записан код из регистра минимума 10 и , то по сигналу с выхода 21 в регистре 10 минимума остается значение кода, бывшее в нем ра-. Нее, так как сигнал разрешения з несения с выхода 25 второго дешифратора 1Г.2 не поступает.-Если , то с выхода 25 второго дешифратора 11,2 поступает сигнал, разрешаюпщй занесение кода KXj, из блока 2 памяти в регистр минимума 10, Триггер 12 управления ключами перебрасывается по нулевому входу, и аналоговый ключ 5 замыкается, а аналоговый ключ 6 размыкается. Следующий пятый сигнал с выхода распределителя 13 тактовых импульсов поступает на вход блока 16 изменения режима работы, с выхода 30 которого на вход блока 2 памяти поступает третий импульс Пуск, По этому сигналу происходит процесс автокомпенсации входного сигнала Uj, . В дальнейшем устройство работает так же, как и при поступлении второго сигнала Пуск. Таким образом, в регистре максимума 9 и регистре минимума 10 накапливаются соответственно коды наибольших и наименьших значений входного сигнала, которыеjкак и цифровой код каждого значения входного сигнала, поступают на выход 17 всего устрой.ства. Режим Поиск глобальных экстремумов отличается от описанного режима условиями, при которых происходит занесение информации в регистры максимума 9 и минимума 10. С первого выхода блока 16 изменения режимоб работы на вход второго дешифратора 11,2 поступает потенциал, в соответствии с которым сигналы на выходах 24 или 25 появляются только после 9 , появления кодов локального максимума. 01 или локального минимума 10 на выходе регистра 3 сдвига. Коды КХ f,,jj или с выхода блока 2 памяти первый раз заносятся соответственно в регистры максимума 9 и минимума 10. В последующем на блоке 1 сравнения аналоговых сигналов сравниваются величины Ицр и , соответствующие локальному и глобальному максимумам или локально и глобальному минимумам. Изобретение позволяет определить наибольшие и наименьшие значения сигнала, а также глобальные значения экстремумов на заданном промежутке времени.

Х

лття

21

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЭКСТРЕМАЛЬНЫХ ЗНАЧЕНИЙ СИГНАЛА1 .',c.f'- п г^'-?Г!-5^гО ! ч-иП;л й,>&Ь.Н..!1 | 1972 |

|

SU424162A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Цифровой указатель экстремумов сигнала | 1975 |

|

SU557718A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1989-06-15—Публикация

1979-09-17—Подача