Изобретение относится к автоматике и контрольно-измерительной технике и может быть использовано в Систе мах автоматического контроля динамических объектов, в частности в систе мах контроля судовых систем управления и регулирования. Известно устройство для контроля динамических систем управления, в ко тором осуществляется измерение выход ного сигнала системы управления и сравнение его с эталоном, что позволяет оценить работоспособность системы в целом 1 ). Наиболее близким к предлагаемому является устройство для контроля динамической системы управления, содер жащее генератор экспоненциальныхфункций, входной, выходной и (п-1) промежуточных формирующих модулей, каждый из которых состоит из блека произведения и интегратора, п блоков сравнения, п элементов ,НЕ, п элементов и, и индикатор с соответствующими связями 2, Однако эти устройства не позволяют определить значения коэффициентов передачи и постоянных времени динамических блоков системы управления и тем самым оценить работоспособность блоков. Целью изобретения является повышение достоверности результатов контроля системы управления. Указанная цель достигается тем, что в устройство содержащее регистратор, блок генераторов экспоненциальных функций и по числу контрольных точек системы управления - функ(иональные преобразователи, состоящие из последовательно соединенных первого узла умножения и первого интегратора и последовательно соединенных второго узла умножения и второго интегратора, первые входы первого и второго узлов умножения каждо397го функционального преобразователя соединены с соответствующей контрольной точкой системы управления, а вторые входы - с первым и вторым выходами соответстаенно блока генераторов экспоненциальных функциу, запускающий вход которого подключен к запускащему входу устройства, дополнительно введены вычиспительные. , ЧИСЛО которых.на единицу меньшс иисла контрольных точек системы управления, каждый вычислительный блок содержит первый узел деления , последовательно соединенные второй узел деления, третий узел умножения и первый сумматор и последовательно соединенные третий узел деления, четвертый узел умножения и второй сумматор, выходы первого и второго сумматоров каждого вычислительного блока подключен к соответствующим входам регистратора, первые входы второго и третьего узлов деления каждого вычислительного блока соединены соответственно с первым и вторым задающими входами устройства, второй и третий входы второго узла деления каждого i-го вычислительного блока подключены к выходам первых интеграторов i-ro и (t+1)-ro функциональных преобразователей соответственно, второй вход третьего узла деления i-ro вычислительного . блока соединен с первым входом первого узла деления данного вычислительного блока и с выходом второго интегратора i-ro функционального преобразователя, а третий вход третьего узла Д1еления I-го вычислительного блока подключен ко второму входу первого узла деления данного вычр, ели тельного блока и к выходу второго интегратора (1+1)-го функционального преобразователя, причем в каждом вычислительном блоке второй вход первого сумматора соединен с первым задающим входом устройства, выход первого сумматора - со вторым входом четвертого узла умножения, а второй Езход второго сумматора - с выходом первого узла деления данного вычислительного блока

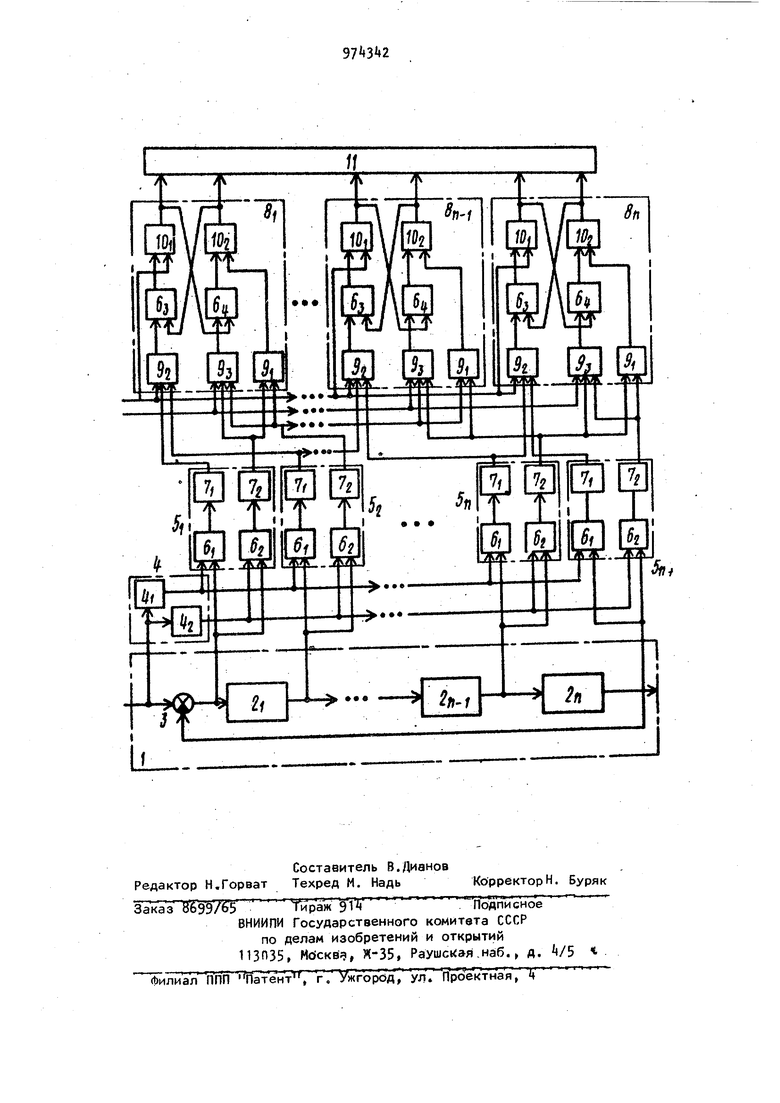

На чертеже представлена схема устройства для снятия динамических характеристик системы управления.

Устройство содержит объект контроля 1, состоящий из блоков 2,,,.2 динамической систему управления и элемента сравнения 3 блока f генераПри наличии на входе устройства запускающего сигнала генераторы i и блока 4 формируют выходные сигналы в виде экспоненциальных функций , которые подаются на первые входы первого и второго узлов умножения 6 и 6 функциональных преобразователей 5;, ,оо, ,5(п.,).На вторые входы узлов 6 и 6i2 поступают си1-

нал рассогласования системы Xjjt) и выходные сигналы X(t), ...,Xn(t) блоков 2,500,2п. Выходные сигналы узлов умножения 6-1 и 62 подаются на соответствующие входы интеграторов

7 и 7(j функциональных преобразователей 5 ,ooi 5(п+).В результате интегрирования формируются сигналы XoCS;),... ,Xy,(Sj) I полученные путем преобразования по Лапласу контролируемых временных сигналов Xo(t),..,, Xn(t). При этом аргументу преобразования Лапласа Sj за аются два фиксированных вещественных значения S : и Sij .

которые равны , ,8

где

П

tp - Время переходного процесса исправной системы.

Выходные сигналы первых интеграторов 7 функциональных преобразователей 5 ,000,5(п+-,)подаются на второй вход вторых узлов деления 87 каждого соответствующего и третий вход этих же узлов деления предыдущего вычислительных блоков В,,.„,8о. Выходные сигналы вторых интеграторов 7 функциональных преобразователей 5 ..5(п+)поступают на второй вход третьего 9 и первый вход первого узла деления 9 каждого соответствующего, а также на третий и второй входы узлов деления из вычислительных блоков В,.„,,8о, Выходные сигналы второго и третьего узлов деления каждого вычислительного блока 8, о о.,8 п. подаются на третий и четвертый узлы умножения и 6п этих вычислительных блоков Выходные сигналы третьего узла умножения вычислительных блоков 8/),o«,,8t в сумторов экспоненциальных функций, функциональные преобразователи 5ni ° 5(4) состоящие из узлов умножения 6;, и. интеграторов 7 и 7,2 вычисли- тельные блоки 8,в-,о,8п, состоящие из узлов деления 9, 92 и Э-г, уэлов умножения 6 и 64 и сумматоров 10 и Юд и регистратор 11. Устройство работает следующим образом,

маторе 1П этих вычислительных блоков суммируются с первым задающим сигналом устройства, а выходнне сигналы четвертого узла умножения 6 суммируются в сумматоре Юд с выходным сигналом первого узла деления 9 вычислительных блоков 8,.,,,8„,

Выходные сигналы сумматоров 10 и lOj, пропорциональные промежуточным значениям коэффициентов передачи и постоянных времени блоков системы управления .,,.. ,2,:,, подаются на вторые входы третьего 6 и четвер того 6 узлов умножения каждого вычислительного блока Это вызывает повторную обработку узлов умножения 6 и 6 сумматоров 10-j и Ю,, Такой процесс повторяется до тех пор, пока на выходах сумматоров 1П и lOj не будут установившиеся сигналы, пропорциональные текущим значе ниям коэффициентов передачи и постбянных времени блоков 2,„„„,2„ системы управления, которые фиксируются регистратором 11.

Таким образом, устройство повышает достоверность снятия динамических характеристик (коэффициентов передачи и постоянных времени) блоков замкнутой системы управления за счет введения вычислительных блоков, содержащих узлы деления и умножения и сумматоры с соответствующими связями. Данная информация позволяет также оценить текущее техническое состояние блоков динамической системы управления,

Формула изобретения

Устройство для снятия динамических характеристик системы управле- ния, содержащее регистратор, блок генераторов экспоненциальных функций и по числу контрольных точек системы управления - функциональные преобразователи, состоящие из последовательно соединенных первого узла умножения и первого интегратора и последовательно соединенных второго узла умножения и второго интегратора, первые входы первого и второго узлов умножения и второго интегратора, первые входы первого и второго узлов умножения каждого функционального преобразователя соединены с соответствующей контрольной точкой системы управления, а вторые входы - с

первым и вторым выходами соответст венно бгЬка генераторов экспоненциальных функций, запускающий вход которого подключен к запускающему входу

5 устройства, отличающееся тем, что, с целью повышения достоверности результатов контроля, устройство содержит вычислительные блоки, число которых на единицу меньше

0 числа контрольных точек системы уп.равления, каждый вычислительный блок содержит первый узел деления, последовательно соединенные второй узел деления, третий узел умножения и

5 первый сумматор и последовательно соединенные третий узел деления, четвертый узел умножения и второй сумматор, выходы первого и второго сумматоров каждого вычислительного блока

0 подключены к соответствующим входам регистратора, первые входы второго и третьего узлов.деления каждого вычислительного блока соединены соответственно с первым и вторым задающими входами устройства, второй и третий входы второго узла деления каждого i-ro вычислительного блока подключены к выходам первых интеграторов i-ro и (i+l)-ro функциональных преобразователей соответственно, второй вход третьего узла деления i-ro вычислительного блока соединЪн с первым входом первого узла деления данного вычислительного блока

- и с выходом второго интегратора i-ro функционального преобразователя, а третий вход третьего узла деления i-ro вычислительного блока прдключен к второму входу первого узла деQ ления данного вычислительного блока и к выходу второго интегратора (i+ +1)-го функционального преобразователя, причем в каждом вычислительном блоке второй вход первого сум. матора соединен с первым задающим входом устройства, выход первого сумматора - с вторым входом четвертого узла умножения, выход второго сумматора - с вторым входом третьего узла умножения, а второй вход второго сумматора - с выходом первого узла деделения данного вычислительного блока.

Источники информации, принятые во внимание при экспертизе

5 1, Авторское свидетельство СССР № , кл. G 05 В 23/02, 197U

2. Авторское свидетельство СССР № 789975, кл. G 05 В 23/02, 1980.

Itl

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения оптимального периода контроля и технического обслуживания системы | 1991 |

|

SU1837338A1 |

| Интегрирующее устройство | 1978 |

|

SU781849A1 |

| Устройство для проведения многофакторного эксперимента | 1989 |

|

SU1691820A1 |

| Множительно-делительное устройство | 1980 |

|

SU920712A1 |

| Устройство для определения оптимального периода технического обслуживания системы | 1981 |

|

SU976461A1 |

| Устройство для контроля динамической системы управления | 1979 |

|

SU789975A1 |

| Частотно-управляемый электропривод | 1989 |

|

SU1720138A1 |

| Устройство для решения интегральных уравнений | 1988 |

|

SU1608705A1 |

| Устройство для определения оптимального периода технического обслуживания изделия | 1990 |

|

SU1737466A1 |

| Адаптивный статический анализатор | 1985 |

|

SU1305730A1 |

Авторы

Даты

1982-11-15—Публикация

1980-05-20—Подача