(54) ИНТЕГРИРУКЯДЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегратор | 1979 |

|

SU805362A1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 1973 |

|

SU409248A1 |

| Решающий блок цифровой интегрирующей структуры | 1983 |

|

SU1104514A1 |

| Интегроарифметическое устройство | 1990 |

|

SU1784975A1 |

| Интегро-арифметическое устройство | 1979 |

|

SU783813A1 |

| ИНТЕГРАТОР ДЛЯ ПАРАЛЛЕЛЬНОЙ ЦИФРОВОЙ ИНТЕГРИРУЮЩЕЙ МАШИНЫ С ЭЛЕКТРОННОЙ КОММУТАЦИЕЙ | 1973 |

|

SU388278A1 |

| Цифровой интегратор | 1974 |

|

SU519735A1 |

| Цифровой интегратор для решения краевых задач | 1976 |

|

SU568060A1 |

| Цифровой интегратор для решения краевых задач | 1988 |

|

SU1501054A1 |

| Устройство для моделирования нейрона | 1977 |

|

SU682910A1 |

1

Изобретение относится к вычислительной :технике и может быть использовано при разработке цифровых интегрирующих машин и структур.

Известны цифровые интеграторы, со- 5 стоящие из сумматоров, регистров, блоков умножения и выходных блоков. Такие устройства облсщают высоким быстродействием tlJ .д

Однако при интегрировании с их по- Ю мощью уравнений Шеннона возникают трудности в расчете начальных значений переменных и в организации вычислений на начальном участке интегрирования.15

Кроме того, в устройствах ошибка вычисления в одном или нескольких шагах интегрирования может существенно повлиять на жонечлёЕ„Рбзультат.

Наиболее близким к предлагаемому 20 по технической сущности является цифровой интегратор, содержащий сумматор, регистр подынтегральной функции,схему умножения, узел формирования и хранениявыходных величин 2. 25

Однако при использовании таких устройств необходимо предварительно рассчитывать начальные значения всех . pe 4eнныx, входящих в исходную систему уравнений Шеннона,что существенно за-30

трудняет их применение для решения задач управления в темпе процесса. Ошибка в одном из шагов ийтёгрйрбйанйя

в таком интеграторе может привести к существенному искажению результата вычисления.

Цель изобретения - повышение надежности устройства.

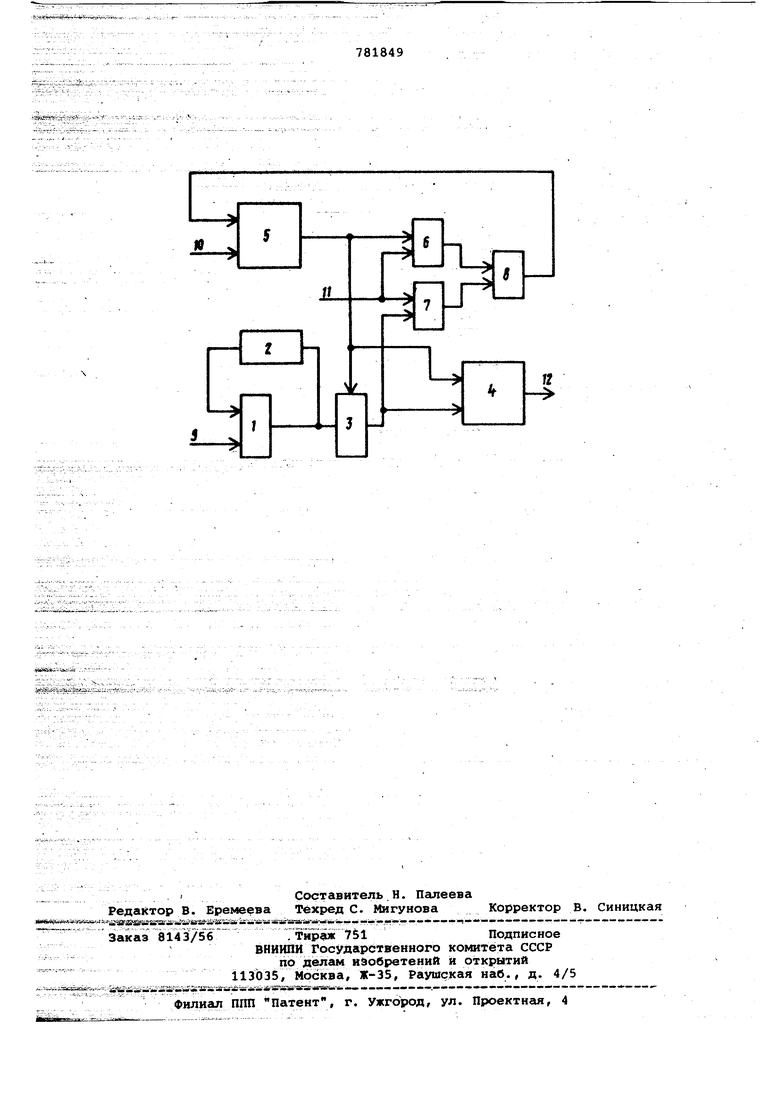

Поставленная цель достигается тем, что в устройство, содержащее сумматор, йыход которого соединен через регистр подынтегральной функции с первьлч входом сумматора и неп6средст венно с первьа входом узла умножения, выход которого подключен к первому входу узла хранения выходных величин, введены узел преобразования переменной интегрирования, элементы И, ИЛИ, причем выход узла преобразования переменной интегрирования подключен к первому входу первого элемента И и вторым входгил узла хранения выходных величин и узла умножения, выход которого соединен с первым входом второго элемента И, управляющий вход устройства соединен со вторыми входами- элементов И, выходы которых соединены соответственно с первым и вторым входа йй элемента ИЛИ, вьссод элемент а ИЛИ подключен к первому входу узла преобразования перменной интегрирования, второй вход каждого подключен к информационному входу устройства, выход узла хранения выходных величин является информационным выходом устройства. На чертеже приведена блок-схема устройства. Устройство содержит сумматор 1, регистр 2 подынтегральной функции, узел 3 умножения, узел 4 хранения выходных величин, узел 5 преобразования переменной интегрирования, элементы И б, 7, элемент ИЛИ 8, вход 9 (шина приращения подынтегральной функции), вход 10 (шина переменной интегрирования) , вход 11(шина управляющих импуль сов) и выход 12 устройства. С помощью узла 5 преобразования переменной интегрирования осуществляется ее представление в каждом шаге решения потоком многоразрядных приращений VJ. , каждое из которых в прямом коде имеет не более одной единицы в значащих разрядах по формуле .,ч- 1 1 -л .V ,.c,;gv, Q-.ecNwPro Q. Y V Пг - r4vi - Здесь Ya. - значение переменной интегрирования в i-ном шаге решения, п - показатель, определяющий вес ста шёго разряда максимального значения приращения V1 ; Р - оператор, учитывающий первое изменение знака рассогласования Q j . . При таком представлении переме,нно интегрирования умножение подынтеграл ной функции на величину приращения переменной интегрирования эквивалент нб сдеигУ значения подынтегральной функади HeKOtopoeчисло разрядов ёправо. Для обеспечения максимального быстродействия необходимо в качестве Vli выбирать максимально допустимое значение шага интегрирования при заданной точности вычислений Выход узла 5 преобразования переменной интегрирования соединен со входами узла 3, элемента и б и узла причем приращения V% поступают на входы элемента И б или узла 4 в зави симости от метода реализации исходно системы в явном или неявном виде. Су матор 1 и регистр 2 предназначены дл образования текущего значения подынтегральной функции, величина которой поступает затем на вход узла 3. Если исходная система уравнений реешизуёт 1;я в явном виде, то результат умноже ния значения пoдынteгpaльнoй функции на величину приращения V поступает на вход узла 4, если система уравненШ рёализубтся в неявном виде, то результат умножения через элементы И 7 и ИЛИ 8 поступает на вход обратной связи узла 5. Устройство работает следующим образом. Каждый шаг решения разбивается на (1+t) шагов интегрирования, где tT определяется величиной J и числом разрядов m для представления приращений по формуле , В первом (начальном) шаге интегрирования каждого i-го шага решения на вход узла 5 по шине 10 поступает значение переменной интегрирования (аргумента) данного шага решения, в регистр 2 через сумматор 1 по шине 9 в зависимости от реализуемой операции записывается значение подынтегральной функции для аргумента равного нулю, или значение подынтегральной функций Для данного шага решения (например, при вычислении функций Y х, в регистр 2 записывается нуль, при вычислении функции Y Cos X - единица, при выполнении операций умножения и деления записывается значение подынтегральной функции данного шага решения). В зависимости от реализации в данном интеграторе исходной систе№1 дифференциальных уравнений в явном или в неявном виде сигналом из устройства управления по шине 11 подготавливается к работе соответственно элемент И б или 7, разрешается поступление на вход узла 4 соответственно значения с выхода узла 5 или значения произведения с выхода узла 3. Со второго шага интегрирования начинается преобразование переменной интегрирования данного шага решения в поток многоразрядных приращений в соответствии с формулой (1). На вход 9 поступает приращение подынтегральной функции Iv а на вход узла 3 приращения ) Jii. . Величина подынтегральной функции гл поступает на узел 3, где умножается на значащий рязряд приращения 15{д . Если исходное дифференциальное Уравнение реализуется в явном виде, то приращение через обратную связь, включающую элементьа И б и ИЛИ 8, псйтупает на вход узла 5, а результат умножения поступает в узел 4 и далее по шине 12 на выход устройства. Если исходное уравнение реализуется в неяв.номвиде, то на вход узла 5 через обратную связь, включающую элементы И 7 и ИЛИ 8, поступает результат умноясенйя, а на вход узла 4 и на выход 12 - приращение . Выходная величина данного шага решения формируется как. алгебраическая сумма приходящих на вход узла 4 значений и выдается через выход 12 устройства в первом (начальном) шаге интегрирования следующего (i+1)-ro шага решения Рассмотрим реализацию операции ум ножения Z и функциональной заkвисимости Z . X В первом случае исходное дифферён диальное уравнение в разностной форм имеет вид zcj х.)5.з в первом (начальном) шаге интегри рования i-ro шага решения в регистр заносится значение Х , в узел 5 пост пает значение Yj . Сигналом из устрой ства управления подготавливается к р боте элемент И 6, на вход узла 4 раз решается поступление результата умножения. в каждом последующем шаге интегрирования данного i-го шага решения реализуется формула (1) и внчисляются значения Z.-5L VZ-Через (1+fc) шагов интегрирования с выхода узла 4 выдается искомбе значение произведения Z . При вычислений функциональной за1висимости Z - исходное дифференциальное уравнение записывается в форме x.. kj и реализуется в неявном виде. В первом (начальном) шаге интег рирования i-ro шага решения в регистр 2 заносится значение Х, в узел 5 поступае значение К. Сигналом из устройства управления подготавливается к работе элемент И 7, на вход узла 4 разрешается поступление приращеиия JJ. В каждом последующем шаге интегрирования данного i-ro шага реализуется формула (О и вычисляются значения 4Zi3 4i1iij и xi 1. Через (l+C)-шагов интегрирования с выхода узла 4 выдается искомое значение фун ции Zj как сумма значений. Использование данного устройства позволяет интегрировать дифференциальные уравнения без -предварительног расчета начальных значений входящих в него переменных и без отработки на чального участка,-что расширяет область применения интеграторов для ре шения задач управления в темпе процесса. Применение интегратора потоков многозарядных приращений увеличивает также вероятность получения правильн го результата вычислений при решении непрерывных задач. Если известные цифровые интеграторы реализуют раз-, лостную схему интегрирования систёШ уравнений Шеннона на отрезке от до X Х(,2) и ошибка в одном из шагов решения может привести к существенному искажению конечного результата, то предлагаемый интегратор потоков многоразрядных прИращений осуществляет в каждом шаге интегрирования исходной системы на отрезке изменения аргумента от X О до X XJ; . При такой организации вычислений результат каждого шага решения не зависит от предыдущих вычислений, что значительно повышает надежность работы интегратора потоков многоразрядных приращений. Формула изобретения Интегрирующее устройство, содержащее сумматор, выход которого сое- . динен через регистр подынтегральной функции с первым входом сумматора и непосредственно с первым входом узла умножения, выход которого подключен к первому входу узла хранения выходных величин, отличающееся тем, что, с целью повышения надежности, в устройство введены узел преобразования переменной интегрирования, элементы И, ИЛИ, причем выход узла преобразования переменной интегрирования подключен к первому входу первого элемента И и вторым входом узла хранения выходных величин и узла умножения, выход которого соединен с первым вхо- , дом второго элемента И, управляющий вход устройства соединен со вторыми входами элементо.в И, выходы которых соединены соответственно с первЕОМ и втсэрым входами элемента ИЛИ, выход элемента ИЛИ подключен к первому входу узла преобразований переменной интегрирования, второй вход каждого псЗдКлючен к информационному входу устройства, выход узла хранения выходных величин является информационным выходом устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 409248, кл. G Об J 1/02, 1974. 2.Авторское свидетельство СССР 418864, кл. G 06 J 1/02, 1974 (прототип) .

u i-i- : :. .

i siKi i -i sfcii; -L.i;L

Авторы

Даты

1980-11-23—Публикация

1978-12-13—Подача