(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПОРАЗРЯДНОГО УРАВНОВЕШИВАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1987 |

|

SU1462479A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1388989A2 |

| Двухканальный аналого-цифровой преобразователь | 1981 |

|

SU995314A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1270895A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1547062A1 |

| Цифроаналоговая следящая система | 1989 |

|

SU1700536A1 |

| Аналого-цифровой преобразователь с промежуточным преобразованием в частоту | 1987 |

|

SU1441479A1 |

| Устройство для измерения уровней сигнала изображения | 1987 |

|

SU1520672A1 |

| Устройство для отображения кривых на экране электронно-лучевой трубки | 1988 |

|

SU1547022A1 |

| Аналого-цифровой преобразователь с самокоррекцией | 1986 |

|

SU1341716A1 |

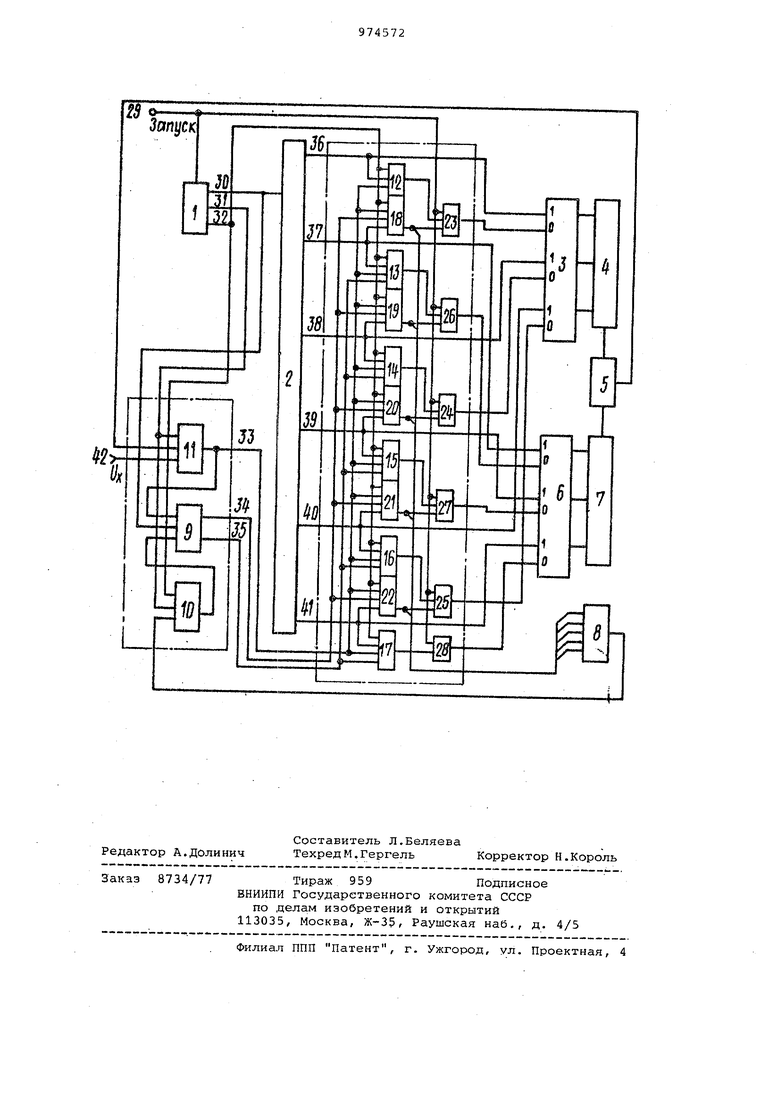

Изобретение относится к аналогоцифровой измерительной технике и может быть использовано в контрольноизмерительных системах различного назначения, работающих в условиях действия импульсных помех. Известен аналого-цифровой преобразотель, построенный по схеме поразрядного уравновешивания, содержащ генератор импульсов, преобразовател кода в напряжение, регистр кода, логический блок и блок сравнения, первый вход которого соединен с источником преобразуемого напряжения, а второй - с выходом преобразователя кода в напряжение, входы которог подключены через регистр кода к вых дам логического блока, первый управ ляющий вход этого блока соединен с первым выходом блока сравнения, а другие - с выходны11и шинами распределителя импульсов 1 . Недостатками его является низкая помехоустойчивость, обусловленная д ствием как внешних импульсных помех так и сбоями дискретных элементов. наличие динамических погрешностей, вызванных изменением сигнала за вре мя преобразования ( низкая корректирующая способность преобразователя) Известен аналого-цифровой преобразователь, построенный по схеме поразрядного уравновешивания, содержащий генератор импульсов, распределитель импульсов, преобразователь кода в напряжение, регистр кода, логический блок и блок сравнения, и связи между нимиt2J. Недостатками устройства является низкая помехоустойчивость в условиях действия внешних импульсных помех и сбоях в элементах его цифровой части, низкая корректирующая способность динамических погрешностей, так как период измерения состоит из двух циклов, а коррекция производится только на последнем. Поэтому глубина коррекции не может быть больше величины последнего разряда первого цикла уравновешивания. При этом значение этого разряда может только увеличиватьсй. Цель изобретения - повышение помехоустойчивости и точности преобразования. Поставленная цель достигается тем, что в аналого-цифровой преобразователь поразрядного уравновешивания, содержащий генератор импульсов, вход которого соединен с шиной Запуск, первый выход соединен со входом распределителя импульсов, нечетные выходы которого подключены к соответствующим входам установки в единицу основного регистра кода, выходы которого соединены со входами ос новного преобразователя кода в напряжение, ,а выходы дополнительного гистра кода - со входами дополнител ного преобразователя кода в напряже ние, первый выход элемента сравнени соединен с шиной входного сигнала, введены элементы И текущего такта и последующего такта, элементы ИЛИ ос новного регистра кода, элементы ИЛ дополнительного регистра кода, элемент ИЛИ, элемент памяти гашения разряда предыдущего такта и сумматор, первый и второй входы которого соответственно соединены с выходами основного и дополнительного преобра зователей кода в напряжение, а выхо соединен со вторым входом элемента сравнения, третий вход которого под ключен к выходной шине стробирующих импульсов генератора импульсов и пе вому входу элемента памяти гашения разряда предыдущего такта, второй вход которого соединен с выходной шиной импульсов разрешения гашения генератора импульсов и с первыми вxoдa ш элементов И текущего и последующего тактов, вторые входы которых соединены с выходом элемента сравнения и с первым входом элемента памяти состояния разряда предыдущего такта, второй вход которог соединен с выходной шиной тактовых импульсов генератора импульсов, тре тий вход - с выходом элемента памяти гашения разряда предыдущего такта, прямой выход которого подключен к третьим входам элемент ов И предыдущего такта, а инверсный - к третьим входам элементов И текущего такта, кроме первого, при этом выходы распределителя импульсов подкл чены соответственно к четвертым входам элементов И текущего такта и, кроме первого, к четвертым входам элементов И предыдущего такта, а четные выходы распределителя импульсов соответственно подключены к входам установки в единицу разрядов дополнительного регистра кода, входы установки в нуль разрядов основного и дополнительного регистров кодов соединены соответственно с выходами элементов ИЛИ основного и дополнительного регистров кода, первые входы которых соединены с шиной Запуск, вторые соответствен но соединены с выходами элементов И текущего такта, а третьи, кроме последнего элемента ИЛИ дополнител ного регистра кода, соответственно соединены с выходами элементов И последующего такта и с входами элемента ИЛИ, выход которого соединен с третьим входом элемента памяти гашения разряда предыдущего такта. На чертеже изображена функциональная схема аналого-цифрового преобразователя , Схема содержит генератор 1 импульсов, распределитель 2 импульсов, основные регистр 3 кода и преобразователь 4 кода в напряжение, сумматор 5, дополнительные регистр 6 и преобразователь 7 кода в напряжение, элемент 8 ИЛИ, элемент 9 памяти состояния разряда предыдущего такта, элемент ГО памяти гашения разряда предыдущего такта, элемент 11 сравнения, элементы И 12 17 текущего такта, элементы И 18-22 предыдущего такта, элементы ИЛИ 23.25 основного регистра кода, элементы ИЛИ 26-28 дополнительного регистра кода, шину 29 Запуск, шину 30 тактовых импульсов, шину 31 стробирующих импульсов, шину 32 импульсов разрешения гашения, шину 33 выхода элемента сравнения, шину 34 прямого и шину 35 инверсного выходов элемента памяти 9, выходные шины 36-41 распределителя 2 импульсов и шину 42 входного сигнала. На шине 33 с приводом импульса по шине 31 вырабатывается сигнал 1 если и U)(, и сигнал О, если Uj(7 и, где и, - измеряемое Напряжение, и ), - напряжение компенсации на выходе сумматора 7. На шине 35 с приходомимпульса по шине 30 вырабатываются сигналы О либо 1, причем 1 в том случае, когда на выходах элементов 10 и 11 имеются сигналы 1, а сигнал О - в остальных случаях. На шине 34 вырабатывается сигнал, противоположный сигналу на шине 35. На выходе элемента 10 с приходом импульса по шине 31 вырабатывается сигнал 1, а с приходом импульса по шине 32 - О, если на выходе элемента ИЛИ 8 сигнал 1, и 1 в противном случае. Генератор 1 поочередно вырабатывает импульсы соответственно на шинах 30-32. Устройство работает следующим образом. Импульсы Запуск по шине 29 устройства устанавливаются в начальное состояние, при этом все разряды основного 3 и дополнительного б регистров кодов через элементы ИЛИ 23-28 устанавливаются в нулевое состояние, рашрешается прохождение импульсов по шинам 30-32 с генератора 1 . Работу преобразователя рассмотрим при воздействии импульсных помех как отрицательной, так и положительной полярности, а также при изме.нении измеряемого напряжения за время преобразования как в сторону уменьшения, так и увеличения.

1-й такт. Импульс по шине 30 через распределитель 2 включает старший разряд основного регистра 3, пр этом на выходе сумматора 5 сформируется компенсационное напряжение U 4h. Поскольку и и )2h то с приходом импульса по шине 31 снал 1 установится на шине 33, одновременно на выходе элемента 10 также сигнал 1. Импульс по шине 32 выключает старший разряд основного регистра 3 через элементы и 18, ИЛИ 25, а элемент 10 состояния не изменяет, так как на выходе элемента ИЛИ 8 импульс отсутствует.

2-й такт. Импульс по шине 30 устанавливает на шинах 34, 35 сигнал соответственно О и 1 и включает старший разряд дополнительного регистра 6. Поскольку , то U( Uy 1 1 h и импульсом по шине 31 на выходе элемента 11 (шина 33) устанавливается сигнал,О, а элемент 10 своего состояния u-s изменяет. Импульс по шине 32 не изменяет состояния разрядов основного и дополнительного регистров кодов 3 и 6, а также - состояние элемента 10.

3-й такт. Импульс по шине 30 устанавливает на шинах 34 и 35 сигнал соответственно 1 и О и включает второй разряд основного регистра 3. Поскольку U 6h, то и с приходом импульсов по шинам 31 и 32 сотояния элементов 11, 10 и разрядов регистров кодов 3 и б не изменятся.

4-й такт. Импульс по шине 30 не изменяет сигналов на шинах 34 и 35, включает второй разряд дополнительного регистра 6. Поскольку , то и 7 U)t и импульсы по шинам 31 и 32 состояния элементов 11, 10 и разрядов основного и дополнительного регистров кодов 3 и 6 не изменяет .

Аналогичным образом происходит процесс поразрядного уравновешивания на 5-м и б-м тактах. В результате в основном регистре кода 3 устнавливается кодовая комбинация 011, а в дополнительном регистре 6 кода - 111. Эта кодовая комбинация соответствует десятичному числу 10.

1-й такт. Импульс по шине 30 вклчает старший разряд основного регистра кода. Поскольку U , th, то U| ) 6h, и с приходом импульса по шине 31 на выходе элемента 11 (шина 33 устанавливается сигнал О, на выходе элемента It) сигнал О. Импульс по шине 32 не изменяет состояния старшего разряда основного регистра 3 и сигнала на выходе элемента 10.

2-й такт. Импульс по шине 30 устанавливает на шинах 34 и 35 сигналы соответственно 1 и О и включает

0 старший разряд регистра 6. Поскольку U 8h, то UK. и с приходом импульса по шине 31 сигнал 1 устанавливается на шине 33, сигнал на выходе элемента 10 не изменяется. Импульс по шине 32 через элементы И 18,

5 ИЛИ 23 выключает старший разряд основного регистра 3, на выходе элемента 10 устанавливает сигнал О, так как на выходе элемента ИЛИ 8 находится сигнал 1.

0

3-й такт. Импульс по шине 30 не изменяет сигналы на шинах 34 и 35 и включает второй разряд основного регистра кода 3. Поскольку U, , то U| U и с приходом импульса по ши5не 31 сигнал на шине 33 не изменяется, на выходе элемента 10 устанавливается сигнал 1. Импульс по шине 32 через элементы И 19, или 26 выключает старший разряд дополнитель0ного регистра 6, на выходе элемента 10 устанавливает сигнал О.

Аналогичным образом происходит процесс поразрядного уравновешивания на 4-м, 5-м и 6-м такте. В ре5зультате в основном и дополнительном регистрах кодов 3 и 6 устанавливаются кодовые комбинации 000 и 001. Эта кодовая комбинация соответствует десятичному числу 1.

1-й такт. Импульс по шине 30 Включает старший разряд основного регистра 3. Поскольку Уц 5h U)(0)

5 8h, то с приходом импульса по шине 31 -на выходе элемента 11 (шина 33} устанавливается сигнал О, а на выходе элемента 10 - 1. Импульс по шине 32 не изменяет состояния

0 старшего разряда основного регистра 3 и сигнала на выходе элемента 10.

2-й такт. Импульс по шине 30 устанавливает на шинах 34 и 35 сигналы соответственно 1 и О и включает

5 старший разряд регистра 6. Поскольку ) 8 1, , то с приходом импульса по шине 31 сигналы на шине 33 и выходе элемента 10 не изменятся. Не изменяются состояния раз0рядов основного и дополнительного регистров кодов 3 и 6 и сигнал на вьуот де элемента 10 с приходом импульса по шине 32.

3-й такт. Импульс по шине 30 на из5меняет сигналов на шинах 34 и 35 и ..

включает второй разряд основного регистра 3. Поскольку и ,io-iT7Ux (2-u.-t) с приходом импульса по шине 31 на выходе элемента 11 (шина 33) устанавливается сигнал 1, сигнал на выходе элемента 10 не изменяется, Импульс по шине 32 через элементы И 19, ИЛИ 26 выключает старший разряд дополнительного регистра кода б на выходе элемента 10 устанавливается сигнал О.

4гй такт. Импульс по шине 30 не и.зменяет сигналов на шинах 34 и 35 и включает второй разряд дополнительного регистра 6. Поскольку UK,-8-ti ; 9-Ьг то с приходом импульса по шине 31 на выходе элемента 11 (шина 33) устанавливается сигнал О, а на выходе элемента 10 - 1. Импульс по шине 32 не изменяет состояния регистров 3 и 6 кодов и сигнала на выходе элемента 10.

5-й такт. Импульс по шине 30 не изменяет сигналов на шинах 34 и 35 и включает младший разряд основного регистра 3. Поскольку Ui -giix и/(4Afc)-9 то с приходом импульса по шине 31 на выходе элемента 11 (шина 33) и на выходе элемента 10 сигналы не изменятся. Импульс по шине 32 не изменяет состояний разрядов регистров 3 и 6 кодов и сигнала на выходе элемента 10.

б-и такт. Импульс по шинез 30 не именяет сигналов на шинах J4 и 35 и включает младший разряд дополнительного регистра 6. Поскольку Ii|(l0h Uy(5u. 2/3h, то с приходом импульса по шине 31 на выходе элемента 11 (шина 33 устанавливается сигнал 1, на выходе элемента 10 сигнал не изменяется. Импульс по шине 32 через элементы И 22, ИЛИ 25 выклн чает младший разряд основного регистра кода 3, на выходе элемента 1U устнавливает сигнал О..,

В результате в основном 3 и дополнительном 6 регистрах кода устанавливаются кодовые комбинации 110 и 011. Эта кодовая комбинация соответствует десятичному числу 9.

1-й такт. Импульс по шине 30 включает старший разряд основного регистра 3, Поскольку 7 U (0) , то с приходом импульса по шине 31 на выходе элемента 11 (шина 33) устанавливается сигнал 1, а на выходе элемента 10 - сигнал 1. Импульс по шине 32 через элементы И 12, ИЛИ 13 выключает старший разряд регистра 3, сигнал на выходе элемента 10 не изменяется.

2-й такт. Импульс по шине 30 устанавливает на шинах 34 и 35 сигналы соответственно О и 1 и включает старший разряд дополнительного регистра 6. Поскольку U| 44ii7 U(&t}-3 ti, то с приходом импульса по шине 31 На выходе элемента 11(шина 33 устанав.ливается сигнал 1, на выходе элемента 10 сигнал не изменяется. Импульс по шине 32 выключает старший разряд дополнительного регистра б, состояние сигнала на выходе элемента 10 не изменяется.

3-й такт. Импульс по шине 30 не изменяет сигналов на шинах 34 и 35 и включает второй разряд основного регистра 3. Поскольку U(2A-t ТО с приходом импульса по шине 31 на выходе элемента 11 (шина 33) устнавливается сигнал О, сигнал на выходе элемента 10 не изменяется. Импульс по шине 32 не изменяет состояний разр-тдов основного и дополнителных регистров 3, 6 кодов и сигнала по выходе 10.

4-й такт. Импульс по шинах 30, 34 и 35 включает второй разряд дополнительного регистра б. Поскольку и, 4h U(3At)3h, то с приходом импульса по шине 31 на выходе элемента 11 (шина 33) устанавливается сигнал 1, на выходе элемента 10 сигнал не изменяется. Импульс пошине 32 через элементы И 20, ИЛИ 24 выключает второй разряд основного регистра 3 и на выходе элемента 10 устанавливает сигнал 1.

5-й такт. Импульс по шине 30 не изменяет f. сшгналов на шинах 34 и 35 и включает младший основного

регистра 3. Поскольку (Jx-3fi 7Ux( с приходом импульса по шине 31 на выходе элемента 11 (шина 33) устанавливается сигнал 1 и на выходе элемента 10 устанавливается сигнал 1. Импульс по шине 32 через элементы И 21, ИЛИ 27 выключает второй разряд дополнительного регистра 6, на выходе элемента 10 устанавливается сигнал О.

б-й такт. Импульс по шине 30 не изменяет сигналов на шинах 34 и 35 и включает младший разряд дополнительного регистра 6. Поскольку UK. 2fi« Ux(Ai) г то с приходом импульса по шине 31 на выходе элемента 11 (шина 33) устанавливается сигнал О, а на выходе элемента 10 - 1.. Импульс по шине 32 не изменяет состояний разрядов основного и дополнительного регистров 3, 6, и сигнала на выходе элемента 10.

В результате в основном и дополнительном регистрах 3 и 6 установятся кодовые комбинации 001 и 001.Эта код;вая комбинация соответствует числу 2

Таким образом, аналого-цифровой преобразователь обладает повышенной

помехоустойчивостью к воздействию как импульсных помех, так и сбоям дискретных элементов j повышенной способностью к коррекции динамических погрешностей, вызванных изменением сигнала за время преобразования как в сторону уменьшения, так и увеличения.

Формула изобретения

Аналого-цифровой преобразователь поразрядного уравновешивания, содержащий генератор импульсов, вход кото(Рого соединен с шиной Запуск, первый выход соединен со входом распределителя импульсов, нечетные выходы которого подключены к соответствующим входам установки в единицу разрядов основного регистра кода, выходы которого соединены со входами основного преобразователя, кода в напряжение, а выходы дополнительного регистра кода - со входами дополнительного преобразователя кода в напряжение, первый вход элемента сравнения соединен с шиной входного сигнала, отличающийся тем, что, с целью повышения помехоустойчивости и точности преобразования, в него введены элементы И текущего такта и последующего такта, элементы ИЛИ .основного регистра кода, элементы ИЛИ дополнительного регистра кода, элемент ИЛИ, элемент памяти гашения разряда предыдущего такта и сумматор, первый и второй входы которого соответственно соединены с выходами основного и дополнительного преобразователей кода в напряжение, а выход соединен со вторым входом элемента сравнения, вретий вход которого подключен к выходной шине стробирующих импульсов генератора импульсов и к первому входу элемента памяти гашения разряда предыдущего такта, второй вход которого соединен с выходной шиной импульсов разрешения гашения генератора импульсов и с первыми входами Элементов И текущего и последующего тактов, вторые входы которых соединены с выходом элемента сравнения и с первым входом элемента памяти состояния разряда предыдущего такта, второй вход которого соединен с выходной шиной тактовых импульсов генератора импульсов, третий вход - с выходом элемента памяти гашения разряда предыдущего такта, прямой выход

0 которого подключен к третьим входам элементов И предьздущего такта, а инверсный - к третьим входам элементов И текущего такта, кроме первого, при этом выходы распределителя им5пульсов подключены соответственно к четвертым входам элементов И текущего такта и ,кроме первого, к четвертым входам элементов И предыдущего такта, а четные выходы распре0делителя импульсов соответственно подключены к входам установки в единицу разрядов дополнительного регистра кода, входы установки в нуль разрядов основного и дополнительного

5 регистров кодов соединены соответственно с выходами элементов ИЛИ основного и дополнительного регистров кода, первые входы которых соединены с шиной Запуск, вторые соот0ветственно соединены с выходами элементов И текущего такта, а третьи, кроме поаледнего элемента ИЛИ дополнительного регистра кода, соотв е тственно соединены с выходами эле5ментов И последующего такта и с входами элемента ИЛИ, выход которого .соединен с третьим входом элемента памяти гашения разряда предыдущего такта .

0

Источники информации, принятые во внимание при экспертизе

5 вычислительных устройств. М., Энергия, 1975, с. 299.

№ 748863, кл. Н 03 К 13/17, 10.05.78.

Авторы

Даты

1982-11-15—Публикация

1981-02-02—Подача