11 ;5

Изобретение относится к электроизмерительной технике и может быть использовано при создании помехоустойчивых аналого-цифровых преобразователей ,

Цель изобретения - расширение области применения за счет повышения достоверности преобразования в условиях помех, увеличения диапазона измерения и расширения функциональных возможностей.

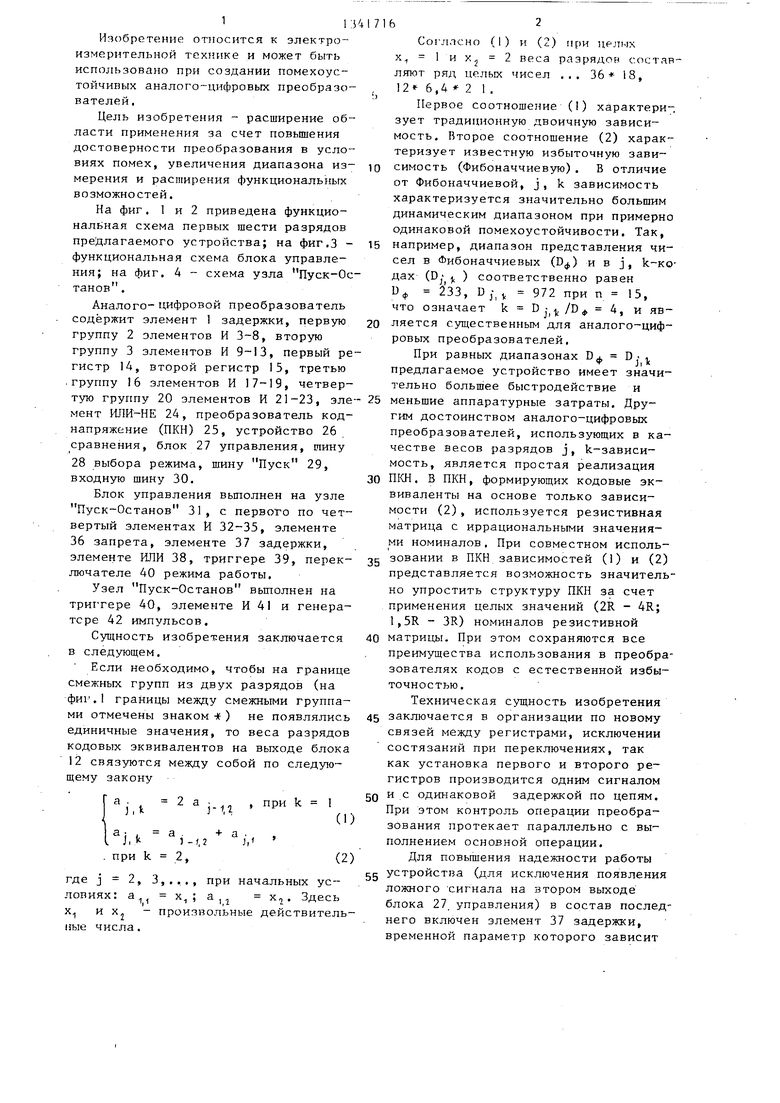

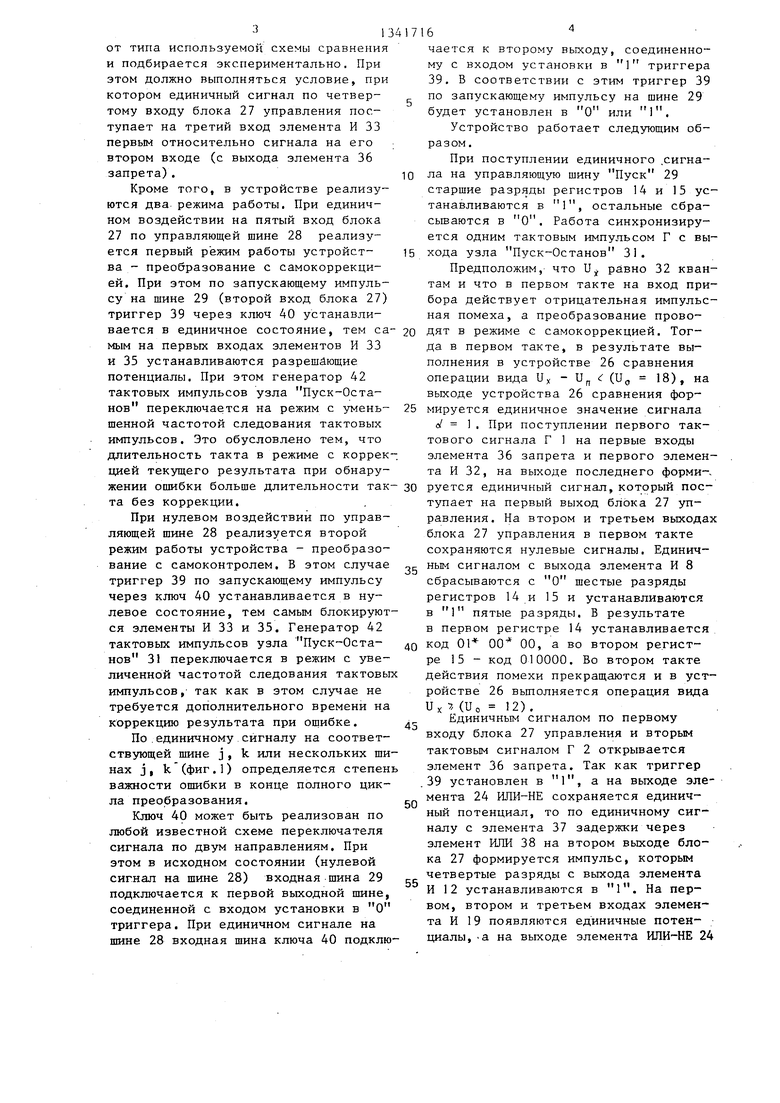

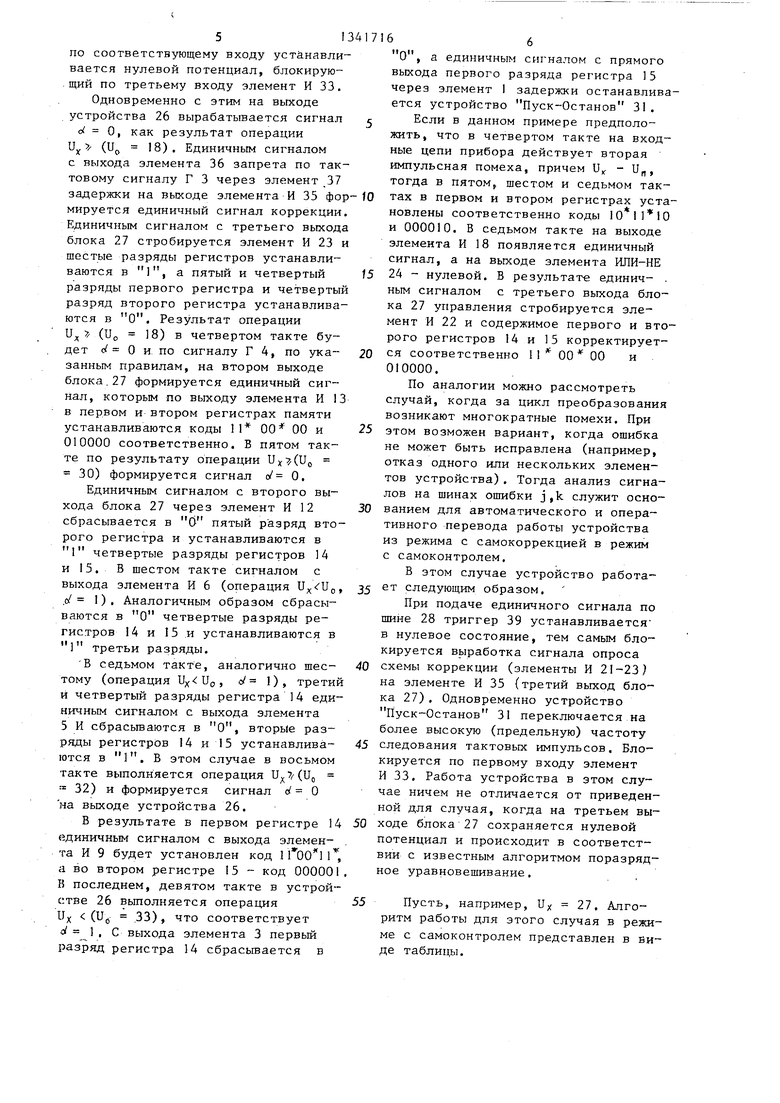

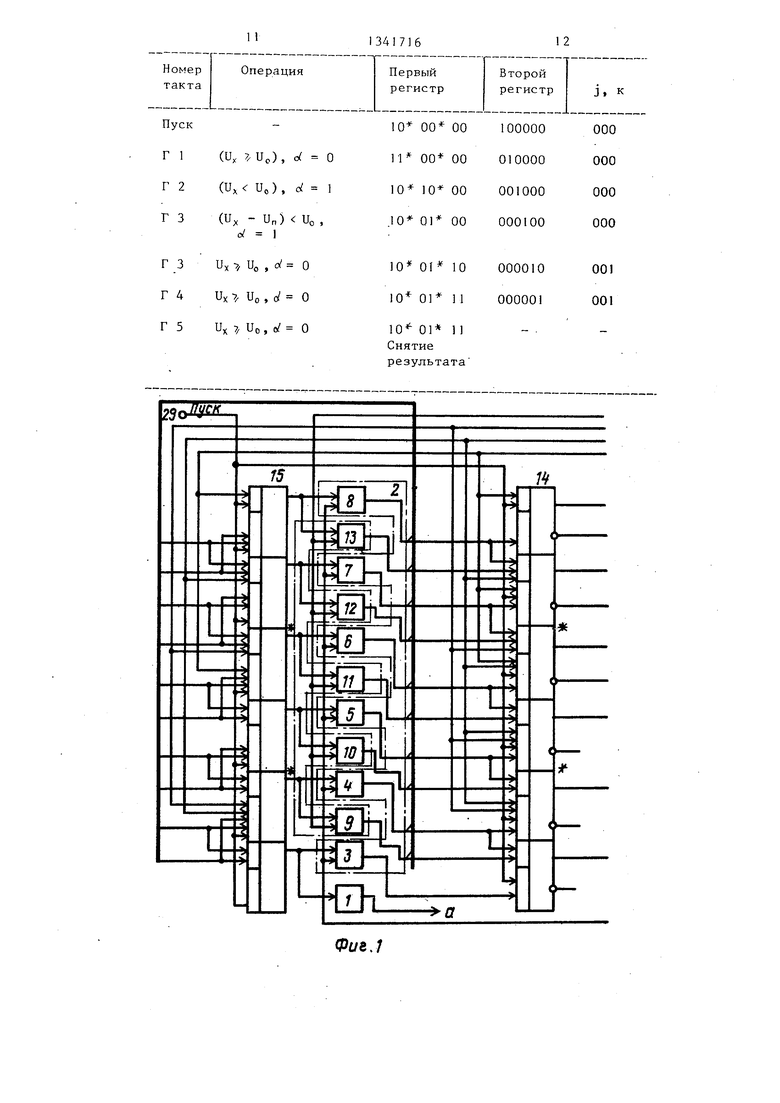

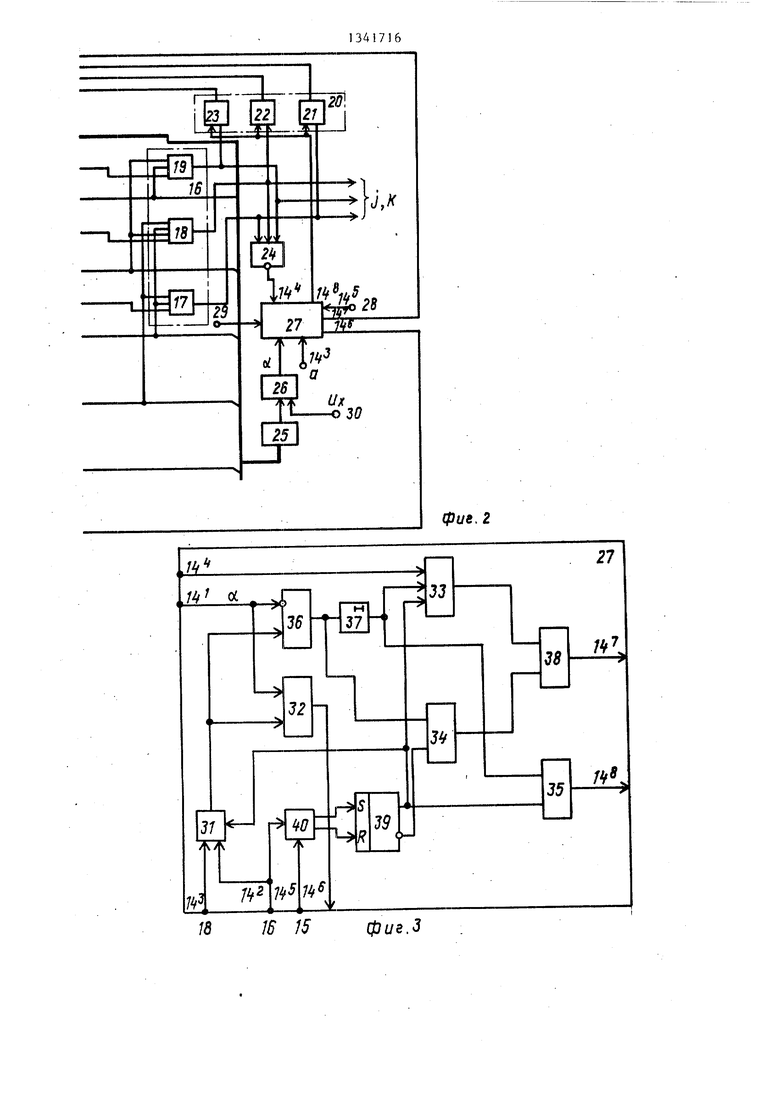

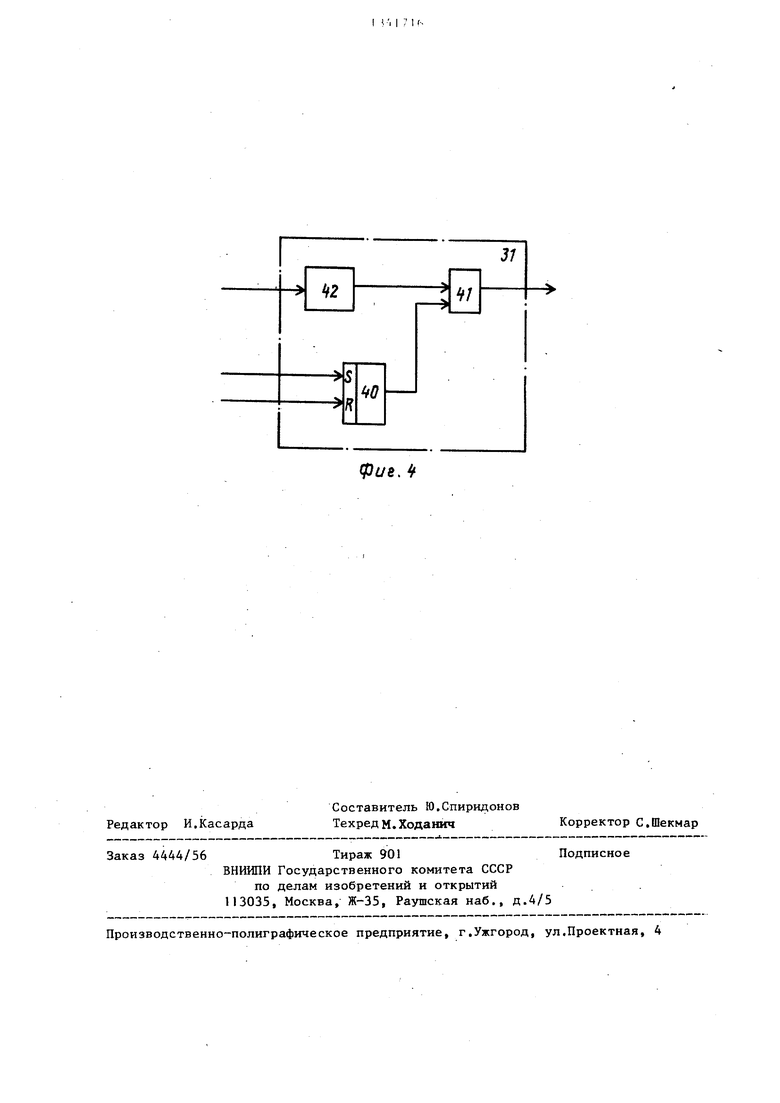

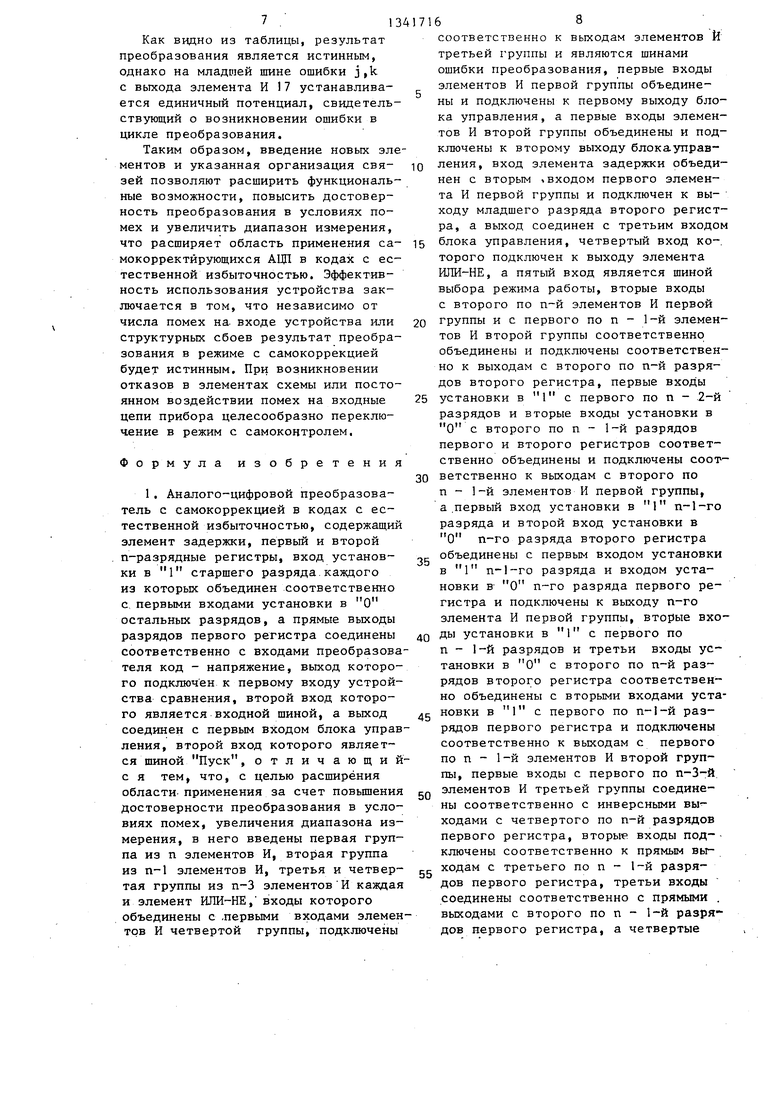

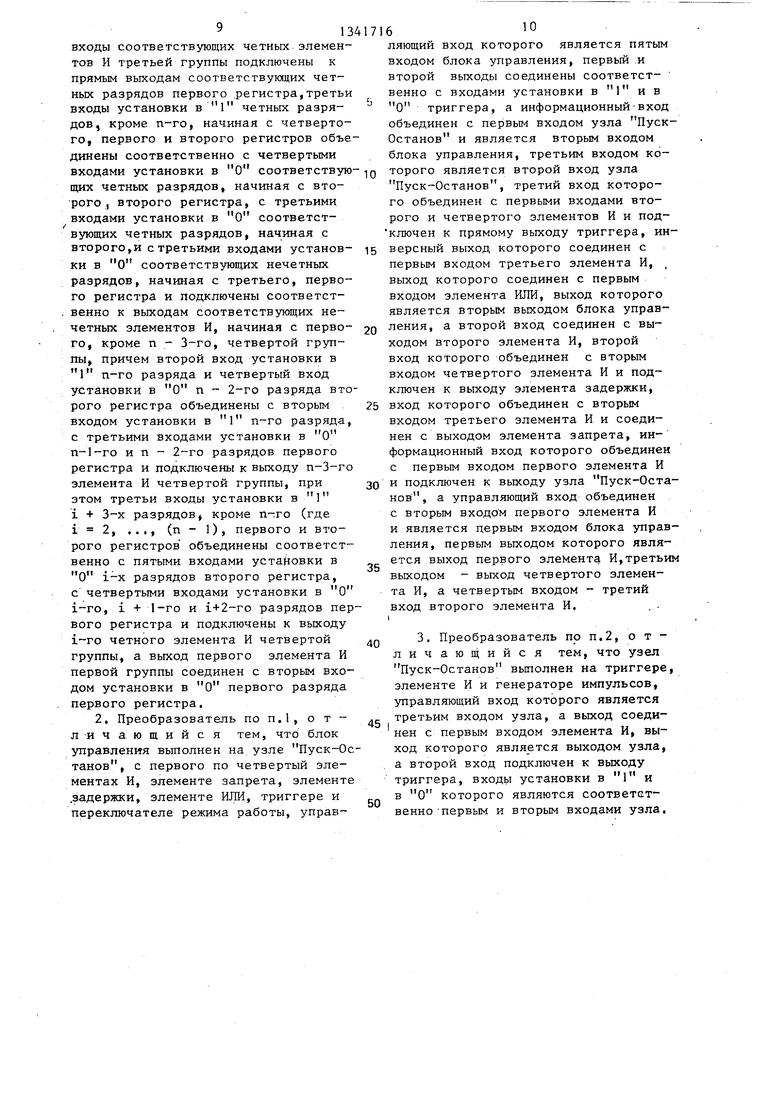

На фиг. 1 и 2 приведена функциональная схема первых шести разрядов предлагаемого устройства; на фиг.З - функциональная схема блока управления; на фиг. А - схема узла Пуск-Ос танов.

Аналого-цифровой преобразователь содержит элемент 1 задержки, первую группу 2 элементов И 3-8, вторую группу 3 элементов И 9-13, первый регистр 14, второй регистр 15, третью .группу 16 элементов И 17-19, четвертую группу 20 элементов И 21-23, элемент ИЛИ-НЕ 24, преобразователь код- напряжение (ПКН) 25, устройство 26 сравнения, блок 27 управления, тину 28 выбора режима, шину Пуск 29, входную шину 30.

Блок управления выполнен на узле Пуск-Останов 31, с первого по четвертый элементах И 32-35, элементе 36 запрета, элементе 37 задержки, элементе ИЛИ 38, триггере 39, переключателе 40 режима работы.

Узел Пуск-Останов вьтолнен на триггере 40, элементе И 41 и генераторе 42 импульсов.

Сущность изобретения заключается в следующем.

Если необходимо, чтобы на границе смежных групп из двух разрядов (на фи1 .1 границы между смежными группами отмечены знаком ) не появлялись единичные значения, то веса разрядов кодовых эквивалентов на выходе блока 12 связуются между собой по следующему закону

2 а : , „ . при k I

Ы

(1

L

при k 2,

J,

(2)

J

ях: а и Xj числа.

1.1

X,

при начальных ус- Здесь

к.

М °- 1,1 Тпроизвольные действитель2

Согласно (I) и (2) при целых X, 1 и Xj 2 веса разрядов составляют ряд целых чисел ... 36 18, 12 6, 1 .

Первое соотношение (I) характери-. зует традиционную двоичную зависимость. Второе соотношение (2) характеризует известную избыточную зависимость (Фибоначчиевую). В отличие от Фибоначчиевой, j, k зависимость характеризуется значительно большим динамическим диапазоном при примерно одинаковой помехоустойчивости. Так,

например, диапазон представления чисел в Фибоначчиевых (Вф) и в j, k-ко- дах (Од)( ) соответственно равен Вф 233, D у, 972 при п 15, что означает k D - /D 4, и является существенным для аналого-цифровых преобразователей.

При равных диапазонах Вф D предлагаемое устройство имеет значительно большее быстродействие и

меньшие аппаратурные затраты. Другим достоинством аналого-цифровых преобразователей, использующих в качестве Весов разрядов j, k-зависи- мость, является простая реализация

ПКН. В ПКН, формирующих кодовые эквиваленты на основе только зависимости (2), используется резистивная матрица с иррациональными значениями номиналов. При совместном использовании в ПКН зависимостей (1) и (2) представляется возможность значительно упростить структуру ПКН за счет применения целых значений (2R - 4R; 1,5R - 3R) номиналов резистивной

матрицы. При этом сохраняются все

преимущества использования в преобразователях кодов с естественной избыточностью.

Техническая сущность изобретения

заключается в организации по новому связей между регистрами, исключении состязаний при переключениях, так как установка первого и второго регистров производится одним сигналом

и с одинаковой задержкой по цепям. При этом контроль операции преобразования протекает параллельно с выполнением основной операции.

Для повьппения надежности работы

устройства (для исключения появления ложного сигнала на втором выходе блока 27. управления) в состав последнего включен элемент 37 задержки, временной параметр которого зависит

от типа используемой схемы сравнения и подбирается экспериментально. При этом должно выполняться условие, при котором единичный сигнал по четвертому входу блока 27 управления поступает на третий вход элемента И 33 первым относительно сигнала на его втором входе (с выхода элемента 36 запрета).

Кроме того, в устройстве реализуются два режима работы. При единичном воздействии на пятый вход блока 27 по управляющей шине 28 реализуется первый режим работы устройст- ва - преобразование с самокоррекцией. При этом по запускающему импульсу на шине 29 (второй вход блока 27) триггер 39 через ключ 40 устанавливается в единичное состояние, тем са мым на первых входах элементов И 33 и 35 устанавливаются разрешающие потенциалы. При этом генератор 42 тактовых импульсов узла Пуск-Останов переключается на режим с умень- шенной частотой следования тактовых импульсов. Это обусловлено тем, что длительность такта в режиме с коррекцией текущего результата при обнаружении ошибки больше длительности так та без коррекции.

При нулевом воздействии по управляющей шине 28 реализуется второй режим работы устройства - преобразование с самоконтролем. В этом случае триггер 39 по запускающему импульсу через ключ 40 устанавливается в нулевое состояние, тем самым блокируются элементы И 33 и 35. Генератор 42 тактовых импульсов узла Пуск-Оста- нов 31 переключается в режим с увеличенной частотой следования тактовы импульсов, так как в этом случае не требуется дополнительного времени на коррекцию результата при ошибке.

По . единичному сигналу на соответствующей шине j, k или нескольких щи нах J, k (фиг.1) определяется степен важности ошибки в конце полного цикла преобразования.

Ключ 40 может быть реализован по любой известной схеме переключателя сигнала по двум направлениям. При этом в исходном состоянии (нулевой сигнал на шине 28) входная шина 29 подключается к первой выходной шине, соединенной с входом установки в О триггера. При единичном сигнале на шине 28 входная щина ключа 40 подклю

s 0 5 О

,.- 0 з

Q

g

чается к второму выходу, соединенному с входом установки в 1 триггера 39. В соответствии с этим триггер 39 по запускающему импульсу на шине 29 будет установлен в О или 1.

Устройство работает следующим образом.

При поступлении единичного .сигнала на управляющую шину Пуск 29 старшие разряды регистров 14 и 15 устанавливаются в 1, остальные сбрасываются в О, Работа синхронизируется одним тактовым импульсом Г с выхода узла Пуск-Останов 31.

Предположим, что U, равно 32 квантам и что в первом такте на вход прибора действует отрицательная импульсная помеха, а преобразование проводят в режиме с самокоррекцией. Тогда в первом такте, в результате выполнения в устройстве 26 сравнения операции вида Uy - V с (U„ - 18), на выходе устройства 26 сравнения формируется единичное значение сигнала

о/ 1 , При поступлении первого тактового сигнала Г 1 на первые входы элемента 36 запрета и первого элемента И 32, на выходе последнего форми-. руется единичный сигнал, который поступает на первый выход блока 27 управления. На втором и третьем выходах блока 27 управления в первом такте сохраняются нулевые сигналы. Единичным сигналом с выхода элемента И 8 сбрасываются с О шестые разряды регистров 14 и 15 и устанавливаются в 1 пятые разряды, В результате в первом регистре 14 устанавливается код 01 00 00, а во втором регистре 15 - код 010000. Во втором такте действия помехи прекращаются и в устройстве 26 выполняется операция вида

и, 7, (Uo 12).

Единичным сигналом по первому

входу блока 27 управления и вторым тактовым сигналом Г 2 открывается элемент 36 запрета. Так как триггер 39 установлен в 1, а на выходе элемента 24 ИЛИ-НЕ сохраняется единичный потенциал, то по единичному сигналу с элемента 37 задержки через элемент ИЛИ 38 на втором выходе блока 27 формируется импульс, которым четвертые разряды с выхода элемента И 12 устанавливаются в 1. На первом, втором и третьем входах элемента И 19 появляются единичные потенциалы, а на выходе элемента ИЛИ-НЕ 24

5I3

по соответствующему входу устанавливается нулевой потенциал, блокирующий по третьему входу элемент И 33.

Одновременно с этим на выходе устройства 26 вырабатывается сигнал

о О, как результат операции и / (Up 18). Единичным сигналом с выхода элемента 36 запрета по тактовому сигналу Г 3 через элемент ,37 задержки на вьсходе элемента И 35 фор мируется единичный сигнал коррекции. Единичным сигналом с третьего выхода блока 27 стробируется элемент И 23 и шестые разряды регистров устанавливаются в 1, а пятый и четвертый

разряды первого регистра и четвертый разряд второго регистра устанавливаются в О. Результат операции и / (Uo 18) в четвертом такте будет of О и по сигналу Г 4, по ука- занным правилам, на втором выходе блока.27 формируется единичный сигнал, которым по выходу элемента И 13 в первом и втором регистрах памяти устанавливаются коды 11 00 00 и 010000 соответственно. В пятом такте по результату операции 30) формируется сигнал |У 0.

Единичным сигналом с второго выхода блока 27 через элемент И 12 сбрасывается в О пятый р азряд второго регистра и устанавливаются в 1 четвертые разряды регистров 14 и 15. В шестом такте сигналом с выхода элемента И 6 (операция (,, .0/ I) . Аналогичным образом сбрасываются в О четвертые разряды регистров 14 и 15 и устанавливаются в 1 третьи разряды,

В седьмом такте, аналогично шее- тому (операция , о/ I), третий и четвертый разряды регистра 14 единичным сигналом с выхода элемента 5 И сбрасьгоаются в О, вторые разряды регистров 14 и 13 устанавлива- ются в 1. В этом случае в восьмом такте выполняется операция U.7/(U(, 32) и формируется сигнал с О на выходе устройства 26.

В результате в первом регистре 14 единичным сигналом с выхода элемен- та И 9 будет установлен код 11 OO l 1 а во втором регистре 15 - код 000001 В последнем, девятом такте в устройстве 26 выполняется операция Ux (Ue 33), что соответствует il , С выхода элемента 3 первый разряд регистра 14 сбрасьшается в

5

0 5

0 5

0 5

0 5

66

О, а единичным сигналом с прямого выхода первого разряда регистра 15 через элемент 1 задержки останавливается устройство Пуск-Останов 31.

Если в данном примере предположить, что в четвертом такте на входные цепи прибора действует вторая импульсная помеха, причем U - U, тогда в пятомр шестом и седьмом тактах в первом и втором регистрах установлены соответственно коды 10 и 000010. В седьмом такте на выходе элемента И 18 появляется единичный сигнал, а на выходе элемента ИЛИ-НЕ 24 - нулевой. В результате единич- . ным сигналом с третьего выхода блока 27 управления стробируется элемент И 22 и содержимое первого и второго регистров 14 и 15 корректируется соответственно 11 00 00 и 010000.

По аналогии можно рассмотреть случай, когда за цикл преобразования возникают многократные помехи. При этом возможен вариант, когда ошибка не может быть исправлена (например, отказ одного или нескольких элементов устройства). Тогда анализ сигналов на шинах ошибки j,k служит основанием для автоматического и оперативного перевода работы устройства из режима с самокоррекцией в режим с самоконтролем.

В этом случае устройство работает следующим образом.

При подаче единичного сигнала по шине 28 триггер 39 устанавливается в нулевое состояние, тем самым блокируется выработка сигнала опроса схемы коррекции (элементы И 21-23) на элементе И 35 (третий выход блока 27). Одновременно устройство Пуск-Останов 31 переключается на более высокую (предельную) частоту следования тактовых импульсов. Блокируется по первому входу элемент И 33. Работа устройства в этом случае ничем не отличается от приведенной для случая, когда на третьем выходе блока 27 сохраняется нулевой потенциал и происходит в соответствии с известным алгоритмом поразрядное уравновешивание.

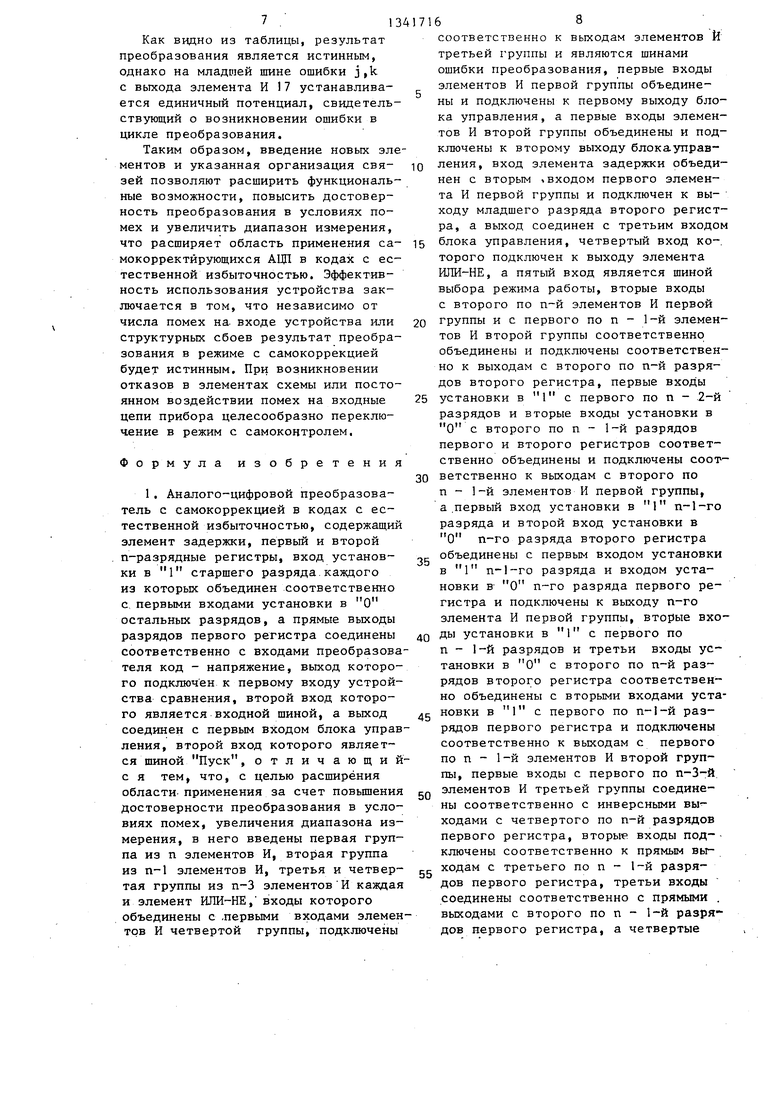

Пусть, например, Uy 27. Алгоритм работы для этого случая в режиме с самоконтролем представлен в виде таблицы.

7 . 1

Как видно из таблицы, результат преобразования является истинным, однако на младшей шине ошибки j,k с выхода элемента И 17 устанавливается единичный потенциал, свидетельствующий о возникновении ошибки в цикле преобразования.

Таким образом, введение новых элементов и указанная организация свя- зей позволяют расширить функциональные возможности, повысить достоверность преобразования в условиях помех и увеличить диапазон измерения, что расширяет область применения са- мокорректйрующихся АЦП в кодах с естественной избыточностью. Эффективность использования устройства заключается в том, что независимо от числа помех на входе устройства или структурных сбоев результат преобразования в режиме с самокоррекцией будет истинным. При возникновении отказов в элементах схемы или постоянном воздействии помех на входные цепи прибора целесообразно переключение в режим с самоконтролем.

Формула изобретения

1. Аналого-цифровой преобразователь с самокоррекцией в кодах с естественной избыточностью, содержащий элемент задержки, первьш и второй п-разрядные регистры, вход установ- ки в 1 старшего разряда.каждого из которых объединен соответственно с, первыми входами установки в О остальных разрядов, а прямые выходы разрядов первого регистра соединены соответственно с входами преобразователя код - напряжение, выход которого подключен к первому входу устройства сравнения, второй вход которого является входной шиной, а выход соединен с первым входом блока управления, второй вход которого является шиной Пуск , отличающий- с я тем, что, с целью расширения области- применения за счет повьш1ения достоверности преобразования в условиях помех, увеличения диапазона измерения, в него введены первая группа из п элементов И, вторая группа из п-1 элементов И, третья и четвер- тая группы из п-3 элементов И каждая и элемент ИЛИ-НЕ, входы которого объединены с .первыми входами элементов И четвертой группы, подключены

5 0 5

0

5 0 5 Q g

68

соответственно к выходам элементов И третьей группы и являются шинами ошибки преобразования, первые входы элементов И первой группы объединены и подключены к первому выходу блока управления, а первые входы элементов И второй группы объединены и подключены к второму выходу блок а управления, вход элемента задержки объединен с вторым входом первого элемента И первой группы и подключен к выходу младшего разрада второго регистра, а выход соединен с третьим входом блока управления, четвертый вход ко-, торого подключен к выходу элемента ИЛИ-НЕ, а пятый вход является шиной выбора режима работы, вторые входы с второго по п-й элементов И первой группы и с первого по и - 1-й элементов И второй группы соответственно объединены и подключены соответственно к выходам с второго по п-й разрядов второго регистра, первые входы установки в 1 с первого по п - 2-й разрядов и вторые входы установки в О с второго по п - 1-й разрядов первого и второго регистров соответственно объединены и подключены соответственно к выходам с второго по п - 1-й элементов И первой группы, а .первый вход установки в I п-1-го разряда и второй вход установки в О п-го разряда второго регистра объединены с первым входом установки в 1 П-1-ГО разряда и входом установки в О п-го разряда первого регистра и подключены к выходу п-го элемента И первой группы, вторые входы установки в 1 с первого по п - I-и разрядов и третьи входы установки в О с второго по п-й разрядов второго регистра соответственно объединены с вторыми входами установки в 1 с первого по п-1-и разрядов первого регистра и подключены соответственно к выходам с первого по п - 1-й элементов И второй группы, первые входы с первого по n-3-й элементов И третьей группы соединены соответственно с инверсными вы ходами с четвертого по п-й разрядов первого регистра, вторые входы под-- ключены соответственно к прямым выходам с третьего по п - 1-й разрядов первого регистра, третьи входы соединены соответственно с прямыми . выходами с второго по п - 1-й разря дов первого регистра, а четвертые

13

входы соответствующих четных элементов И третьей группы подключены к прямым выходам соответствукядих четных разрядов первого .регистра,третьи входы установки в 1 четных разря- дов, кроме п-го, начиная с четвертого, первого и второго регистров объединены соответственно с четвертыми входами установки в О соответствую щих четных разрядов, начиная с второго, второго регистра, с третьими входами установки в О соответствующих четных разрядов, начиная с второго,и с третьими входами установ- ки в О соответствующих нечетных разрядов, начиная с третьего, первого регистра и подключены соответственно к выходам соответствующих нечетных элементов И, начиная с перво- го, кроме п - , четвертой группы, причем второй вход установки в 1 п-го разряда и четвертый вход установки в О п - 2-го разряда второго регистра объединены с вторым входом установки в 1 п-го разряда, с третьими входами установки в О П-1-ГО и п - 2-го разрядов первого регистра и подключены к выходу п-З-го элемента И четвертой группы, при этом третьи входы установки в 1 i + 3-х разрядов кроме п-гго (где , .., (п - 1), первого и второго регистров объединены соответственно с пятыми входами установки в

О

1-х разрядов второго регистра, с четвертыми входами установки в О i-ro, i + 1-го и i+2-го разрядов первого регистра и подключены к выходу i-ro четного элемента И четвертой группы, а выход первого элемента И первой группы соединен с вторым входом установки в О первого разряда первого регистра,

2, Преобразователь по п.1, о т - л И чающийся тем, что блок управления выполнен на узле Пуск-Останов, с первого по четвертый элементах И, элементе запрета, элементе .задержки, элементе ИЛИ, триггере и

переключателе режима работы, управ

Q 5 0 5 о

5

о

g

0

1610

ляющий вход которого является пятым входом блока управления, первый и второй выходы соединены соответст- венно с входами установки в 1 и в О триггера, а информационный-вход объединен с первым входом узла Пуск- Останов и является вторым входом блока управления, третьим входом которого является второй вход узла Пуск-Останов, третий вход которого объединен с первыми входами второго и четвертого элементов И и под ключен к прямому выходу триггера, инверсный выход которого соединен с первым входом третьего элемента И, выход которого соединен с первым входом элемента ИЛИ, выход которого является вторым выходом блока управления, а второй вход соединен с выходом второго элемента И, второй вход которого объединен с вторьт входом четвертого элемента И и подключен к выходу элемента задержки, вход которого объединен с вторым входом третьего элемента И и соединен с выходом элемента запрета, информационный вход которого объединен с первым входом первого элемента И и подключен к выходу узла Пуск-Останов, а управляющий вход объединен с вторым входо м первого элемента И и является первым входом блока управления, первым выходом которого является выход первого элемента И,третьим выходом - выход четвертого элемента И, а четвертым входом - третий

вход второго элемента И. , .

1

3. Преобразователь по п.2, о т - личающийся тем, что узел Пуск-Останов выполнен на триггере, элементе И и генераторе импульсов, управляющий вход которого является третьим входом узла, а выход соединен с первым входом элемента И, выход которого является выходом узла, , а второй вход подключен к выходу триггера, входы установки в 1 и в О которого являются соответственно первым и вторым входами узла.

Pt/e.;

фие, 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь в кодах с естественной избыточностью | 1986 |

|

SU1381698A1 |

| Аналого-цифровой преобразователь с самокоррекцией в кодах с естественной избыточностью | 1986 |

|

SU1381703A1 |

| Сигнатурный анализатор для поиска перемежающихся неисправностей | 1986 |

|

SU1495799A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Генератор псевдослучайных чисел | 1985 |

|

SU1272484A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1522400A1 |

| Вероятностный преобразователь аналог-код | 1986 |

|

SU1363461A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1388989A2 |

| Система отладки микропроцессорных устройств | 1989 |

|

SU1700559A1 |

| Параллельно-последовательный п-разрядный аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1732471A1 |

Изобретение относится к электроизмерительной технике и может быть использовано при создании помехоустойчивых аналого-цифровых преобразователей. В устройство, содержащее элемент задержки, регистры, преобразователь код-напряжение, устройство сравнения, блок управления, с целью расширения области применения за счет повышения достоверности преобразования в условиях помех, увеличения диапазона измерения и расширения функциональных возможностей, введены с первой по четвертую группы элементов И, элемент ИЛИ-НЕ, шины ошибки преобразования и установки режима работы, 2 З.П..Ф-ЛЫ, 4 ил., 1 табл; § (Л с оо 4 VM k OS

J8 16 15фие.З

Редактор И.Касарда

Составитель Ю.Спиридонов Техред М. Ходанич

Заказ 4444/56Тираж 90 Подписное

ВНИШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Корректор С.Шекмар

| Аналого-цифровой преобразователь с самоконтролем | 1980 |

|

SU930657A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Браткевич В.В., Помехоустойчивый аналого-цифровой преобразователь | |||

| Автоматика и вычислительная техника, 1978, № 1, с | |||

| Способ приготовления сернистого красителя защитного цвета | 1915 |

|

SU63A1 |

Авторы

Даты

1987-09-30—Публикация

1986-04-18—Подача