1

Изобретение относится к области вычислительной техники и может быть использовано при построении ЦВМ повьпиенной надежности.

Известен контролируемый п-разрядный сумматор, содержащий в цепи контроля разряда два пороговых элемента (ПЭ) и логические элементы И, ИЛИ и НЕ ll Недостатком этого контролируемого сумматора являются значительные аппаратурные затраты, так как каждый двоичный разряд контролируется в отдельности, а также невысокое быстродействие из-за использования многоуровневой логики.

Наиболее близким техническим решением к изобретению является десятичный сумматор с контролем,кдждый разряд которого содержит четырехразрядный двоичный суммаГор, две схемы для формирования переноса, блок для коррекции суммы, сумматор по модулю 2, объединяющий выходы схем для формирования переноса, две четь1рех-вхоловые схемы нечетности для определения четности кодов входных операндов, семивходовую схему нечетности для определения четности нескорректированной суммы и шестивходовую схему нечетности с контрольным выходом 2. Десятичный сумматор контролируется с помощью предсказания четности для скорректированной суммы и сравнения ее с действительной четностью полученной суммы. Дублирование схемы для формирования переноса производится для того, чтобы неисправности при ее работе не вызывали необнаружи10ваемых ошибок.

Недостатком известного десятичного сумматора с контролем являются значительные аппаратурные затраты, а также невозможность обнаружения

15 многократных ошибок, когда четность ошибочного результата совпадает с четностью истинного результата.

Целью изобретения являются уменьшение аппаратурных затрат и улучшение контроля за счет обнаружения

20 двоичных ошибок.

Поставленная цель достигается тем, что в контроли Ьуемый двоичнодесятичный сумматор, содержащий

25 п двоично-десятичных тетрад, входы операндов каждой тетрады соединены с группой входов устройства, выход переноса каждой i-и тетрады соединен со входом переноса (Ч-1)-й тетрады введен элемент ИЛИ, выход

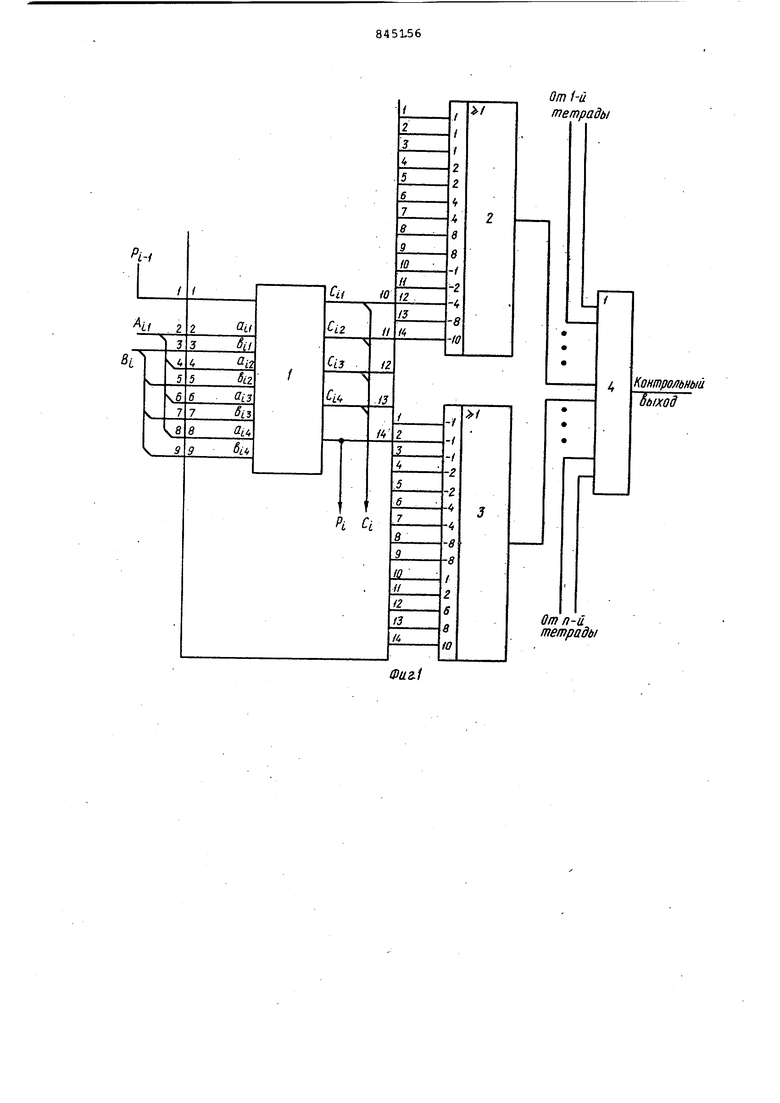

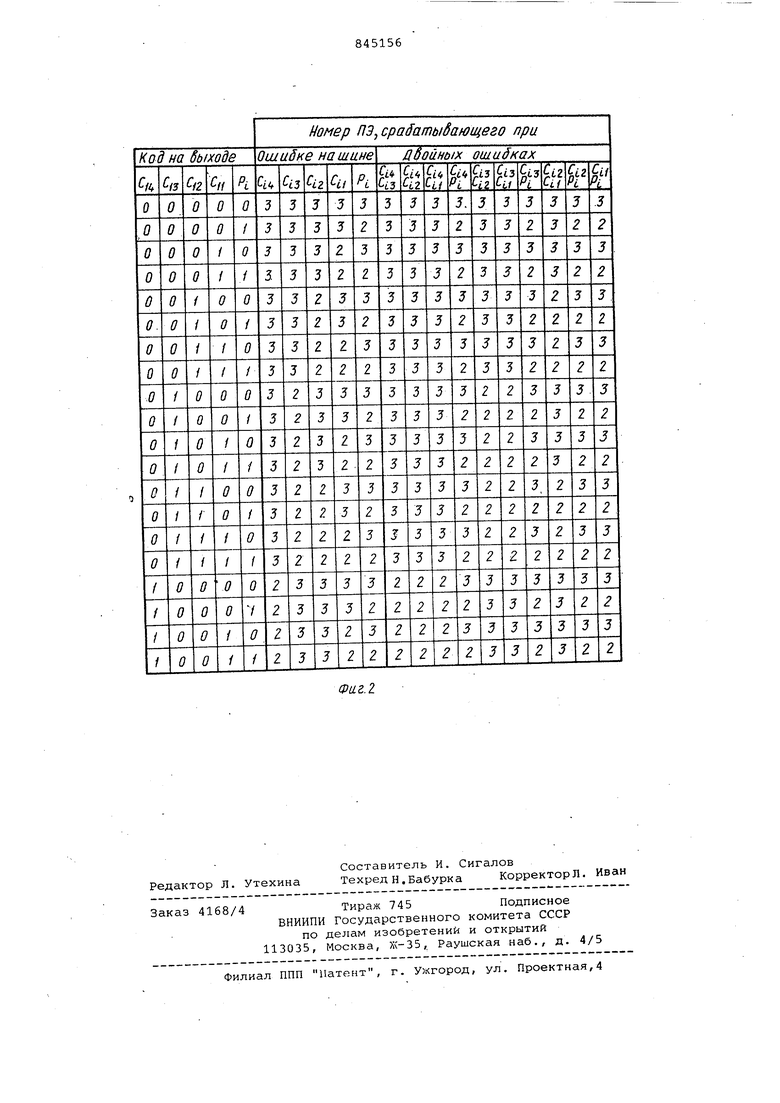

30 которого является выходом сумматора, а в каждую двоично-десятичную тетраду сумматора дополнительно введены два пороговых элемента с порогом 1. Выходы всех пороговых элементов с порогом 1 соединены с соответствующим входом элемента ИЛИ Входы операндов первого, второго, третьего и четвертого разрядов калсдой тетрады соединены с первыми и вторыми входами первого пороговог элемента с весами, равными соответственно 1,2,4 и 8 и с первыми и вторыми входами второго порогового элемента с весами, равными соответственно -1,-2,4 и -8. Выходы сумм первого, второго, третьс1.-о и четвер того разрядов каждой тетрады соединены с первыми и вторыми входами первого порогового элемента с весами, равными соответственно -1,-2 -4, и -8 и с первьами и вторыми входами 1,2,4 и 8. Вход переноса из предыдущей тетрады соединен с треть им входом первого порогового элемсн la с весом 1 и с третьим входом второго порогового элемента с весом -1. Выход переноса каждой тетрады соединен с первыми входами пер вого и второго пороговых элементов, веса которых соответственно равны 1 и -10. На фиг. 1 изображена функциональ ная схема i-и тетрады двоично-десят ного сумматора, на фиг, 2 - работа схемы контроля одной тетрады. Каждая i-я тетрада двоично-десятичного сумматора содержит четырехразрядный двоичный сумматор 1, первый 2 и второй 3 пороговые элементы Весы входов порогового элемента 2 равны +1,+,+,+2,+2,+4,+4,+8,+8,-1 -2,-4,-8, и -10. Входы его с весами +1 соединены со входами операндов первого (младшего) разряда а и и входом переносаР- i-й тетрады, входы с весом +2 соединены со входами операндов второго разряда а. и , входы с весом +4 - .со входами операндов третьего разряда а и , входы с весом +8 - со входами операндов четвертого разряда и Ь а входы с весами -1,-2,-4,-3 и - 1 подключены соответственно к выходам суммы первого (младшего) разряда С; , второго разряда с, третьего разряда с, четвертого разрядаС, и к выходу переноса Р,- i-й тетрады Веса входов второго порогового элемента 3 равны -1,-1,-1 ,-2 ,-2, -4,-4,-8,-8,+1,+2,+4,+8,+10. Входы его с весом -1 соединены со входам операндов младшего разряда а и Ц и входом переноса Р,- 1-и тетрады, входы с весом -2 соединены со вход операндов второго разряда a,,-, b входы с весом -4 - со входами операндов третьего разряда а и ,, Ехоль- с весом 8 - со входами one рандов четвертого разряда а и Ьу , а входы с весами +1,+2,+4,+8 и +10 одключены соответственно к выходам уммы первого (младшего) разряда ,- второго разряда с,-,. , третьего разряда , четвертого разряда ск выходу переноса R; i -и тетрады. Выходы первого и второго пороговых элементов 2 и 3 всех тетрад соединены со входами многовходового элемента ИЛИ 4, выход которого является выходом двоично-десятичного сумматора. Устройство работает следующим образом. входы пороговых элементов 2 и 3 подключены таким образом, что при появлении ошибки на выходах суммы или переноса i-й тетрады сумма входных сигналов одного из пороговых элементов 2 и 3 превышает его порог, в результате чего на выходе этого порогового элемента появится единичный сигнал, вызывающий сигнал ошибки на контрольном выходе сумматора. В приведенной таблице указаны все возможные единичные и двойные ошибки сумматора и соответствующий пороговый элемент, обнаруживающий конкретную ошибку. В данном сумматоре схема контроля Обнаруживает все единичные и двойные ошибки, а также большинство к-кратных ошибок, где к з-3 . Работа i -и тетрады двоично-десятичного сумматора при отсутствии ошибок описывается равенством A. + B,-p.. , о; где А и В операнды I-и тетрады ; Cj - суглма-; - перенос из младшей I I -1) -и тетрады Р- - перенос, получающийся в 1-1 тетраде. Учитывая, что в ДЦС применяется двоично-десятичный код 8,4,2,1, равенство (1) эквивалентно следующим равенствам: SV ai5 ia --i V V2 ici M PiH 8с.,.Ис..Ор., (а) б(с 14Ч4 + -1з 1э)2(а,+Ц.)1(а,+) 1f,.-c. (3) Отсюда следуют неравенств.; ,)+4(d,.jtb.)2(q-,fa,..)a,-/bi,) + 1р..- 8Цд+4С у2С-.,2;Ю.,1 , (4.1J вCa,,,)n(,)н(a.+fc. Pi-r C-r4 S- 2 i-/ ii PiJ -1. (--i), которые равносильны следующим неравенствам: а(,2()мЦ/1г,1р-., -«C,-4-4c..-Yc.p.i, (f.i) -sCH i ),-,V2 (,i)-i(i,,)-f Pi. - Очевидно, .что выполнение неравенства 5.1 контролируется первым пороговым элементом ,2, а выполнени неравенства 5.2 - вторым пороговым элементом 3. При ложном появлении кода О вместо 1 на одном из вы ходов сумматора 1 левая часть неравенства 5.1 становится равной или больше 1, что вызывает срабатывание порогового элемента 2. При ложном появлении кода 1 вместо. О нарушается неравенство 5.2, что приводит к срабатыванию п рогового элемента 3. Для доказательства утверждения, что обнаруживаются все двойные ошибки, рассмотрим выражение,описы вающее состояния выходных шин СУМматора 1 8с. 4с; 2с. 10, Юр. (6 При одновременном ложном появле НИИ на двух выходных шинах кода О вместо 1 или 1 вместо О значение выражения (6) соответственно уменьшится или увеличится на величину (и + v), где U и V - веса шин с ложным кодом, т.е. и 1,2,4,8,1 V 1, 2 , 4 , 8 ,10 ; U V . Это приводит к нарушению равенства (3) , а следовательно, и одног из неравенств (5.1) (5.2), что вызо вет сигнал ошибки. При ложном появл нии кода О вместо 1 на одной вы ходной шине и появлении 1 вместо О на другой, значение выражения (6) изменится на величину lu-v), где U и V - веса шин с ложным кодом. Поскольку U V 1различные шины имеют разные веса), то всегда т.е. любая двойная ошибка изменит значение выражения (б) и вызовет срабатывание одного из пороговых элементов 2 и 3. Схема контроля обнаруживает такж большинство многократных ошибок,т.е таких, для которых сумгдарное изменение кодов с учетом весов отлично от О. Д.ПЯ примера рассмотрим работу сумгиатора 1 на входном наборе А; 1001, В; 0101 и Р 0. Пр правильной работе-на шинах суммы бу дет записано число с 0100, а на не переноса р 1. Гфи появлении на шине р. сигнала О сумма входных кодов, подаваемых на пороговый элемент 2, равна 10, что превышает его порог срабатывания, и на выходе первого порогового элемента 2 появится сигнал ошибки. При одновремен ном ложном появлении кода 1 на шинах с , Cj,j и с;, и кода О :ia шине сумм.: кодов, подаваемых на первый пороговый элемент, больше порога срабатывания, что вызовет сигнал ошибки. Двойные ошибки Taioxe будут обнарух ены одним из пороговых элементов 2,3 (см.таблицуI. Сравним количество контрольного оборудования известного и данного сумматоров.. Известный сумматор содержит в цепи контроля одной тетрады 2 четырехвходовых, шестивходовую и семивходовую схемы нечетности, сумматор по модулю 2 (двухвходовая схема нечетности; 2 схемы типа И и схему ИЛИ, дублирующие схему формирования переноса. Минимальное количество двухвкодовых схем нечетности для построения вышеуказанных многовходовых схем нечетности равно: N 2(4-1)+(6-1)+(7-1) Количество схем ИЛИ-НЕ И-НЕ для реализации этих схем равно: L 18-4 -72 (см. Ф. Селлерс Методы обнаружения ошибок в работе ЭЦВМ, с. 74, фиг.4.7, с. 5, табл. 4.1). В данном сумматоре количество логических схем в цепи контроля одной тетрады равно 2 (два пороговых элемента). Известны пороговые элементы, построенные на основе одного транзистора и нескольких сопротивлений. Пороговые элементы, реализованн е таким образом, по сложности соизмеримы, например, с элементом ИЛИ-НЕ при одинаковом количестве входов. Проведем оценку по Квайну контрольного оборудования известного и данного сумматоров, учитывая вышеизложенные расчеты и примечания. Для известного сумматора общее количество входов контрольных логических схем в одной тетраде равно К.,.д 72.2 +2-2 +1- 2, Кизе 150. Для данного сумматора получаем Кд 214 28, где Кд - общее количество входов схем в цепи контроля одной тетрады. Кроме уменьшения аппаратурных затрат в данном двоично-десятичном сумматоре увеличивается быстродействие контрольного оборудования. Число логических уровней, через которые проходит сигнал от входа к выходу, в схеме контроля данного двоичного десятичного сумматора равно 2 (поро17Овый элемент,элемент ИЛИ) .

Число логических уровней схемы контроля известного сумматора равно

М Tlogo 4 +ltioga. 6J + + Tlog 7 + 1 2 + 3+3 + 1 9.

Таким образом, время выявления ошибок в данном сумматоре меньше по сравнению с известным.

Следует заметить такхе,что в известном сумматоре схема контроля подключается также и к внутренним точкам сумматора (ко входам схемы коррекции), что не позволяет контролировать таким способом сумматоры в интегральном исполнении, не имеющие выводов внутренних точек.

В данном сумматоре схема контроля подключается только ко входам и выходам сумматора, что дает возможность контролировать предложенным способом десятичные сумматоры всех

типов.

I

Фор(Мула изобретения

Контролируемый двоично-десятичный сумматор, содержащий п двоично-десятичных тетрад,входы операндов каждой тетрады соединены с группой входов устройства, выход переноса каждо i-и тетрады соединен со входом переноса и+1)-й тетрады, отличаю д и и и ,я тем, что, с целью уменьшения аппаратурных затрат, в сумматор введен элемент ИЛИ, выход которого является выходом сумматора, а в каждую двоично-десятичную тетраду

сумматора дополнительно введены два пороговых элемента с порогом 1, причем выходы всех пороговых элементов с порогом 1 соединены с соответствующим входом элемента ИЛИ, входы one-. е рандов первого, второго, третьего и четвертого разрядов каждой тетрецда соединены с первыми и вторыми входами первого порогового элемента с весами, равными соответственно 1,2,4 и 8 и

Q с первыми и вторыми входами второго порогового элемента с весами, равными соответственно -1,-2,-4 и -8, выходы сумм первого, второго, третьего и четвертого разрядов каждой тетрады соединены с первыми и вторыми входами

5 первого порогового элемента с весами, равными соответственно -1,-2,-4,-8 и с первыми и вторыми входами второго порогового элемента с весгхми, равными соответственно 1,2,4 и 8, вход

0 переноса из предыдущей тетрады соединен с третьим входом первого порогового элемента с весом 1 и с третьим входом второго порогового элемента с весом 1, выход переноса каждой

5 тетрады соединен с первьдми входами пороговых элементов, веса которых соответственно равным - 10 и 10.

Источники информации, rj принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 500527, G Об F 11/00, 1976.

2.Селлерс Ф. Методы обнаружения ошибок в работе ЭЦВМ. М., Мир, 1972, с. 141, фиг.7.13 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования фибоначчиево-десятичных кодов | 1981 |

|

SU945862A1 |

| Суммирующее устройство с контролем | 1983 |

|

SU1140112A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| Двоично-десятичный сумматор | 1985 |

|

SU1305664A1 |

| Устройство для умножения двоично-десятичных цифр | 1983 |

|

SU1198513A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1285604A1 |

| Операционный модуль | 1984 |

|

SU1406592A1 |

| Устройство для сложения п-разрядныхдЕСяТичНыХ чиСЕл | 1979 |

|

SU824203A1 |

Авторы

Даты

1981-07-07—Публикация

1979-07-17—Подача